Fターム[5J098AA14]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コンデンサ (333)

Fターム[5J098AA14]の下位に属するFターム

可変コンデンサ (54)

Fターム[5J098AA14]に分類される特許

201 - 220 / 279

OTA出力振幅低減回路

【課題】ダイナミックレンジを広くとれるOTAを構成要素としたGm−Cフィルタを提供する。

【解決手段】上記課題を解決するために、複数の演算相互トランスコンダクタンス増幅器とキャパシタとで構成する等価インダクタ回路を有するGm−Cフィルタにおいて、該等価インダクタ回路の入力側に接続される回路のインピーダンスであって、該等価インダクタ回路から見たインピーダンスである第1のインピーダンスが、前記等価インダクタ回路の出力側に接続される回路のインピーダンスであって、該等価インダクタ回路から見たインピーダンスである第2のインピーダンスと同程度に小さくする。

(もっと読む)

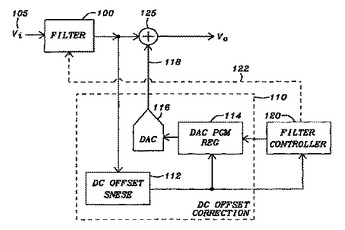

高利得複素フィルタのためのDCオフセット補正

複素フィルタ回路のフィルタ段の出力のDCオフセット電圧の補正を提供するDC電圧オフセット補正回路は、フィルタ段の出力においてDCオフセット電圧の存在を示すオフセット存在信号を生成するために複素フィルタのフィルタ段の出力に接続される、DCオフセット検出装置を含んでいる。ディジタル−アナログ変換器は、オフセット存在信号という条件付きの出力に補償信号を加える。プログラミング・レジスタは、フィルタ段の出力に補償電圧を加えることをディジタル・アナログ変換器にさせるようにディジタル信号を生成する二分探索を行なうためにオフセット存在信号を受け取る。フィルタ・コントローラは、フィルタ段のプログラムされた利得値に適合させるように、プログラミング・レジスタに補償電圧レベルをセットする。  (もっと読む)

(もっと読む)

アクティブインダクタンス回路、フィルタ回路及び受信回路

【課題】 低電源電圧状態での歪特定を改善して動作を安定化でき、設計の自由度を向上し得るようなアクティブインダクタンス回路を提供する。

【解決手段】 正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量(コンデンサ108)を付加することにより形成した差動型の90度移相器130と、入力信号を電流に変換して上記90度移相器130に電流を流し込む第1の差動対回路140と、上記90度移相器130の出力電圧を電流に変換して入力側に戻す第2の差動対回路150とを有して構成され、上記90度移相器130の入力側からみたインピーダンスを2端子のインダクタンスとして作用させる。

(もっと読む)

トランスコンダクタ、積分器及びフィルタ回路

【課題】完全差動型のトランスコンダクタについて、差動出力の同相動作点を安定させ、さらに、消費電力及びチップ面積を低減し、ノイズ特性を向上する。

【解決手段】差動電圧信号を受け、差動電流信号を出力するトランスコンダクタとして、差動電圧信号を受け、シングルエンドの電流信号を出力する二つのトランスコンダクタ(10+、10-)を備えたものとする。ここで、二つのトランスコンダクタ(10+、10-)の一方の反転入力端と他方の非反転入力端とは互いに接続されている。本トランスコンダクタは、二つのトランスコンダクタ(10+、10-)のそれぞれから出力された電流信号を差動電流信号として出力する。

(もっと読む)

能動フィルタ回路

【課題】回路規模を増大させることなく、フィルタ回路を所望の特性に安定化させる

【解決手段】能動フィルタ部14は、電流制御部30と、第1Gm−Cフィルタ部32と、後段回路34と、を含む。電流制御部30は、中央制御部20から出力された信号を入力として、第1Gm−Cフィルタ部32に対し、それぞれのトランスコンダクタンスアンプに対応した、Gm値を調整するための調整電流を出力する。後段回路34は、トランスコンダクタンスアンプなどの能動素子によって構成される負荷容量を含む。第1Gm−Cフィルタ部32は、複数のトランスコンダクタンスアンプと、トランスコンダクタンスアンプのGm値を制御する制御部とから構成され、第1フィルタ信号選択部12から出力された信号の帯域を制限して後段回路34に出力する。

(もっと読む)

能動フィルタ回路、フィルタ調整方法、および、それらを用いた通信装置

【課題】回路規模を増大させることなく、フィルタ回路を所望の特性に安定化させる

【解決手段】能動フィルタ部14は、電流制御部30と、第1Gm−Cフィルタ部32と、後段回路34と、を含む。電流制御部30は、中央制御部20から出力された信号を入力として、第1Gm−Cフィルタ部32に対し、それぞれのトランスコンダクタンスアンプに対応した、Gm値を調整するための調整電流を出力する。後段回路34は、トランスコンダクタンスアンプなどの能動素子によって構成される負荷容量を含む。第1Gm−Cフィルタ部32は、複数のトランスコンダクタンスアンプと、トランスコンダクタンスアンプのGm値を制御する制御部とから構成され、第1フィルタ信号選択部12から出力された信号の帯域を制限して後段回路34に出力する。

(もっと読む)

高性能ADSL回線コンディショナシステムおよび方法

DSL回線コンディショナは、現在利用可能なものより実質的により長い距離に渡って、標準の電話ツイストペア回線(102、104、106、108)上においてビデオ、音声、およびデータの信号を同時にサポートする十分に高い性能を達成する。回線コンディショナ(100)は、それが用いられるツイストペア回線によって上り信号および下り信号に課される実際の劣化に従って、上りプリアンプ(112)および下りプリアンプ(122)のゲインおよび減衰を自動的に調整およびセットする。回線コンディショナは、DSL信号の信号対雑音比および信号品質を最適化することによって高い性能を達成し、回線コンディショナが用いられるツイストペア回線からの給電によって動作し得る低い電力消費性を有する。  (もっと読む)

(もっと読む)

共振回路

本発明の実施形態は共振回路に関し、特に、広い周波数範囲に応答するRFID(radio frequency identification)における共振回路に関するが、これに限定しない。可制御電気共振器は、共振回路を構成するために第1キャパシタに結合されたインダクタを備え、前記可制御電気共振器は、可制御素子と、前記可制御素子によって前記第1キャパシタの一端から他端に制御可能に結合される第2キャパシタと、前記第1および第2キャパシタの合計の実効静電容量が前記可制御電気共振器における振動信号のデューティサイクルによって変化するように前記可制御素子を制御する制御装置とをさらに備える。  (もっと読む)

(もっと読む)

フィルタ回路、及び受信回路

【課題】比較的大きな時定数を持ち、フィルタ特性が可変可能で、且つ、LSI化が可能なフィルタ回路の実現。

【解決手段】フィルタ回路10は、LPFであり、抵抗R1及びコンデンサC1によりRCフィルタ(LPF)が形成されているとともに、抵抗R1の入力側にスイッチSW1が直列接続されている。スイッチSW1は、所定周期のパルス信号である制御電圧によってそのオン/オフが制御される。そして、フィルタ回路10の時定数は制御電圧のデューティによって可変され、この制御電圧のデューティが小さくなるに従ってフィルタ回路10の時定数は小さくなる。

(もっと読む)

RC濾波器の遮断周波数の可変方法

【課題】 抵抗とコンデンサーで構成される低域通過濾波器、高域通過濾波器及び全域通過濾波器において、抵抗とコンデンサーの値を変えることなく、その遮断周波数を変えることを可能とした低域通過濾波器、高域通過濾波器及び全域通過濾波器を提供する。

【解決手段】 低域通過濾波器、高域通過濾波器及び全域通過濾波器を構成する抵抗とコンデンサーに流れる信号電流の比を変えることにより実現する。

(もっと読む)

フィルタ調整方法及びフィルタ調整装置並びにフィルタ回路

【課題】アナログフィルタの特性を調整するためのフィルタ調整方法及びフィルタ調整装置並びにフィルタ回路に関し、簡単な構成で自動調整が行なえるフィルタ調整方法及びフィルタ調整装置並びにフィルタ回路を提供することを目的とする。

【解決手段】本発明は、アナログフィルタ(111)の特性を調整するフィルタ調整方法において、アナログフィルタ(111)に擬似ランダムビットパターンを供給し、アナログフィルタ(111)の出力と擬似ランダムパターンとの相互相関値を算出し、算出した相互相関値に基づいてアナログフィルタの特性を調整することを特徴とする。

(もっと読む)

ボルテージレギュレータ

【課題】非常に長い間、出力電圧のオーバーシュートが生じる状況でも当該オーバーシュートを抑制可能とすると共に、容量の大きなコンデンサの付加を不要とし、省スペースを実現する。

【解決手段】誤差増幅器を具備したボルテージレギュレータに、出力電圧のオーバーシュートを検出する第1の手段(誤差増幅器(2)1a)と、出力電圧のオーバーシュートを検出している間、誤差増幅器に流す電流を増加させる第2の手段(PチャネルトランジスタM19、NチャネルトランジスタM12)とを設ける。

(もっと読む)

イコライザ回路

【課題】構成が簡単で雑音が小さく、かつパラメータの調整が容易なイコライザ回路を提供すること。

【解決手段】イコライザ回路は、入力信号を増幅して出力する第1の増幅回路50、入力信号が印加されるフィルタ回路51、フィルタ回路51の出力信号が入力される第2の増幅回路52、第1の増幅回路50の出力信号と第2の増幅回路52の出力信号とを逆相で加算する加算回路53とを備える。フィルタ回路51と第2の増幅回路52の組を複数個備えていてもよい。更に、増幅回路の利得やフィルタ回路の特性を制御する等化特性設定回路54を備える。高精度あるいは低雑音の部品や素子が必要なく、回路構成が簡単である。また、回路が高域に敏感でなくなるので、低雑音化が図れる。更に、イコライザ回路の特性を連続的に変更可能である。

(もっと読む)

半導体メモリ装置及びメモリモジュール

【課題】外部から基準電圧を与える場合、動作クロック等に起因するノイズ成分を確実に除去し誤動作を有効に防止可能な半導体メモリ装置等を提供する。

【解決手段】本発明の半導体メモリ装置は、基準電圧を与えるVREF信号を入力するVREF端子と、VREF端子に接続され、VREF信号のうち基準電圧の成分を通過させるとともに不要な高周波成分を除去するローパスフィルタ10と、ローパスフィルタ10の出力と論理レベルの判定対象のDQ0〜DQn−1信号が接続される入力初段回路A0〜An−1とを備え、ローパスフィルタ10は少なくとも動作クロックの周波数において所定の減衰量を有している。

(もっと読む)

PLL回路におけるアクティブフィルタ。

【課題】 PLL回路の内部のローパスフィルタを構成する回路素子、特に静電容量の値を小さくすることによって、ローパスフィルタをチップに内蔵化可能とする。

【解決手段】 位相比較器の後段に2つのチャージポンプ回路を備えるPLL回路内で用いられるアクティブフィルタが、一方のチャージポンプ回路の出力とアースとの間に接続される第1の回路要素と、他方のチャージポンプ回路の出力とアースとの間に接続される第2の回路要素と、第1、第2の回路要素のそれぞれの両端の電圧を加算する電圧加算器とを備える。

(もっと読む)

遅延回路及びそれを用いた映像信号処理回路

【課題】ドレイン・基板間の寄生容量を軽減させる。

【解決手段】充電用・放電用トランジスタとそれらのソースに接続された容量素子とを有したスイッチド・キャパシタ部を複数有し、入力信号が充電用トランジスタのドレイン各々に対して共通に入力され且つ容量素子を充電させるように接続されるとともに、放電用トランジスタのドレイン各々から容量素子を放電させて出力信号が出力されるように接続されるスイッチド・キャパシタ群と、充電用及び放電用トランジスタのゲート各々のオン・オフを制御して容量素子各々を入力信号に基づいて順次充電させるとともに、当該順次充電の際に前回充電しておいた容量素子を放電させることで出力信号を順次出力させるスイッチング制御部と、を有し、隣接する二つの前記スイッチド・キャパシタ部において、双方の充電用・放電用トランジスタ同士を隣接させ、双方の充電用・放電用トランジスタのドレインを共通させる。

(もっと読む)

超音波診断装置

【課題】 CWドプラ信号処理にも適用可能なダイナミックレンジを有し、かつ回路規模が小さい新方式のAD変換器を採用することにより、小型で低価格な超音波診断装置を提供すること。

【解決手段】 映像化モード及び使用する超音波プローブ11に応じて、制御式バンドパス型シグマ・デルタAD変換器154の中心周波数Fc、帯域幅Bw、ダイナミックレンジのそれぞれを共振器コントローラ16によって自由に制御する。これにより、一つの受信系によるオールモード対応の受信ビームフォーマを実現することができ、従来必要だったCWドプラモード専用アナログ信号処理回路を削除することができる。その結果、従来に比して小型且つ低価格な受信ビームフォーマ、及び超音波診断装置を実現することができる。

(もっと読む)

フィルタ回路

【課題】 スイッチの切り替え時に出力端子にノイズ電圧が発生しないようにすること。

【解決手段】 演算増幅器1の非反転入力端子+を演算増幅器11を用いたボルテージフォロアDの入力端子+に接続し、このボルテージフォロアDの出力端子を第2のスイッチSW2を介してコンデンサC2と第1のスイッチSW1と間に接続し、更に、VAの電位をボルテージフォロアDでバッファした電位をVA*として、第1のスイッチSW1と第2のスイッチSW2とが逆相の動作を行うように制御するスイッチ制御回路Eを接続して、フィルタ回路を構成する。

(もっと読む)

フィルタ回路

本発明は、フロントエンド無線受信機内に使用されるベースバンドフィルタの消費電力を削減し、かつ必要な線形性を提供するという要求に応えるものである。詳細には、従来よりも少ない消費電力で比較的高い線形性を得ることができる。これは、理想的な統一された直流利得の「複合」ソースフォロワ(CMOS素子を使用するとき)として動作する最適化された単分岐完全差動構造を使用する本発明の実施形態で達成される。ソースフォロワの内部の正帰還により、1つまたは2つの複素数極を合成することができる。  (もっと読む)

(もっと読む)

フィルタ回路、並びに、これを用いたイメージセンサ、イメージセンサモジュール、画像読取装置

【課題】フィルタ定数を高精度、広範囲に設定することができ、集積化規模の増大を抑制する事が可能なフィルタ回路と、これを用いたイメージセンサ及びモジュールを提供すること。

【解決手段】フィルタ回路AF1は、定電流源I1、I2とトランジスタP1、P2から成るカレントミラー部CM1とトランジスタN1、N2から成るカレントミラー部CM2と入力パルス信号をバッファする入力バッファBUF1とソースが電源に接続され、ドレインがP1、P2のゲートに接続され、ゲートがBUF1に接続されたトランジスタP3とソースが接地され、ドレインがN1、N2のゲートに接続され、ゲートがBUF1に接続されたトランジスタN3とCM1のミラー電流m1によって充電され、CM2のミラー電流m2によって放電されるコンデンサC1とC1の一端電圧Vcを出力パルス信号S1として出力する出力バッファBUFより成る。

(もっと読む)

201 - 220 / 279

[ Back to top ]