Fターム[5J098AA15]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | コンデンサ (333) | 可変コンデンサ (54)

Fターム[5J098AA15]に分類される特許

1 - 20 / 54

フィルタ回路及び受信装置

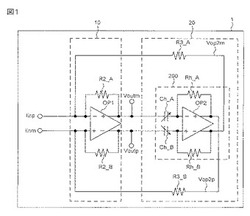

【課題】低雑音かつ低カットオフ周波数のフィルタ回路をより小面積で実現する。

【解決手段】フィルタ回路(1〜5)は、入力端子(Iinp、Iinm、(Vinp、Vinm))に供給された入力信号を受け、信号を増幅して出力端子(Voutm、Voutp)に出力する第1回路(10、11)と、第1容量素子(Ch_A、Ch_B)を介して前記第1回路の出力信号を入力する第1差動増幅回路(OP2)と、前記第1差動増幅回路(OP2)の入出力間に負帰還経路を形成する第1抵抗素子(Rh_A、Ch_B)と、前記第1差動増幅回路の出力と前記第1回路の入力との間に負帰還経路を形成する第2抵抗素子(R3_A、R3_B)とを有する。

(もっと読む)

フィルタ装置およびその制御方法

【課題】フィルタのノッチ周波数を調整する機能を持ったフィルタ装置を提供する。

【解決手段】入力信号を抵抗109と可変容量110、アクティブインダクタ111を備えたフィルタコア部102にて分圧し、フィルタコア部102のフィルタ特性信号Vfの振幅と基準振幅とを比較する振幅比較回路101、振幅比較回路101での比較結果に基づいてアクティブインダクタ111の位相を制御する位相制御部108、フィルタコア部102のフィルタ特性信号Vfの周波数と基準周波数とを比較する周波数比較回路103、周波数比較回路103の比較結果に基づいて可変容量110の容量を制御する可変容量制御部117によってフィルタ装置を構成し、アクティブインダクタ111の位相、可変容量11の容量が制御される間、アクティブインダクタ111の位相制御部108が、フィルタコア部102を発振させる。

(もっと読む)

受信装置及び多重フィルタの制御方法

【目的】受信強度に拘わらず高精度な復調を行うことが可能な受信装置及び多重フィルタの制御方法を提供することを目的とする。

【構成】送信信号を受信して得られた周波数信号に対して、夫々が異なる周波数特性を有する複数のフィルタが直列に接続されてなる多重フィルタによって周波数選択処理を施すにあたり、受信強度が所定の閾値受信強度よりも高い場合には、複数のフィルタの内の少なくとも1つのフィルタの中心周波数を偏倚させる。

(もっと読む)

オーディオ機器

【課題】入力端子に接続されたソース機器に合わせて入力インピーダンスやゲインを設定可能なオーディオ機器を提供する。

【解決手段】ホット端子およびコールド端子を有しソース機器が接続される入力端子と、インピーダンス素子と、キャパシタと、テスト信号発生部と、リターン信号解析部と、通常動作時にインピーダンス素子を入力端子に並列に接続し、ソース機器のインピーダンス検出時にコールド端子にテスト信号発生部を接続するとともにホット端子にキャパシタおよびリターン信号解説部を接続する切替スイッチとを備え、ソース機器のインピーダンス検出時に、テスト信号発生部はテスト信号を発生し、リターン信号解析部はホット端子に戻ってきたテスト信号であるリターン信号に基づいてソース機器のインピーダンスを検出する。

(もっと読む)

バンドパスフィルタ及びバンドパスフィルタのキャリブレーション方法

【課題】BPFを構成するOTAの個数を削減し,低消費電力で高次のバンドパスフィルタを提供する。

【解決手段】バンドパスフィルタは,入力信号が入力されるハイパスフィルタ(14)と,ハイパスフィルタの出力が反転入力端子に入力され,反転入力端子と非反転入力端子間の入力電圧を増幅して出力信号を出力端子に出力するアンプ(10)と,アンプの非反転出力端子と反転入力端子との間に接続された第1抵抗(R2)と,反転入力端子に第1端子が接続された第1キャパシタ(C2)と,アンプの非反転出力端子の出力信号の極性を反転し,当該反転した信号をキャパシタの第2端子に出力する反転アンプ(12)とを有する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

フィルタ装置および通過帯域特性調整方法

【課題】従来よりも少ない回路規模で、半導体で構成される受動素子により形成される通過帯域特性の調整機能を実現できるフィルタ装置および通過帯域特性調整方法を得ること。

【解決手段】通信装置の受信系で用いられるフィルタ装置8であって、半導体で構成される受動素子の組み合わせにより、入力される受信信号に対し通過帯域の制限を行うフィルタ回路4と、毎回の受信動作開始時に、当該受信系において前記フィルタ回路の後段に設けられている信号強度検出回路が検出した信号強度を利用して、前記フィルタ回路の周波数通過特性を、前記入力される受信信号を最大に出力できるように調整する制御回路9とを備えた。

(もっと読む)

フィルタ調整装置、電源制御システム、およびフィルタ調整方法、

【課題】位相比較を行わず、振幅検出結果に基づいてフィルタ特性のばらつきを高精度、かつ自動的に補償可能なフィルタ調整装置を提供すること。

【解決手段】実施形態によれば、フィルタ調整装置はフィルタと、基準信号生成部と、制御部と、振幅検出部と、調整部とを具備する。フィルタは特性制御信号に応じてフィルタ特性が制御される。基準信号生成部は振幅制御信号に応じた振幅の基準信号を生成し、フィルタに供給する。制御部は特性制御信号によりフィルタに異なるフィルタ特性を設定し、振幅制御信号により基準信号の振幅を異なる振幅に設定する。振幅検出部は特性制御信号によりフィルタに異なるフィルタ特性が設定される状態において、異なる振幅の基準信号に対するフィルタの出力信号の振幅を検出する。調整部は振幅検出部によって検出された複数の振幅に従い、フィルタ特性が所望の特性となる所望の特性制御信号を決定する。

(もっと読む)

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

電磁誘導型埋設物探査装置

【課題】デジタル信号処理装置(略称「DSP」)による電磁誘導型埋設物探査装置では、デジタル化時の量子化レベル等の制約によって十分な感度が得られず、非金属管路に収容される光ファイバーケーブルを、手軽な間接法によって検出することが難しかった。

【解決手段】本発明の水晶アクティブフィルタは中心周波数の調整機能と水晶振動子の破損防護機能を有しており、多段接続により超狭帯域かつ高DU比のフィルタを容易に構成することができ、高感度の電磁誘導型埋設物探査装置を実現することができる。これによって、非金属管に収容される光ファイバーケーブルを、間接法によって検出することが可能となる。

(もっと読む)

フィルタ較正

【課題】費用対効果が大きく、簡単であり、さらに正確な、フィルタを較正する方法を提供する。

【解決手段】フィルタ104、116は、較正中に発振器として再構成される。フィルタを再構成するために、スイッチおよび/または他の構成が使用されて、フィルタの負のフィードバックループに対して正のフィードバックループを再構成する。フィルタのコンポーネントを調整して、所望のフィルタ特性に対応する発振を達成するために発振パラメータが次に測定される。

(もっと読む)

再帰型フィルタ回路

【課題】再帰フィルタ回路のエミッタフォロア回路の数を低減し、回路規模が小さい再帰型フィルタ回路を提供する。

【解決手段】バイポーラトランジスタ(Tr)101を流れる電流Iinとフィードバック電流Ifbとを加算して電流Iを生成するノードB、電流Iをテール電流とし、ゲインを変更する制御信号が入力されるバイポーラTr106及びバイポーラTr103を含む差動対100、バイポーラTr106に流れる電流を電圧に変換する抵抗素子105を含む可変ゲイン増幅部、変換後の電圧を増幅して出力信号を生成するバイポーラTr113を含む出力部115、可変容量素子104を含むハイパス部、ハイパス部から出力された信号をバッファリングする回路114、バッファリングされた信号を、可変容量素子109を介して周波数帯域制限するローパス部を含む移相部によって再帰型フィルタを構成する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の中心周波数を調整する機能を備えたフィルタ回路を提供する。

【解決手段】入力信号とフィードバック信号(信号Vf)の加算信号を出力するカプラー109、加算信号を増幅した増幅信号を生成するAGC回路110、増幅信号の位相をシフトさせて信号Vfを生成する移相器111を備えたフィルタコア部102と、基準信号(信号Vr)を取得する基準信号生成部119、信号Vr、信号Vfの振幅を比較する振幅比較回路101、比較の結果に基づいてAGC回路110の増幅率を制御するゲイン制御電圧生成部108、信号Vrの位相と信号Vfの位相とを比較する移相比較回路103、比較結果に基づいて移相器111の位相のシフト量を制御する移相器制御電圧生成部117によってフィルタ回路を構成し、増幅率、シフト量が制御される間、カプラー109には信号Vfに代えて基準信号が入力される。

(もっと読む)

受信装置及びイメージ除去方法

【課題】ウィーバー方式又はハートレー方式等のイメージ除去構成と複素フィルタを組み合わせて用いる場合に、希望信号及びイメージ信号の直交性を共に維持する。

【解決手段】直交ミキサ(ミキサ101及び102)は、RF信号をダウンコンバートし、I信号及びQ信号を生成する。複素フィルタ103は、正の周波数領域と負の周波数領域との間で非対称な周波数利得特性を有し、I信号及びQ信号に含まれるイメージ信号を希望信号に比べて抑圧する。直交補償回路106は、複素フィルタ103の後段に配置され、複素フィルタ103によってイメージ抑圧されたI信号及びQ信号の間における希望信号の位相差誤差及び振幅誤差を打ち消すように、I信号及びQ信号を補正する。また、制御回路117は、複素フィルタの後段にてI信号及びQ信号に現れるイメージ信号の位相差誤差及び振幅誤差を打ち消すように、複素フィルタ103の素子特性を調整する。

(もっと読む)

可変利得トランスコンダクタンスステージと同調可能な適応フィルタ

例示的な実施形態では、アナログフィルタ(400)を備えている通信デバイスを提供する。所望の値で、または、所望の範囲内でフィルタの極の位置を管理するために、デジタル信号プロセッサ(410)は、アナログフィルタの利得(420、440)と、フィルタの極の位置(430、480)とを同時に設定する。さらなる実施形態では、フィルタの、利得と極の位置とを同時に設定する方法論も与える。 (もっと読む)

半導体集積回路

【課題】受信系チャンネル選択フィルタの高次フィルタおよび送信系ローパスフィルタの低次フィルタの周波数特性の不所望な変動を軽減する。

【解決手段】送受信機能をサポートする半導体集積回路は、所定の次数の受信系チャンネル選択フィルタと小さな次数の送信ローパスフィルタとキャリブレーション回路200を具備する。チャンネル選択フィルタの第1キャリブレーション動作の間に、抵抗スイッチ回路20が使用され電圧・電流変換器30は基準電圧を第1変換電流に変換して、時間積分器40、50は内蔵容量70の時間積分を実行して、電圧比較の結果がラッチ90に格納され、チャンネル選択フィルタの特性が決定される。ローパスフィルタの第2キャリブレーション動作の間に抵抗回路161が使用されて電圧・電流変換器30は基準電圧を第2変換電流に変換して、電圧比較の結果がラッチ90に格納され、ローパスフィルタの特性が決定される。

(もっと読む)

アクティヴインダクタ

【課題】出力電流雑音の変動しない可変型アクティヴインダクタを提供すること。

【解決手段】トランジスタのゲート−ソース間に並列に容量素子とスイッチを直列接続した素子を接続する。すなわち、PMOSトランジスタM2のドレインとキャパシタC1の一方の端子を接続する。また、端子VinとキャパシタC1のもう一方の端子にスイッチS1の一方の端子を直列接続し、スイッチS1のもう1方の端子をPMOSトランジスタM2のゲートと接続する。スイッチS1を開閉する事で見かけ上のトランジスタのゲート−ソース間容量を変化させてインダクタンス値を変動させるが、MOSトランジスタM1・M2の相互コンダクタンスは変化せず、そのため出力電流雑音は変らない。

(もっと読む)

周波数可変フィルタ回路

【課題】簡素な回路構成で実現でき、小型化可能な周波数可変フィルタ回路を提供すること。

【解決手段】インダクタ12と可変容量素子14(第2の並列容量素子)とが並列に接続された並列共振回路20と、複数の可変容量素子10、11及び13からなるインピーダンス調製回路21と、2つのエミッタフォロワ回路16、18からなるインピーダンス調整回路22と、を備えて周波数可変フィルタ回路1を構成し、可変容量素子10の容量値と可変容量素子11(及び可変容量素子10と可変容量素子13)の容量値との比を調整することにより、並列共振回路20の入力側のインピーダンスを所望値に調整し、エミッタフォロワ回路16及び18によって並列共振回路20の出力側のインピーダンスを所望値に調整することにより、簡素な構成で小型化可能の周波数可変フィルタ回路を構成した。

(もっと読む)

半導体集積回路

【課題】電源電圧の変化に依存する内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】半導体集積回路は校正回路200を具備し、内蔵容量70:151は容量とスイッチを有する。V・I変換器30、20は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧を比較する。校正動作の間に時間積分と電圧比較が実行され、その結果はラッチ90に格納される。校正動作の完了時のラッチ90の格納結果に従って、内蔵フィルタ150の周波数特性が決定される。V・I変換器30、20のスイッチ素子SW0のNチャンネルMOSトランジスタのゲートに、校正動作の間に安定化電圧VREFが供給される。

(もっと読む)

フィルタ回路

【課題】本発明は、フィルタリング特性調整機能を有するアナログフィルタを有するフィルタ回路に関し、アナログフィルタのフィルタリング特性を簡易な補正回路によって補正する機能を備える。

【解決手段】アナログフィルタ50と、レプリカ回路としての発振器61と、周波数比較ロジック62を備え、周波数比較ロジック62で、その発振器61の発振周波数が基準周波数となるように、発振器61とアナログフィルタ50との双方を同時に調整する。

(もっと読む)

1 - 20 / 54

[ Back to top ]