Fターム[5J098AB11]の内容

能動素子を用いた回路網 (5,588) | 回路要素 (1,356) | 定電圧回路、バイアス回路、基準電圧 (58)

Fターム[5J098AB11]に分類される特許

1 - 20 / 58

フィルタ装置およびその制御方法

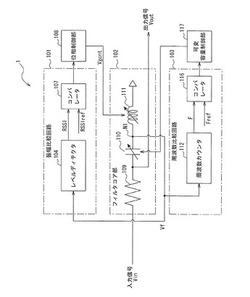

【課題】フィルタのノッチ周波数を調整する機能を持ったフィルタ装置を提供する。

【解決手段】入力信号を抵抗109と可変容量110、アクティブインダクタ111を備えたフィルタコア部102にて分圧し、フィルタコア部102のフィルタ特性信号Vfの振幅と基準振幅とを比較する振幅比較回路101、振幅比較回路101での比較結果に基づいてアクティブインダクタ111の位相を制御する位相制御部108、フィルタコア部102のフィルタ特性信号Vfの周波数と基準周波数とを比較する周波数比較回路103、周波数比較回路103の比較結果に基づいて可変容量110の容量を制御する可変容量制御部117によってフィルタ装置を構成し、アクティブインダクタ111の位相、可変容量11の容量が制御される間、アクティブインダクタ111の位相制御部108が、フィルタコア部102を発振させる。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

カットオフ周波数自動調整回路及び携帯情報端末

【課題】フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能にする。

【解決手段】電圧電流変換回路(30)、充電回路(50)、放電回路(40)、複数の静電容量を有するデジタル容量(70)、上記デジタル容量に入力される電圧と基準電圧との対比を行う比較器(80)及び上記デジタル容量を制御する容量制御回路(600)を含んでカットオフ周波数自動調整回路(412)を構成する。上記リセット信号が所定の論理レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間を計測し、その計測結果と、上記デジタル容量の目標値と、上記デジタル容量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理を、所定の条件下で繰り返すことによって上記デジタル容量を制御する。上記目標値は、調整範囲内の任意の設定値とすることができる。

(もっと読む)

ロードスイッチ

【課題】小さい入力−出力差分電圧を維持し、既定の応答を提供する半導体装置、回路、そしてAC及びDCロードスイッチを提供する。

【解決手段】ロードスイッチは、入力端子及び出力端子へ結合された通過素子を含み得る。通過素子は制御端子を含み、制御端子は通過素子の応答を制御し得る。ロードスイッチは第1のループを含み得る。第1のループは制御端子へ結合され、通過素子との高インピーダンスを維持しながら入力端子及び出力端子間の電圧降下を制御するように構成される。ロードスイッチは第2のループを含み得る。第2のループは制御端子へ結合され、既定のフィルタ応答を入力端子から提供するように構成される。既定の応答は、低域通過応答、高域通過応答、又は帯域通過応答であり得る。応答の通過帯域及び/又は阻止帯域は、プログラムされ得る。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

フィルタ回路

【課題】 回路規模を増大させることなく、コモンモードノイズを除去できるフィルタ回路を提供すること。

【解決手段】 フィルタ回路1は、オペアンプQ1と、オペアンプQ1の非反転入力端子と入力信号源との間に接続された抵抗R2と、オペアンプQ1の非反転入力端子に接続されたコンデンサC3と、オペアンプQ1の非反転入力端子に接続された抵抗R3と、オペアンプQ1の反転入力端子と入力信号源との間に接続された抵抗R4と、オペアンプQ1の反転入力端子と出力端子との間に接続されたコンデンサC4と、オペアンプQ1の反転入力端子に接続された抵抗R5とを備える。抵抗2の抵抗値と抵抗R4の抵抗値とが等しく、コンデンサC3の容量値とコンデンサC4の容量値とが等しく、抵抗R3の抵抗値と抵抗R5の抵抗値とが等しく設定されている。

(もっと読む)

可変抵抗制御回路及び可変抵抗器

【課題】抵抗を広い範囲で変化させることができる可変抵抗制御回路及び可変抵抗器を提供すること

【解決手段】本発明にかかる可変抵抗制御回路は、電源10と、電源10よりも低い電位を有する電源11との間に設けられ、電源10と接続される抵抗21と、電源10と、電源11との間に設けられ、前記抵抗21と直列に接続されるMOSトランジスタ31と、電源10と、電源11との間に設けられ、前記MOSトランジスタ31と直列に接続されるMOSトランジスタ32と、抵抗21とMOSトランジスタ31との節点における電圧と、制御電圧とに基づいて、MOSトランジスタ32にゲート電圧を出力するオペアンプ41とを備え、オペアンプ41は、ゲート電圧に基づいて抵抗値が制御される外部の可変抵抗に対してゲート電圧を出力するものである。

(もっと読む)

ローパスフィルタ設計

高い品質係数(Q)を有するローパスフィルタリングのための手法。 例示的な実施形態では、入力電流は第1のトランジスタのドレインに接続される。 1のトランジスタのドレインとゲートとは抵抗器R1によって一緒に結合され、そして、ドレインは第1キャパシタC1によって基準電圧に結合される。ゲートは第2のキャパシタC2により、基準圧に結合される。ゲートはさらに第2のトランジスタのゲートに結合され、出力電流が第2のトランジスタのドレインに接続される。別の例示的な実施形態では、さらに受動素子が奇数次のローパス伝達特性を発生するために結合されることができる。 複数のフィルタは、任意のオーダーを有するフィルタを合成するために、直列にカスケード接続することができる。  (もっと読む)

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

フィルタ回路およびバイアス回路

【課題】回路面積の縮小を図りつつ、出力信号に含まれるオフセットを減少させることが可能なフィルタ回路を提供する。

【解決手段】フィルタ回路は、入力端子と出力端子との間に接続された第1のキャパシタと、前記出力端子と設定電位との間に接続されたバイアス回路と、を備え、前記バイアス回路は、前記出力端子と設定電位との間に接続された第1のMOSトランジスタと、前記第1のMOSトランジスタのゲートと前記出力端子との間に接続された第2のキャパシタと、前記第1のMOSトランジスタのゲートに一端が接続され、第1のバイアス電位が他端に印加された抵抗素子と、を有する。

(もっと読む)

半導体集積回路

【課題】受信系チャンネル選択フィルタの高次フィルタおよび送信系ローパスフィルタの低次フィルタの周波数特性の不所望な変動を軽減する。

【解決手段】送受信機能をサポートする半導体集積回路は、所定の次数の受信系チャンネル選択フィルタと小さな次数の送信ローパスフィルタとキャリブレーション回路200を具備する。チャンネル選択フィルタの第1キャリブレーション動作の間に、抵抗スイッチ回路20が使用され電圧・電流変換器30は基準電圧を第1変換電流に変換して、時間積分器40、50は内蔵容量70の時間積分を実行して、電圧比較の結果がラッチ90に格納され、チャンネル選択フィルタの特性が決定される。ローパスフィルタの第2キャリブレーション動作の間に抵抗回路161が使用されて電圧・電流変換器30は基準電圧を第2変換電流に変換して、電圧比較の結果がラッチ90に格納され、ローパスフィルタの特性が決定される。

(もっと読む)

フィルタ回路

【課題】高速でかつ低消費電流であり、MOSトランジスタのしきい値電圧の絶対値が低い場合でも入力信号レベルを大きくすることができるフィルタ回路を提供する。

【解決手段】ゲートから信号を入力するMOSトランジスタ(Tr)1、Tr2、ドレインがMOSトランジスタ1のソースに接続され、ゲートがMOSトランジスタ2のソースに接続されるTr3、ドレインがTr2のソースに接続され、ゲートがTr1のソースに接続されるTr4、Tr3のソースに電流を供給する電流源5、Tr4のソースに電流を供給する電流源6、Tr1〜Tr4のソースの各々に接続されるコンデンサ7、8を含むフィルタ回路に、Tr3、Tr4の動作点が飽和領域内の線形領域に近い側から遠い側に向かう方向にシフトするように電圧を印加する電圧源101、102を設ける。

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

半導体装置

【課題】高い精度のインピーダンス調整回路を有する半導体装置を提供する。

【解決手段】可変抵抗回路と外部抵抗素子との分圧電圧と、基準電圧とを比較する差動増幅回路にオフセット調整回路を設ける。オフセット調整回路は、第1と第2オセット調整信号によりそれぞれオン/オフ制御されて上記差動増幅回路の第1と第2負荷抵抗に流れる電流を形成し、それぞれ並列形態にされた複数からなる第2と第3MOSFET群を有する。上記差動増幅回路の両入力に基準電圧を供給した状態にし、上記第2と第3MOSFET群に供給される第1オフセット調整信号による電流を変化させて上記差動増幅回路及びデジタル変換段を通した出力信号が変化した時点での第1オフセット調整信号又は上記第2オフセット調整信号をオフセット調整設定信号とする。

(もっと読む)

アクティヴインダクタ

【課題】出力電流雑音の変動しない可変型アクティヴインダクタを提供すること。

【解決手段】トランジスタのゲート−ソース間に並列に容量素子とスイッチを直列接続した素子を接続する。すなわち、PMOSトランジスタM2のドレインとキャパシタC1の一方の端子を接続する。また、端子VinとキャパシタC1のもう一方の端子にスイッチS1の一方の端子を直列接続し、スイッチS1のもう1方の端子をPMOSトランジスタM2のゲートと接続する。スイッチS1を開閉する事で見かけ上のトランジスタのゲート−ソース間容量を変化させてインダクタンス値を変動させるが、MOSトランジスタM1・M2の相互コンダクタンスは変化せず、そのため出力電流雑音は変らない。

(もっと読む)

バイアス回路及びそれを備えたgm−Cフィルタ回路並びに半導体集積回路

【課題】実装面積の増加を抑えつつ、温度変動や閾値電圧Vthの製造バラツキでの影響を抑えることができるバイアス回路及びそれを備えたgm−Cフィルタ回路並びに半導体集積回路を提供すること。

【解決手段】第1電流源Iaをなす第1のPMOSトランジスタQ1と、第1のPMOSトランジスタQ1のカレントミラー回路を構成し、第2電流源Ibをなす第2のPMOSトランジスタQ2と、第1電流源Iaからそのドレインに電流が供給される第1のNMOSトランジスタQ3と、第1のNMOSトランジスタQ3とカレントミラー回路を構成し、第2電流源Ibからそのドレインに電流が供給される第2のNMOSトランジスタQ4と、第2のNMOSトランジスタQ4のソースとグランドとの間に接続された抵抗とを備え、さらに、第1のNMOSトランジスタQ3のソースとグランドとの間にgm調整用の抵抗成分Zrを接続した。

(もっと読む)

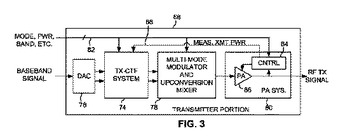

プログラム可能送信連続時間フィルタ

プログラム可能電流の送信連続時間フィルタ(TX−CTF)システムは無線周波数(RF)送信機に含まれ得る。TX−CTFの入力はベースバンド送信信号を受信することができ、TX−CTFの出力はアップコンバージョンミキサに供給されて、送信用のRFに変換され得る。TX−CTFは、フィルタパラメータをともに規定する増幅回路および受動回路を含む。TX−CTFはさらに、プログラム可能バイアス電流を増幅回路に供給するプログラム可能電流回路を含む。TX−CTFシステムはまた、1つ以上の送信機制御信号を受信し、これに応じて、TX−CTFに供給されるバイアス電流を制御する信号を生成する制御論理を含む。  (もっと読む)

(もっと読む)

フィルタ回路、連続時間フィルタ及び信号再生装置

【課題】周波数帯域を制限するフィルタ回路に関し、周波数とは、独立に利得を調整する。

【解決手段】第1の電圧/電流変換回路(12)に、係数設定回路(16)からの第1の制御信号と利得調整のための第2の制御信号とから作成した第3の信号を入力し、第2の電圧/電流変換回路(14)に、第1の制御信号を入力する。このため、周波数と、利得を独立に制御したフィルタを実現できる。

(もっと読む)

半導体集積回路

【課題】電源電圧の変化に依存する内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】半導体集積回路は校正回路200を具備し、内蔵容量70:151は容量とスイッチを有する。V・I変換器30、20は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧を比較する。校正動作の間に時間積分と電圧比較が実行され、その結果はラッチ90に格納される。校正動作の完了時のラッチ90の格納結果に従って、内蔵フィルタ150の周波数特性が決定される。V・I変換器30、20のスイッチ素子SW0のNチャンネルMOSトランジスタのゲートに、校正動作の間に安定化電圧VREFが供給される。

(もっと読む)

フィルタ回路

【課題】平滑用コンデンサに対する充電電流及び放電電流による時定数を大きくした場合であっても、平滑用コンデンサの体格の大型化や、オフセット電圧の増加を抑制することが可能なフィルタ回路を提供する。

【解決手段】入力電圧とフィルタ処理電圧との電圧差に応じた電流を、カスコード型カレントミラー回路を利用して減衰させて、平滑用コンデンサC1の放電電流I11及び放電電流I12を発生させる。さらに、平滑用コンデンサC1の充電電流I12の一部となるベース電流Ib1’を流すトランジスタT23を、トランジスタT24と抵抗R13,R14からなる回路により、フィルタ回路10の後段回路と分離する。

(もっと読む)

1 - 20 / 58

[ Back to top ]