Fターム[5J098AD03]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 遅延、移相特性の改善 (27)

Fターム[5J098AD03]に分類される特許

1 - 20 / 27

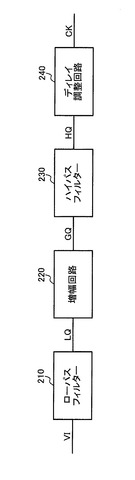

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

狭帯域雑音低減のためのフィルタ及び可調整遅延ユニット

【課題】ベースバンド信号をフィルタし、無線通信の信頼性を改善する技術の提供。

【解決手段】無線通信システムにおける雑音減少の為の技術として受信信号をフィルタするために制御可能な帯域幅フィルタ120を使用する。フィルタ120はベースバンド周波数で使用され、測定(RSSI)は受信信号強度を表し、フィルタ制御回路144はフィルタ120の帯域幅を制御する為に制御信号146を生成する。受信信号強度が第一の閾値を超えていれば、より広い帯域幅がフィルタ120の為に使用され、受信信号強度が第二の閾値以下であれば、フィルタ制御回路144はフィルタ120をより狭い帯域幅に設定する為に制御信号146を生成する。フィルタの帯域幅は又狭帯域干渉(妨害信号)の存在に応じて変動し、可調整遅延ユニットはフィルタの全ての可能な構成の間で一定の群遅延を保証する。

(もっと読む)

狭帯域雑音低減のためのフィルタ及び可調整遅延ユニット

【課題】ベースバンド信号をフィルタし、無線通信の信頼性を改善する技術の提供。

【解決手段】無線通信システムにおける雑音減少の為の技術は受信信号をフィルタするために制御可能な帯域幅フィルタ120を使用する。フィルタ120はベースバンド周波数で使用され、測定(RSSI)は受信信号強度を表している。フィルタ制御回路144はフィルタ120の帯域幅を制御する為に制御信号146を生成する。受信信号強度が第一の閾値を超えていれば、より広い帯域幅がフィルタ120の為に使用され、受信信号強度が第二の閾値以下であれば、フィルタ制御回路144はフィルタ120をより狭い帯域幅に設定する為に制御信号146を生成する。フィルタの帯域幅は又狭帯域干渉(妨害信号)の存在に応じて変動する。可調整遅延ユニットはフィルタの全ての可能な構成の間で一定の群遅延を保証する。

(もっと読む)

抵抗値補正回路

【課題】外付けの基準抵抗と半導体集積回路に形成した抵抗の遅延量を比較して、半導体集積回路に形成した抵抗の抵抗値を補正する抵抗値補正回路を提供する。

【解決手段】半導体集積回路に形成した抵抗29と半導体集積回路の外部に設けられた基準抵抗33に予め設定された周期のクロック信号を入力し、抵抗29から出力された第1の信号A1と基準抵抗33から出力された第2の信号A2との遅延差を検出する遅延判定回路3と、直列接続される複数のフリップフロップにより構成されるフリップフロップ部に、遅延判定回路3で遅延差を計測開始と同時にクロック信号を入力し、フリップフロップごとに順次クロック信号を遅延させ、フリップフロップごとに遅延信号を出力し、遅延差が発生している期間に出力された遅延信号を選択して出力するばらつき検出回路と、を備える抵抗値補正回路1である。

(もっと読む)

遅延回路および半導体装置

【課題】入力信号を遅延させ出力する遅延回路において、動作時の消費電流低減をはかる。

【解決手段】遅延回路100の端子202に、Pチャネル型MOSトランジスタ105を介して容量素子107を接続する。NAND回路104は、入力端子が、遅延回路100の入力端子201とインバータ103へ接続され、出力端子がPチャネル型MOSトランジスタ105のゲート端子へ接続される。インバータ103は、入力端子が遅延回路100の出力端子へ接続される。Pチャネル型MOSトランジスタ105は、遅延回路100の出力信号がLレベルからHレベルに遷移することに応答して、端子202と容量素子107を電気的に非接続とする。

(もっと読む)

フィルター回路

【課題】入力信号の周波数が高くなるほど出力信号の入力信号に対する相対的な位相が進行し、入力信号の周波数が低くなるほど出力信号の入力信号に対する相対的な位相差がなくなる周波数領域を使用するフィルター回路を得る。

【解決手段】抵抗とコンデンサによって構成されるフィルター回路において、入力端子Iと接地端子Gの間に第1の抵抗R1と第2の抵抗R2とコンデンサCがこの順番で直列に接続され、第1の抵抗R1と第2の抵抗R2の接続点に出力端子Oが設けられており、第1の抵抗R1と第2の抵抗R2の合成抵抗値とコンデンサCの静電容量値によって決定されるカットオフ周波数より高い周波数領域にある最大位相遅延周波数より高い周波数領域を使用することにより、入力信号の周波数が高くなるにつれて、出力信号の入力信号に対する相対的な位相の遅れが小さくなる特性を発揮するフィルター回路による。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

パルス伸長回路及び半導体装置

【課題】幅のより短いパルスに対して伸長が可能なパルス伸長回路及び半導体装置を提供する。

【解決手段】それぞれのソースが定電流源21を介して電源端子5に接続され、それぞれのドレインが定電流源21より電流駆動能力の大きな定電流源22を介して接地端子6に接続され、ゲートが入力端子27に接続されたp‐MOSトランジスタP1及びゲートが出力端子28に接続されたp‐MOSトランジスタP2と、一端がp‐MOSトランジスタP1、P2のソースと定電流源21との間に接続され、他端が接地端子6に接続されたキャパシタC1と、ドレインがp‐MOSトランジスタP2のゲートに接続され、且つ定電流源23を介して電源端子5に接続され、ソースが接地端子6に接続され、ゲートがp‐MOSトランジスタP1、P2のドレインと定電流源22との間に接続されたn‐MOSトランジスタN1とを備える。

(もっと読む)

信号処理回路、電子機器、信号処理方法及びプログラム

【課題】IF信号からベースバンド信号をより正確に再生するための新たな手法を提案すること。

【解決手段】フィルタ部のフィルタの遮断周波数に応じて周期波形の形状を変更して再生用発振信号を生成し、生成した再生用発振信号を用いてベースバンド信号を再生する。具体的には、フィルタの遮断周波数が低いほど、正の振幅から負の振幅までの正負振幅間長が長い周期波形の再生用発振信号を用いてベースバンド信号を再生する。

(もっと読む)

フィルタ回路

【課題】 アクティブフィルタにおいて、オペアンプのGB積が不足していても十分な特性が得られるようにする。

【解決手段】 入力信号を抵抗器R41を通じてオペアンプQ41Iの非反転入力端に供給するとともに、オペアンプQ41Iの反転出力端と非反転入力端との間に、帰還用のコンデンサC41を接続してアクティブフィルタを構成する。コンデンサC41に別の抵抗器r41を直列に接続する。コンデンサC41の値と、抵抗器r41との積C41・r41を、オペアンプQ41IのGB積に対して

GB=1/(C41・r41)

に設定する。

(もっと読む)

位相調整回路、妨害信号除去回路、および無線受信装置

【課題】全ての周波数範囲においてI信号とQ信号の位相差が一定となるように調整できる位相調整回路、その位相調整回路を備えた妨害信号除去回路、およびその妨害信号除去回路を備えた無線受信装置を提供する。

【解決手段】入力端子T1と入力端子T2からそれぞれ入力されたI信号とQ信号は、加算器21で加算され、アッテネータ22で1/X倍に減衰される。減衰された信号は、加算器23でI信号と加算されて出力端子T3より出力される。また、減衰された信号は、加算器24でQ信号と加算され、出力端子T4より出力される。この操作によりI信号とQ信号の位相差を縮小する。位相の遅れた同相成分を位相調整に用いるため、低周波数成分側のI信号とQ信号の位相差と高周波数成分側のI信号とQ信号の位相差をほぼ等しく保ちながらI信号とQ信号の位相を変化させることができる。

(もっと読む)

遅延回路

【課題】電荷蓄積用キャパシタに蓄積された情報を破壊することなく読み出すことのできるスイッチト・キャパシタ型の遅延回路を提供する。

【解決手段】遅延セル11〜13は、書き込み信号Wが入力されたときに入力端子INへ入力される電流を取り込み、その取り込んだ電流の大きさに応じた電荷をキャパシタC1に蓄積し、そのキャパシタC1の出力電圧で電流源のNMOSトランジスタM1の出力電流の大きさを制御し、読み出し信号Rが入力されたときにその出力電流を出力する。書き込み制御用のシフトレジスタ2は、遅延セル11〜13へ入力する書き込み信号W1〜W3を制御し、遅延セル11〜13への電流の取り込みタイミングを1個ずつ遅延させる。読み出し制御用のシフトレジスタ3は、遅延セル11〜13へ入力する読み出し信号R1〜R3を制御し、電流の取り込み終了後の遅延セル11〜13からの電流の出力タイミングを制御する。

(もっと読む)

遅延信号生成装置、および遅延量制御方法

【課題】短い時間で精度良くデータを記録する。

【解決手段】図1の遅延信号生成装置は、光ディスク記録装置に設けられる。検出部105は、第2遅延信号と第1遅延信号の遅延量の差が検出用パルス信号のパルス幅となるときの第2遅延セレクト信号を求め、その第2遅延セレクト信号に対応する出力位置と第1遅延セレクト信号に対応する出力位置との間にあるバッファの数を、検出結果として出力する。遅延量制御部106は、上記検出結果に基づいて、制御入力信号を求める。記録用ディレイライン101は、上記制御入力信号に応じた遅延量だけ記録用クロックを遅延させる。制御入力信号を求める遅延キャリブレーション動作は、記録中に行われる。

(もっと読む)

半導体集積回路装置

【課題】光ディスク装置のアナログフロントエンド処理において、ノイズを増加させることなく、バンドパスフィルタの位相改善を行う。

【解決手段】位相補正回路11,12は、トランジスタ24,25、抵抗28,29、ならびに定電流源32からなる差動信号VINを増幅するアンプ部と、トランジスタ22,23、静電容量素子26,27、および定電流源30,31からなる差動信号VINの位相を進め、高周波帯域をブーストする位相補正部とから構成されている。差動信号VINの位相進めは、静電容量素子26,27の静電容量値、またはトランジスタ22,23のトランジスタサイズ(ゲートサイズ)を任意に可変することにより、バンドパスフィルタ19に入力される信号の位相が略0°となるように設定する。

(もっと読む)

移相器、および移相方法

【課題】精度の高い移相を行うことが可能な移相器を提供する。

【解決手段】入力信号Vin1と、入力信号Vin1の移相量を規定する第1デジタル制御信号C1[0:N−1]とが入力され、入力信号Vin1と、第1デジタル制御信号C1[0:N−1]に基づいて算出される乗算値とを乗算して第1出力信号を出力する第1乗算部104と、入力信号Vin1と位相が直交する直交入力信号と、移相量を規定する第2デジタル制御信号C2[0:N−1]とが入力され、直交入力信号と、第2デジタル制御信号C2[0:N−1]に基づいて算出される乗算値とを乗算して第2出力信号を出力する第2乗算部108と、移相量に対応する第3デジタル制御信号C3[0:1]に基づいて、第1出力信号と第2出力信号との加算、または、減算を行う加減算部110とを備える移相器が提供される。

(もっと読む)

移相器および無線送信装置

【課題】低周波において90°位相発生器で矩形波となった場合においても位相精度が良好で、広帯域で利用可能な移相器および当該移相器を具備し歪み補償機能を有する無線送信装置を提供すること。

【解決手段】移相器100に、入力信号から90°の位相差を持つ第1の信号および第2の信号を出力する90°位相回路110と、前記第1および第2の信号をそれぞれ入力し位相制御電圧に従って出力信号の振幅および極性を制御するバランスドミキサ120a,bと、バランスドミキサ120a,bの出力信号を合成し合成信号を出力するコンバイナ130と、前記合成信号を増幅して出力するバッファ150と、コンバイナ130とバッファ150との間に設けられ前記合成信号を波形整形する波形整形フィルタ140とを設けた。無線通信装置に移相器100を用いることにより、広帯域に負帰還補償が可能となる。

(もっと読む)

フィルタ装置、及びそれを用いたフィードバック制御装置

【課題】入力信号のうちノイズ等の無用な高周波成分を低減させながら、制御すべき周波数帯域の位相遅れが小さいフィルタ装置、及びそれを用いたフィードバック制御装置を提供することを目的とする。

【解決手段】入力信号の高周波ノイズを低減するフィルタ装置であって、入力信号を位相遅れ処理して位相遅れ信号を出力する一次遅れフィルタ部と、前記入力信号を微分処理して微分信号を出力する微分特性処理部と、前記位相遅れ信号と前記微分信号を加算して出力信号を得る加算処理部とを備えることを特徴とするフィルタ装置、及びそれを用いたフィードバック制御装置。

(もっと読む)

遅延回路及びそれを用いた映像信号処理回路

【課題】ドレイン・基板間の寄生容量を軽減させる。

【解決手段】充電用・放電用トランジスタとそれらのソースに接続された容量素子とを有したスイッチド・キャパシタ部を複数有し、入力信号が充電用トランジスタのドレイン各々に対して共通に入力され且つ容量素子を充電させるように接続されるとともに、放電用トランジスタのドレイン各々から容量素子を放電させて出力信号が出力されるように接続されるスイッチド・キャパシタ群と、充電用及び放電用トランジスタのゲート各々のオン・オフを制御して容量素子各々を入力信号に基づいて順次充電させるとともに、当該順次充電の際に前回充電しておいた容量素子を放電させることで出力信号を順次出力させるスイッチング制御部と、を有し、隣接する二つの前記スイッチド・キャパシタ部において、双方の充電用・放電用トランジスタ同士を隣接させ、双方の充電用・放電用トランジスタのドレインを共通させる。

(もっと読む)

遅延回路およびそれを用いた電圧制御発振器

【課題】 良好な波形を有する信号を生成可能な遅延回路を提供する。

【解決手段】 第1、第2PMOSトランジスタP1、P2は、ゲートが第1入力端子12、第2入力端子14に接続される。第1NMOSトランジスタN1は、ゲートが第1入力端子12に、ドレインが第1PMOSトランジスタP1のドレインに接続される。第2NMOSトランジスタN2は、ゲートが第2入力端子14に、ドレインが第2PMOSトランジスタP2のドレインに接続される。第3NMOSトランジスタN3は、ゲートおよびドレインが第1PMOSトランジスタP1のドレインに接続され、第4NMOSトランジスタN4は、ゲートおよびドレインが第2PMOSトランジスタP2のドレインに接続される。第1電流源20を、第1、第2PMOSトランジスタP1、P2のソースに接続し、第2、第3電流源22、24を、第1、第4NMOSトランジスタN1、N4のソースに接続する。

(もっと読む)

1 - 20 / 27

[ Back to top ]