Fターム[5J100BA07]の内容

増幅器の制御の細部、利得制御 (10,574) | 被制御回路 (627) | 増幅器 (475) | 演算増幅器(オペアンプ) (56)

Fターム[5J100BA07]に分類される特許

1 - 20 / 56

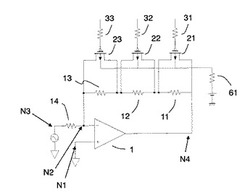

抵抗の調整機能を有する演算回路

【課題】MOSスイッチによる抵抗の調整機能を有する演算回路において、面積の増加を最小限に留め、かつ、非常に簡易な方法でMOSスイッチの寄生容量の影響を抑える演算回路を提供する。

【解決手段】MOSスイッチ21−23のゲートやバックゲートに、調整対象の抵抗11−13よりも数倍以上大きな抵抗31−33、61を設けることにより、寄生容量でできる極とほぼ同じ周波数にゼロが発生し、寄生容量の影響を抑えることができる。この抵抗には、絶対値バラつきや温度特性、相対バラつきやノイズ等の特性は要求されないため、用いるプロセスで最もシート抵抗の高い抵抗を細い幅で作成すればよく、面積の増加量は少ない。また、抵抗は容量よりも微細化が容易であるため、今後更にプロセスの微細化が進んでも本発明を変わらず使用できる。

(もっと読む)

可変利得増幅回路,および可変利得増幅回路を用いた通信装置

【課題】利得ズレを抑制する可変利得増幅回路を提供する。

【解決手段】可変利得増幅回路は,一端が第1の可変利得増幅器11の入力抵抗Ri10 と入力スイッチSWi10との第1の接続ノードN1に接続され,他端が第1の可変利得増幅器の後段側の第2の可変利得増幅器13の演算増幅器OP3の入力端に接続されたバイパススイッチSWb13を有する。

(もっと読む)

誤差増幅回路及びスイッチングレギュレータ

【課題】位相補償回路を内蔵する誤差増幅回路と比較して、回路規模及び回路の消費電流を大きくすることなく、位相補償容量を外付けにすることができる誤差増幅回路及び当該誤差増幅回路を用いたスイッチングレギュレータを提供する。

【解決手段】所定の基準電圧Vref1と入力電圧Vfb1との誤差を増幅して出力する誤差増幅器12と、誤差増幅器12にバイアス電流Ibias1を供給する電流生成回路11とを含む集積回路10を備えた誤差増幅回路10aにおいて、集積回路10は、電流生成回路11に接続されたバイアス電流制御端子T1と、位相補償抵抗14を介して誤差増幅器12の出力端子T11に接続された位相補償端子T2とを備え、誤差増幅回路10aは、位相補償端子T2に接続された位相補償容量30を集積回路10の外部に備える。

(もっと読む)

ボリューム調整回路

【課題】ディジタル的に出力電圧を変化させるボリューム調整回路において、ダイサイズの大幅な増大をまねくことなく、ジッパーノイズの発生を抑制する。

【解決手段】ボリューム調整回路は、オペアンプ1と、オペアンプ1の出力端子と反転入力端子との間に接続され、離散的な複数の抵抗値を有するボリューム回路2と、入力電圧の電圧源とオペアンプ1の反転入力端子との間に接続され、ボリューム回路2を流れる電流の大きさを変化させるR−2Rラダー回路3と、ボリューム回路2及びR−2Rラダー回路3を制御する制御回路6とを備える。制御回路6は、ボリューム回路2の抵抗値を第1の抵抗値から第2の抵抗値に変更するとき、第1の抵抗値に対応する出力電圧と第2の抵抗値に対応する出力電圧との間の差をさらに細分化したステップサイズで出力電圧を変化させるように、R−2Rラダー回路3を用いてボリューム回路2を流れる電流の大きさを変化させる。

(もっと読む)

利得切換型増幅器およびそれを用いたオーディオ機器

【課題】ポップノイズの発生を、再生時の音声品質を維持しつつ、防ぐ。

【解決手段】オペアンプ回路1の出力端子からの出力信号を、オペアンプ回路1の反転入力端子にフィードバックするフィードバック回路2を具備し、フィードバック回路2でフィードバックする帰還電圧を減衰することにより利得切換を行い、オペアンプ回路1に入力された入力信号の出力レベル調整を行う利得切換型増幅器において、オペアンプ回路1の非反転入力端子に、入力信号を減衰して入力するアッテネータ回路3を設け、このアッテネータ回路3の減衰率の設定とフィードバック回路2の減衰率の設定の組み合わせにより、信号出力レベルの切換分解能を上げることで、例えば音声出力レベルを連続的に変化させることを可能とし、ポップノイズの発生を防ぐ。

(もっと読む)

可変ゲイン差動入出力アンプ

【課題】単位抵抗の数を少なくすることができる可変ゲイン差動入出力アンプを提供する。

【解決手段】第1のオペアンプと、第2のオペアンプと、前記第1のオペアンプの出力と前記第2のオペアンプの出力間に単位抵抗からなる抵抗群を複数直列接続して複数のゲイン設定値に対応する分割比に抵抗分割した第1の抵抗列と、前記抵抗分割により得られる分割電圧を選択して前記第1及び前記第2のオペアンプの反転入力に入力するスイッチ手段とを備える可変ゲイン差動入出力アンプにおいて、単位抵抗からなる抵抗群を複数直列に接続して前記複数のゲイン設定値より高いゲイン設定値に対応する分割比に抵抗分割した第2の抵抗列を前記第1の抵抗列と並列に接続する。

(もっと読む)

入力セレクタおよび信号処理回路

【課題】さまざまな入力形式の信号に柔軟に適応可能な汎用性の高い入力セレクタを提供する。

【解決手段】第1抵抗R1〜第4抵抗R4は、それぞれの第1端子が対応する入力ポートPi1〜Pi4に接続される。第1スイッチSW1〜第4スイッチSW4はそれぞれ、対応する抵抗と第1演算増幅器10の反転入力端子の間に設けられる。第5スイッチSW5、第6スイッチSW6はそれぞれ、対応する抵抗と、第2演算増幅器12の反転入力端子の間に設けられる。第5抵抗R5および第7スイッチSW7は第1演算増幅器10の出力端子と第2演算増幅器12の反転入力端子の間に直列に設けられる。第6抵抗R6は第1演算増幅器10の出力端子と反転入力端子の間に設けられ、第7抵抗R7は第2演算増幅器12の出力端子と反転入力端子の間に設けられる。

(もっと読む)

可変利得増幅回路

【課題】入出力範囲を電源電圧まで可能とする。

【解決手段】入力段に第1の演算増幅器51が、出力段に第2の演算増幅器52が、それぞれ配されると共に、第1の演算増幅器51の帰還路に第1のトランスコンダクタンス増幅器53が、第1及び第2の演算増幅器51,52の間に、第2のトランスコンダクタンス増幅器54が、それぞれ配されてなり、第1の演算増幅器51には第1の抵抗器61を介して入力信号を印加可能とし、その第1の抵抗器51に流れる電流と、第1の演算増幅器51の負帰還電流を等しくする一方、第2の演算増幅器52の入出力端子間に第2の抵抗器62を設けると共に、第2の演算増幅器52には、その終段がフルスイング可能に構成されたものを用い、第2の抵抗器62に流れる電流と第2のトランスコンダクタンス増幅器54の出力電流を等しくすることで、入出力範囲が電源電圧まで広げられたものとなっている。

(もっと読む)

可変利得増幅器

【課題】可変利得増幅器の利得可変範囲の拡張と非線形歪みの低減を両立する。

【解決手段】可変利得増幅器は、演算増幅器(1)と、与えられた制御電圧に応じた抵抗値を呈する可変抵抗素子(21,22)が複数個直列接続されてなり、演算増幅器(1)の入力端と出力端との間に接続された可変抵抗回路(2)と、利得制御信号に応じた制御電圧であって互いに演算増幅器(1)の入出力直流成分差に応じたオフセットを有する複数の制御電圧を生成して複数の可変抵抗素子(21,22)のそれぞれに与える制御回路(3)とを備えている。

(もっと読む)

増幅回路

【課題】利得の変化量を大きくさせ得る増幅回路を提供する。

【解決手段】演算増幅器2の反転入力端子に一端が接続された入力抵抗3と、非反転入力端子に一端が接続され、他端が入力抵抗3の他端に接続された入力抵抗4と、演算増幅器2の反転入力端子と出力端子との間に接続された抵抗5と、演算増幅器2の反転入力端子にドレイン端子が接続され、かつゲート端子およびソース端子がグランド電位GNDに規定されたFET6と、演算増幅器2の非反転入力端子にドレイン端子が接続され、ソース端子がグランド電位GNDに規定されたFET6と同型のFET7とを備え、各入力抵抗3,4が各FET6,7の作動時のドレイン・ソース間の抵抗値RFETよりも大きな抵抗値に規定され、FET7のゲート端子に増幅率制御用の制御電圧Vcが入力される。

(もっと読む)

高周波送信機の出力回路

【課題】最大電力出力時の信号帯域外の雑音出力電力を抑制するとともに,低利得領域での通信品質の劣化を抑えた高周波送信機の出力回路を提供する。

【解決手段】

高周波送信機の出力回路は,第1の周波数の信号を増幅する微調用の可変利得増幅器と,その出力信号の周波数をアップコンバートした信号であって第1の周波数より高い第2の周波数の信号を増幅する粗調用の可変利得増幅器と,微調用の可変利得増幅器の利得をその利得可変範囲で昇降させるたびに,粗調用の可変利得増幅器の利得をその可変幅ずつ昇降させて,全体の利得を最少利得と最大利得との間で昇降制御する利得制御ユニットとを有する。利得制御ユニットは,粗調用の可変利得増幅器の利得を最大利得レンジに制御した時の微調用の可変利得増幅器の利得可変範囲内の最大利得よりも,粗調用の可変利得増幅器の利得を最小利得レンジに制御した時の微調用の可変利得増幅器の利得可変範囲内の最大利得を,低く制御する。

(もっと読む)

電子ボリューム回路

【課題】ゲインに関する誤差が小さく、且つ、雑音が低い電子ボリューム回路を実現する。

【解決手段】演算増幅器OP1と、入力端子Vinと演算増幅器の入力端(−)との間に設けられた可変入力抵抗部RI,RJと、演算増幅器の出力端Voutと入力端Vin子との間に設けられた可変帰還抵抗部RK,RLと、可変入力抵抗部を構成する各抵抗素子RI,RJと可変帰還抵抗部を構成する各抵抗素子RK,RLとの組合せを選択することによってゲインを可変設定する選択制御部10と、を備え、選択制御部10は、この電子ボリューム回路に設定されたゲインに応じて各可変入力抵抗部RI,RJと、可変帰還抵抗部RK,RLとの大小の組合せを選択してゲインの誤差と雑音とを抑制する。

(もっと読む)

感度調整回路

【課題】感度調整量の線形性を確保しながら小規模な回路構成を実現することができる感度調整回路を提供する。

【解決手段】電圧供給回路101より電源電圧と電源電圧を分圧した電圧が出力され、電源電圧変動感度調整電圧を得ている。また、温度センサ111および基準電圧発生回路112より温度変動感度調整電圧を得ている。さらに、伝達関数が制御端子107、108の電位差に比例し、制御端子109、110の電位差に反比例する可変利得増幅回路104に、電源電圧変動感度調整電圧および温度変動感度調整電圧を与える回路構成にすることにより線形性を確保しながら小規模な回路構成を実現している。

(もっと読む)

AGC回路およびこれを用いた無線機、並びにAGC回路の制御方法

【課題】AGCアンプのゲイン特性の温度補正による誤差を低減でき、安定した温度補正ができるAGC回路を提供する。

【解決手段】直列状態で配列された複数のAGCアンプ12,13を備え、これら複数のAGCアンプ12,13の各ゲインを、共通のAGC電圧により並列に制御するAGC回路11において、AGC電圧に対する複数のAGCアンプ12,13からの出力特性がリニアとなるように、AGC電圧を補正するリニアリティ補正回路14を設ける。

(もっと読む)

可変利得反転増幅回路

【課題】入力抵抗周りの寄生容量による影響を抑制し、利得制御信号による利得の設定値に対する可変利得反転増幅回路の利得の線形性を維持して、利得が低い領域においても適切な利得制御を行うことが可能な可変利得反転増幅回路を実現する。

【解決手段】演算増幅器20の反転入力端子への入力信号Vinの供給を第1のスイッチ31のオン・オフ動作によって断続し、該断続におけるオン期間の比率によって可変利得反転増幅回路としての利得を制御する。演算増幅器20の入力抵抗13の一端側と第1のスイッチの一方の極側との接続点であるA点を、第1のスイッチ31のオン・オフ動作とは逆位相の関係でオン・オフ動作が制御される第2のスイッチ32およびボルテージフォロア回路34を介して、低インピーダンスの直流電圧源としての接地点に接続するようにして寄生容量による影響を抑制する。

(もっと読む)

自動利得制御回路

【課題】順方向電圧降下の温度特性による利得の変動を解消することができる自動利得制御回路を提供すること。

【解決手段】入力端子2から出力端子3に至る電気信号の利得を調整する自動利得調整回路1であって、制御信号と帰還信号との差分に応じた出力を行うオペアンプOP1と、オペアンプOP1の出力に応じた電源を入力端子2から出力端子3に供給するトランジスタTR1と、入力端子2から出力端子3に至る線路5に配置されたダイオードD3と、オペアンプOP1に対して帰還信号を入力する線路上に、トランジスタTR1及びダイオードD3の少なくとも一方の順方向電圧降下の温度特性変化を補償する温度補償用のダイオードD1、D2を配置した。

(もっと読む)

可変ゲイン増幅器およびD/A変換器

【課題】回路規模が小さく、同一回路でありながら任意の分解能のゲイン設定を可能とする。

【解決手段】2進コード「101」の場合、LSBは1なのでコンデンサC11に電荷CVinをサンプリングするとともに、コンデンサC10の電荷をゼロに初期化する(状態A)。コンデンサC10とC11との間で電荷の加算と分割とを同時に行う(状態B)。次のビットは0なので、コンデンサC11に電荷ゼロをサンプリングし(状態D)、その後、コンデンサC10とC11との間で電荷の加算と分割を同時に行う(状態B)。MSBは1なので、コンデンサC11に電荷CVinをサンプリングし(状態C)、その後、コンデンサC10とC11との間で電荷の加算と分割を同時に行う(状態B)。

(もっと読む)

半導体集積回路装置

【課題】本発明は、縦続接続された後段の増幅回路の評価を行うことができる半導体集積回路装置を提供することを目的とする。

【解決手段】縦続接続される複数の増幅回路を搭載した半導体集積回路装置において、複数の増幅回路11,12,13それぞれの間に設けられたスイッチ14,15と、スイッチ14,15のオン時に複数の増幅回路11,12,13の出力端子に接続される複数のモニタ用端子22,23,24を有し、スイッチ14,15それぞれに制御信号を供給してオン/オフ制御を行う。

(もっと読む)

回路ブレーカトリップユニットの電流利得制御

【課題】回路ブレーカ用電子トリップユニットを提供する。

【解決手段】回路ブレーカ用電子トリップユニット100は、各々が定格プラグ110用の指定の定格電流を示すように構成され、当該電子トリップユニット100用の定格電流を選択的に供給する複数のスイッチを備える当該定格プラグ110と、電力上昇すると当該定格プラグ110から選択された定格電流の値を受け、これを読み取る処理ユニット140と、複数の利得回路122を備える利得制御ユニット120とを有する。各々の当該利得回路122は、当該電子トリップユニット100の入力電流の利得を制御するために、選択された定格電流に基づいて当該処理ユニット140が設定する複数の利得スイッチを備える。

(もっと読む)

可変抵抗アレイ、増幅回路、及び電子機器

【課題】MOSトランジスタを製造するのに複雑かつ高度な製造プロセスが必要であった

。

【解決手段】直列接続されている複数の抵抗器と、複数のMOSトランジスタと、複数の

スイッチと、を含み、制御信号が、MOSトランジスタを導通にするオン電圧であるとき

、スイッチは、MOSトランジスタのバックゲートにソースの電圧を印加し、かつ、第i

のMOSトランジスタは、ゲートに印加されたオン電圧に応答して導通し、制御信号が、

第iのMOSトランジスタを遮断にするオフ電圧であるとき、スイッチは、MOSトラン

ジスタのバックゲートに基板電圧を印加し、かつ、MOSトランジスタは、ゲートに印加

されたオフ電圧に応答して遮断する。

(もっと読む)

1 - 20 / 56

[ Back to top ]