Fターム[5J106EE05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 検出回路 (618) | 電圧レベル検出 (164) | 入力レベル検出 (61)

Fターム[5J106EE05]の下位に属するFターム

入力信号断検出 (52)

Fターム[5J106EE05]に分類される特許

1 - 9 / 9

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、外部基準信号の検波における温度特性に応じて外部基準信号の入力レベルの適正範囲内を特定し、その適正範囲の内外に対して電圧制御発振器の制御電圧を制御して高安定な発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、温度センサ22と、固定電圧供給回路23と、外部基準同期モードとして位相比較器12とループフィルタ14を接続し、固定電圧モードとして固定電圧供給回路23とループフィルタ14を接続する選択スイッチ13と、検波回路17で検出された外部基準信号レベルの検波電圧が温度センサ22で検出された温度の温度特性に応じた適正範囲内であれば外部基準同期モードとし、適正範囲外であれば固定電圧モードとして選択スイッチ13を切り替えるCPU20とを有する発振周波数制御回路である。

(もっと読む)

電圧制御発振器及びこれを用いた位相同期回路

【課題】インバータセルを構成するMOSトランジスタが飽和領域のみならず、線形領域で動作する場合にも位相雑音を低減する。

【解決手段】ダミーインバータセル110からの信号と、基準信号との電位差を増幅した増幅信号を出力する演算増幅器120と;第2MOSトランジスタ102に接続され、増幅信号を受ける第1MOSトランジスタ101と、インバータ入力部及びインバータ出力部として機能する第2MOSトランジスタ102及び第3MOSトランジスタ103と、第3MOSトランジスタ103に接続され、発振信号の周波数を制御するための制御信号を受ける第4MOSトランジスタ104とを含むインバータセル100を環状に接続したリング・オシレータと;インバータセル100と同一の構造を備え、インバータ出力部がインバータ入力部に短絡されたダミーインバータ110と;を具備する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号に電圧制御発振部からの周波数信号を同期させて出力するPLL装置において、外部からの基準信号に不具合が生じても周波数の変動が抑えられるようにすること。

【解決手段】外部からの基準周波数信号の信号レベルを監視し、その信号レベルが設定範囲内であるときには、位相差データ作成手段により作成された位相差に関するデータを用いてPLL制御を行うが、前記信号レベルが設定外れたときには、信号の供給が停止あるいは異常が起きたものと認識して記憶部に記憶されている位相差に関するデータ、例えば蓄積している最新のデータあるいは予め作成しておいたデータに切り替えてPLL制御を行う。

(もっと読む)

クロック再生装置

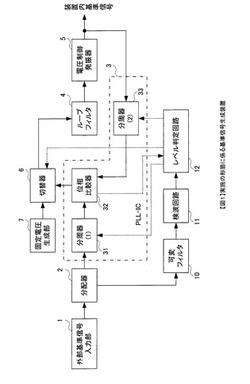

【課題】映像信号等の入力信号の劣化状況により、1次PLL回路と2次PLL回路の自走/ロック方法をフレキシブルに変更でき、劣化した入力信号に対しても、正常なクロック再生を可能とする。

【解決手段】1次PLL回路10及び2次PLL回路20を有する2段PLL回路において、1次PLL自走検出回路30は、入力信号の異常状態を検出して1次PLL回路10をアンロック状態に切り替えるための第1切替信号FD1を出力する。これにより、切替SW13が切り替えられ、定電圧発生器15から出力された定電圧がVCO14に与えられる。2次PLL自走検出回路40は、VCO14が自走状態で動作してしていることを検出して2次PLL回路20をアンロック状態に切り替えるための第2切替信号FD2を出力する。これにより、切替SW23が切り替えられ、定電圧発生器25から出力された定電圧がVCO24に与えられる。

(もっと読む)

1 - 9 / 9

[ Back to top ]