Fターム[5J106EE16]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 推測・予測回路 (10)

Fターム[5J106EE16]に分類される特許

1 - 10 / 10

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

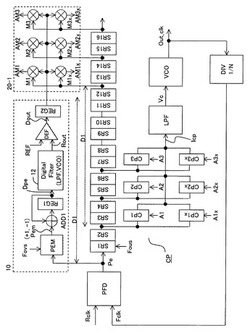

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

タイミング調整装置

【課題】温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

(もっと読む)

ADPLL周波数シンセサイザ

【課題】DCO利得正規化回路を用いることなく制御感度を適切に推定することで、デジタル制御発振器の発振周波数が変化しても位相雑音特性が変化しないADPLL周波数シンセサイザを提供する。

【解決手段】周波数設定ワードがFCW0からFCW2へ変更される場合、制御感度推定部12は、ダミーであるFCW1である時の発振周波数f1をまず測定し、次にFCW2である時の発振周波数f2を測定する。そして、制御感度推定部12は、発振周波数f1及びf2の値からFCW2時の制御感度KDCO2を計算する。ループフィルタ13は、制御感度KDCO2の値に基づいて、予め設計した固有周波数ωn及びダンピングファクタζとなるように、フィルタ係数α2及びρ2の値を決定する。

(もっと読む)

自動周波数制御回路

【課題】 自動周波数制御回路における検出部の起動および停止を簡単に制御し、消費電力を低減する。

【解決手段】 受信パケットから送信装置と受信装置との間のクロック周波数の誤差を検出し、その周波数誤差に対する補正値を出力する検出部と、検出部から出力された補正値に基づいて受信パケットの周波数誤差を補正する補正部とを備えた自動周波数制御回路において、検出部とは別のアルゴリズムで、受信パケットの周波数誤差の有無を簡易に判定し、周波数誤差があれば検出部を動作させ、周波数誤差がなければ検出部の動作を停止させ、検出部の動作時に出力した補正値を受信パケットの周波数誤差の補正に用いる制御を行う簡易判定部を備える。

(もっと読む)

PLL回路及びディスク装置

【課題】温度特性や経時変化がなく、線速度変化に合わせてループ特性をシームレスに補正できるPLL回路を提供する。

【解決手段】デジタルループフィルタ103は、位相比較器102が出力する位相誤差を入力し、デジタル周波数値を生成する。このデジタル周波数値は、D/A変換器104でアナログ電圧に変換され、VCO105は、D/A変換器104が出力する電圧に応じた周波数の同期クロックを出力する。位相比較器102が出力する位相誤差は、デジタルループフィルタ103の出力に所定の係数Aを乗じたものでゲイン補正され、デジタルループフィルタ103に入力される。デジタルループフィルタ103に入力する位相誤差を、出力クロック周波数に比例して変化させることで、PLLループ全体として、出力クロック周波数に依存して線形にループ特性が制御できる。

(もっと読む)

PLL回路

【課題】主回路と主回路を模擬するダミー回路とを有するPLL回路において、電流源の製造誤差に基づく、基準クロックと帰還クロックとの位相オフセットを低減する。

【解決手段】開示されるPLL回路は、位相比較器PFD14で基準クロックと帰還クロックとの位相を比較してUP信号又はDOWN信号を出力し、PFD14を模擬する位相比較器PFD11で2入力の基準クロックの位相を比較してダミーUP信号又はダミーDOWN信号を出力して、UP信号又はダミーUP信号で流し込み側の電流源23Aを選択し、DOWN信号又はダミーDOWN信号で引き抜き側の電流源23Bを選択する。主回路のチャージポンプ(CP)の出力電圧とダミー回路のダミーCPの出力電圧との差分に応じて、電流源23A,23Bを制御してCP又はダミーCPを充放電して出力電圧を変化させるが、電流源23A,23Bは、CPの充放電に使用しない期間に、ダミーCPの充放電に使用される。

(もっと読む)

クロック回復方法、記憶媒体を読出すためのドライブ、およびクロック回復回路

【課題】クロック/データ信号におけるクロック回復を改善するための方法、回路、およびドライブを提供する。

【解決手段】ロックループ回路、たとえばPLLにタイミング基準が提供される。このタイミング基準は、回復されているクロックの周波数の期待値に基づいて更新される。回復されている各クロックまで追従させたシステムクロックが出力される。各システムクロックの現在の周波数が見積られ、1つ以上のシステムクロックの見積られた現在の周波数に基づき、期待値が更新される。データストリームが一連のブロックに分離されるデータを含む場合、更新は、ブロックの終端の後、および、後続のブロックの開始部の前に行なわれ得る。見積りは、各ブロックに対して定期的におよび/または複数回行なわれ得る。

(もっと読む)

1 - 10 / 10

[ Back to top ]