Fターム[5J106QQ10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、機能 (379) | 誤動作の防止、同期回復 (23)

Fターム[5J106QQ10]に分類される特許

1 - 20 / 23

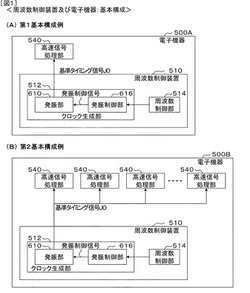

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

周波数シンセサイザ装置及びその製造システム

【課題】 多数の類似機種を製造する場合でも、製造工程や検査工程における人為的なミスをなくし、適正な仕様とすることができる周波数シンセサイザ装置及びその製造システムを提供する。

【解決手段】 周波数シンセサイザ装置1のハードウェア識別子回路13が機種に対応するハードウェア識別子を記憶し、外部PC2が複数のハードウェア識別子とそれに対応するパラメータを記憶しており、マイクロコントローラ12が、外部PC2からハードウェア識別子の要求を受信すると、ハードウェア識別子回路13からハードウェア識別子を読み取って外部PC2に出力し、外部PC2が、周波数シンセサイザ装置1から取得したハードウェア識別子に対応して記憶されているパラメータを読み取って周波数シンセサイザ装置1に出力し、マイクロコントローラ12が、受信したパラメータを不揮発性メモリ14に記憶する周波数シンセサイザ装置及びその製造システムとしている。

(もっと読む)

基準周波数発生装置

【課題】長時間にわたって基準周波数周波数の周波数安定度を維持可能で、かつ安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置1は、ルビジウム発振器11と、ルビジウム発振器11より周波数安定度が低い水晶発振器21と、判定部42と、切替スイッチ51a〜51fと、を備える。判定部42は、ルビジウム発振器11が正常な出力信号を出力している正常状態か、正常な出力信号を出力していない故障状態か、を判定する。切替スイッチ51c,51dは、ルビジウム発振器11が正常状態であると判定部42が判定しているときは、第1PLL回路を構成するように設定を行い、ルビジウム発振器11が故障状態であると判定部42が判定しているときは、第2PLL回路を構成するように設定を行う。

(もっと読む)

基準周波数発生装置

【課題】比較器が出力する追従誤差に応じて適切な制御を行い、外乱の影響によっても基準周波数信号の精度が低下しない構成の基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、電圧制御発振器と、位相比較器と、制御器と、ファジィ補償器と、を備える。電圧制御発振器は、基準周波数信号を出力する。位相比較器は、基準周波数信号を分周した信号と、リファレンス信号と、を比較して位相差を算出する。制御器は、位相差を考慮して制御電圧信号を電圧制御発振器に出力する。ファジィ補償器は、位相差が急激な変動をしているか否かを、ファジィ理論を用いて判定する。そして、ファジィ補償器は、位相差が急激な変動をしていると判定した場合は、当該位相差が基準周波数信号に影響を及ぼさないように補償値を決定する。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

周波数変調機能付きクロック生成回路

【課題】良好なスペクトラム拡散効果を有し、ノイズの発生が少なく周辺回路や電子部品の誤動作を低減することができる周波数変調機能付きクロック生成回路を提供する。

【解決手段】クロック生成回路1は、帰還用分周器17を有し、周波数変調されたクロックを出力するPLL回路10と、帰還用分周器17から所定の周波数のみ取り出しPLL回路10に入力するバンドパスフィルタ20と、三角波を生成する三角波生成回路40とを有し、バンドパスフィルタ20は、サイン波生成器としても機能し、所定のタイミングでサイン波を生成して三角波と合成して帰還用分周器17の分周比を変化させる。

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

シンセサイザ装置及びこれを備える携帯通信端末

【課題】デュアルシンセサイザ装置において、基板の定在波比が劣化しても、簡単な構成でアイソレーションの低下を防止する。

【解決手段】プリント基板13上には第1及び第のPLLシンセサイザ部11及び12が配置され、第1及び第2のPLLシンセサイザ部には基板に形成された配線パターン13aを介して基準発振器14から基準信号が与えられ、選択スイッチ(SW)45によって第1及び第2のPLLシンセサイザ部からの出力信号のうちいずれか一方が選択される。配線パターンのインダクタンスとこのインダクタンスと対向するアースパターンからなる第1及び第2のコンデンサとによってローパスフィルタが構成される。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

シンセサイザモジュール

【課題】PLL回路用接地パターン領域7と広域接地パターン11間に基準信号除去用フィルタ4を接続し、電圧制御発振器1への基準信号の回り込みをなくしたシンセサイザモジュールを提供する。

【解決手段】絶縁基板5上面に、電圧制御発振器1及びPLL回路2を装着すると共に電圧制御発振器用接地パターン領域6及びPLL回路用接地パターン領域7を形成し、絶縁基板5下面に広域接地パターン11を形成したもので、絶縁基板5上面にさらにPLL回路の基準信号除去用フィルタ4を装着し、フィルタ用接地パターン領域10を形成し、フィルタ4をPLL回路用接地パターン領域7とフィルタ用接地パターン領域10間に接続し、フィルタ用接地パターン領域10を広域接地パターン11に導電接続した。

(もっと読む)

PLL回路

【課題】直列接続されたPLL回路について、特にリセット時や電源投入時における異常なクロック信号の発生を抑制する。

【解決手段】直列接続された二つのPLL回路(10A,20)からなるPLL回路において、前段のPLL回路(10A)は、出力クロック信号を生成する電圧制御発振器(104)、及び電圧制御発振器(104)に入力される制御電圧が所定の範囲にあるか否かを検出し、当該検出結果を示す検出信号を出力する制御電圧検出回路(106)を備えている。後段のPLL回路(20)は、前段のPLL回路(10A)から出力された検出信号が第1の論理レベルのとき、停止する一方、当該検出信号が第2の論理レベルのとき、動作する。

(もっと読む)

周波数シンセサイザ

【課題】第1の周波数の信号を生成する第1の信号生成回路と、第1の周波数と異なる周波数である第2の周波数の信号を生成する第2の信号生成回路と、の相互干渉を抑制した周波数シンセサイザを実現する。

【解決手段】第1の周波数の信号を生成する第1の信号生成回路と、第1の周波数と異なる周波数である第2の周波数の信号を生成する第2の信号生成回路と、を備え、第1の周波数の信号と第2の周波数の信号のうち、いずれかを出力する周波数シンセサイザであって、第1の信号生成回路は、第1の周波数のN倍(Nは、正の整数)の周波数でPLL発振し、これを1/N倍で分周することにより、第1の周波数の信号を生成し、第2の信号生成回路は、第2の周波数のM倍(Mは、Nよりも大きく、Nで割った値が自然数にならない整数)の周波数でPLL発振し、これを1/M倍で分周することにより、第2の周波数の信号を生成する。

(もっと読む)

局部発振回路、携帯情報端末および局部発振制御方法

【課題】 TDMA/TDDのスロット可変型通信における周波数の変動を防止する。

【解決手段】 2系統のPLL回路をそれぞれ有する第1の集積回路(40a)および第2の集積回路(40b)と、基準発振回路(30)と、2系統の周波数帯域の信号を出力する出力回路(50,60)とを備える。互いに同一系統となる2つの第1PLL回路(70A,70B)は、該各PLL回路をフレーム期間中の異なるタイムスロットにて動作させるための制御信号が供給される信号線(70AC,70BC)と出力回路とに接続される。第1の集積回路の第2PLL回路(80A)は、該PLL回路を上記タイムスロットの双方にて動作させるための制御信号が供給される信号線(80AC)と出力回路とに接続される。第2の集積回路の第2PLL回路(80B)は、出力回路には接続されず、第1の集積回路のPLL回路が接続された信号線(70AC,80AC)のうちのいずれかと接続される。

(もっと読む)

通信用半導体集積回路

【課題】所定の周波数の局部発振信号を発生する発振器を含むPLL回路を内蔵し、温度が変化してVCOの発振周波数が変動してもPLLループのロックがはずれにくい高周波ICを提供する。

【解決手段】発振周波数帯を切り替え可能なVCO11と可変分周回路12と位相比較回路15とループフィルタ17とを含み、ループフィルタとVCOとの間を切り離した開ループ状態で、複数の所定の固定電圧のいずれかをVCOへ印加する切替えスイッチと、所定の周波数の基準信号に対する可変分周回路の出力の位相の進みまたは遅れを判別する判別回路22と、判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド切り替え回路23とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけ、さらにVCOへ印加する固定電圧を2分探査方式で切り替え最適な印加電圧を見つけPLLループをロックさせる。

(もっと読む)

2パイ・スリップ検出を用いて位相同期ループ(PLL)シンセサイザを粗調整するためのシステムおよび方法

VCOの周波数と基準周波数との間の位相差を決定し、VCOの周波数と基準周波数との位相差が2πラジアン以上の場合に誤差信号を出力する位相周波数検出器(PFD)を有する位相同期ループ(PLL)シンセサイザ(200)において、少なくとも1つの電圧制御発振器(VCO)(211)を粗調整するためのシステムに関する。続いて、PFDに生成された誤差信号の数を追従するために、監視装置(215)が用いられる。監視装置の回路が所定のレベルに到達する場合、VCOの自走周波数が粗調整され得る。本発明によって、回路の動作に影響を与える動作因子にかかわらずPLLのVCOが動作レンジに留まることが可能なようにPLLを粗調整することを可能とする、大きな利点が示される。  (もっと読む)

(もっと読む)

PLLシンセサイザ

【課題】 信号純度を低下させることなく、誤差信号の極性を反転させる際のロック外れを起こさないようにする。

【解決手段】 VCO11の自走発振周波数をローカル信号Bの周波数より高い第1の周波数領域内にするために必要な第1のオフセット電圧V1と、ローカル信号Bの周波数より低い第2の周波数領域内にするために必要な第2のオフセット電圧V2のうち、周波数領域を切り替える際に、その切り替える方の周波数領域に対応したオフセット電圧を選択してVCO11に一時的に印加する。

(もっと読む)

周波数変調回路

【課題】多チャネルPLLシンセサイザでの低域周波数の周波数変調において逆変調が発生しないとともに、連続スロットにおいても所定の周波数を保持することのできる周波数変調回路を提供することを目的とする。

【解決手段】所定の基準周波数の信号を発生する基準発振器3と、制御電圧に基く周波数である制御電圧周波数を出力する電圧制御型発振器1と、基準周波数の信号と制御電圧周波数を分周した分周周波数の信号との位相差を示す位相比較電圧としての制御電圧a、bを出力する位相比較回路5と、制御電圧を保持する保持回路(9、10、11)とを有する。これにより、多チャネルPLLシンセサイザにおける低域周波数の変調において逆変調を防止することができる。

(もっと読む)

周波数分割器を有する装置

セクション(21−27)を有する周波数分割器(2)は、調整信号(p,,)に依存して、かつ、後のセクションから生じる制御信号(c,,)に依存して、調整可能な数によって、周波数信号(f,,)を分割する第1種の基本セクション(21、22、23)を備えており、付加的な回路55、56、64、66、67を有する第2種の高度なセクション(22)を備えている。この付加的な回路55、56、64、66、67は、限られた数の早いセクションに対して実施されるべき何らかの変調を可能にし、後のセクションは影響を受けない。結果として、周波数分割器(2)は、例えば、いかなる変調も適応化される必要なしに、アクティブ及び非アクティブモードを有するプログラム可能なセクション(26、27)によって拡張されることができる。これに対し、回路55、56、64、66、67は、変調信号(mo、ml)及び付加的な制御信号(c3)を受け取る。前記のような周波数分割器(2)は、コストが低く、信頼でき、ロバスト性を有し、容易に実施化されることができる。  (もっと読む)

(もっと読む)

PLL回路、復調回路、ICカード及びICカード処理装置

本発明は、所望の伝送系を介して伝送された入力信号より、入力信号を介して伝送されるデータ列を再生する復調回路であり、発振器(252)及び可変型分周器(253)により生成される第1の発振出力信号及び第1の発振出力信号に対して90度[π/2]位相の異なる第2の発振出力信号をイクスクルーシブオア(EX−OR)回路(254Q)(254I)により位相比較し、その位相比較結果の正負に基づいて制御方向判定回路(257)により制御方向を判定し、その制御方向判定結果を積算回路(258)により入力信号の1周期分積算して、その積算結果に対し、補正回路(259)により、位相比較結果に基づいて位相差が[±π/2]の場合に所定の制御量とする補正処理を行い、1周期に1回に出力される補正処理済みの制御信号により可変型分周器(253)の動作を制御する。 (もっと読む)

1 - 20 / 23

[ Back to top ]