Fターム[5J500AF06]の内容

Fターム[5J500AF06]に分類される特許

1 - 20 / 29

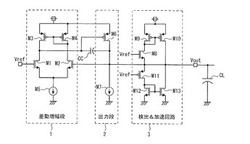

定電圧バッファ回路

【課題】スタートアップ時などに、演算増幅回路の出力電圧が、駆動能力の高い側とは反対方向に大きくずれた場合においても、出力段の定電流源に制限されることなく、所定電圧へのセットリングを加速することが可能な定電圧バッファ回路を提供すること。

【解決手段】基準電圧(Vref)をバッファし、一定電圧の出力電圧(Vout)を供給する定電圧バッファ回路であって、出力電圧と基準電圧とを取得する差動増幅器(1)と、差動増幅器(1)の出力信号に応じて制御されるP型駆動の出力手段(2)と、出力電圧が基準電圧よりも大きいことを検出する検出手段(M11)と、検出手段(M11)において、出力電圧が基準電圧に対して大きいことが検出された場合には、出力ノードから電流を引き出すように電流を制御する電流制御手段(3)とを有する定電圧バッファ回路。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

増幅回路

【課題】 動作が制限されることのない増幅回路を提供する。

【解決手段】 増幅回路1において、初段増幅回路10は、反転入力端子41に入力される入力信号61と、非反転入力端子42に入力される入力信号62とを増幅して初段増幅信号を出力する。第5トランジスタのコレクタ電流は、正電源の電位と第1コレクタ抵抗の抵抗値とに基づいて決定される。第6トランジスタのコレクタ電流は、負電源の電位と第2コレクタ抵抗の抵抗値とに基づいて決定される。このため、従来の差動増幅回路に比べて、第5トランジスタ及び第6トランジスタのコレクタ電流の上限値が大幅に緩和される。第5トランジスタ及び第6トランジスタのコレクタ電流が第1入力信号及び第2入力信号に応じて変化するときに、各コレクタ電流の波形が歪むことを防止できる。

(もっと読む)

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

抵抗の誤差訂正を用いるコンパレータベースのバッファ

【課題】スイッチトキャパシタの負荷を有する高利得増幅器の駆動容量を高めるコンパレータベースのバッファ方法及びシステムを提供することを目的とする。

【解決手段】電流源と、コンパレータと、スイッチと、サンプリングキャパシタと、オーバーシュート訂正抵抗を含む。充電経路内の抵抗及び訂正位相を使用する訂正の解決法は、電力消費を制約し、コンポーネントを最小化する一方で、出力電圧のオーバーシュートを低減する。Spectre(登録商標)シミュレーションは、本発明の効果を確証する。

(もっと読む)

演算増幅器

【課題】従来回路に比して極力少ない回路素子の追加によって入力換算雑音電圧を増加させることなく、従来回路同様の回路安定性を保持したまま、スルーレートの増大を図る。

【解決手段】入力電圧が低電位から高電位に遷移する際、及び、高電位から低電位に遷移する際にのみ、一時的に位相補償用コンデンサ61に電流を追加供給可能とした電流供給回路100A,100B,100Cが設けられ、回路動作の安定性を損なうことなく、スルーレートの増大が可能となっている。

(もっと読む)

演算増幅器

【課題】全ての位相補償容量に対して充放電の加速電流を供給することでスルーレートを増大させた演算増幅器を提供する。

【解決手段】ゲートが正転入力端子IN+に接続されたトランジスタ11a、ゲートが反転入力端子IN−に接続されたトランジスタ11b、トランジスタ11a,11bのソースに共通接続された電流源CS1、及びトランジスタ11a、11bのドレインに接続された負荷を有する第1の差動回路11と、該第1の差動回路11の正転出力信号を増幅する1又は2段以上縦続接続された増幅器121〜12nと、増幅器121〜12nの入力側と出力端子OUTの間に接続された位相補償容量CC1〜CCnとを備えた演算増幅器において、正転入力端子IN+の電圧が反転入力端子IN-の電圧よりもVdif1より高くなると位相補償容量CC1〜CCnに対し放電電流を追加し、Vdif3より低くなると充電電流を追加する電流制御部13を備えた。

(もっと読む)

スイッチング回路、分布定数型のスイッチング回路、及び包絡線信号増幅器

【課題】単一のスイッチング素子でインンダクタンス素子をスイッチングすることにより、半導体材料がシリコン又はガリウム砒素からなるスイッチング素子を用いたプッシュプルの増幅器よりも高周波且つ大電力の増幅が可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】スイッチング回路33aは、炭化珪素(SiC)を半導体材料とするn個のトランジスタ(FET)M1,M2,・・MnのゲートをコイルL1を介して縦続接続する入力側伝送線路と、各トランジスタM1,M2,・・MnのドレインをコイルL2を介して縦続接続する出力側伝送線路とを備える。入力端331から与えられて入力側伝送線路を伝播するPWM信号によってトランジスタMm(mは1からnまでの整数)を順次オンさせ、トランジスタMmのドレインに流入する電流と、出力側伝送線路を出力端332の方向に伝播する電流とを加算する。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

インピーダンス整合装置

【課題】メンテナンス時期を予知することができるインピーダンス整合装置を提供する。

【解決手段】可変インピーダンス素子3a、3bと、モータ7a,7bを駆動源として可変インピーダンス素子の操作軸を操作する操作機構と、操作軸の目標位置を設定する目標位置設定部9と、検出された操作軸の位置を設定された目標位置に一致させるようにモータを制御するモータ制御部18と、操作軸の目標位置と現在位置との間に存在する残留偏差が許容値を超えたときに異常判定を行う異常判定部12とを備える。異常判定回数が設定された判定値未満である間は残留偏差の許容値を初期許容値とするとともにモータの出力トルクを初期トルクとし、異常判定回数が判定値に達した後は、残留偏差の許容値を初期許容値よりも大きい異常検出後許容値に切り替えるとともに、モータの出力トルクを初期トルクよりも大きい異常検出後トルクとする。

(もっと読む)

電気増幅回路

【課題】特許文献1の電気増幅回路は、ゲインが中程度で、NFB回路もなかった。

【解決手段】コンデンサをFETのソースとバイポーラトランジスタのベースとの間に接続し、さらにNチャンネル、PチャンネルのFETのソース間に抵抗を接続し、さらに出力段から抵抗を介してFETのソースにNFBをかけることで、ゲインが非常に大きくでき(現在2000倍(66db)を実証済であるが、今後さらに大きくできる可能性がある。)、電気増幅回路としての特性も向上させることができる。

(もっと読む)

スタートアップ回路

【課題】必要とするキャパシタの数を削減し、且つ電源電圧が低下しても基準電圧回路から出力する基準電圧の変動を防止できるようにする。

【解決手段】電源投入時に定電流回路10に起動電流を供給するキャパシタC1と、該キャパシタC1に流れる起動電流を入力しそのミラー電流が出力するカレントミラー回路(MN31,MN32)とを設ける。そして、該カレントミラー回路の出力電流を基準電圧回路20に起動電流として供給する。

(もっと読む)

電源回路

【課題】広帯域な包絡線信号を高効率に増幅することができる電源回路を提供する。

【解決手段】電源回路102の入力信号を増幅する線形増幅器9と、線形増幅器9の出力端子に一端が接続され他端が電源回路102の出力に接続された抵抗10と、抵抗10によって生じる電圧を入力するヒステリシスコンパレータ6と、ヒステリシスコンパレータ6が生成した信号を入力する第1のデジタルアンプ2と、電源回路102の入力信号または線形増幅器9の出力信号を入力し、所定の倍率に増幅して出力する増幅器33と、三角波を生成する三角波生成手段13と、増幅器33と三角波生成手段13からの信号を比較するコンパレータ32と、コンパレータ32の出力信号を増幅して出力する第2のデジタルアンプ7と、で構成された電源回路102において、第2のデジタルアンプ7の出力を第1のデジタルアンプ2の電源として供給することで線形増幅器9を高効率動作させる。

(もっと読む)

電圧振幅回路

【課題】アイドリング電流以上の電流を出力することができる電圧振幅回路を提供する。

【解決手段】ローサイドスイッチ素子Q1とハイサイドスイッチ素子Q2を備え、電圧を振幅させて電流を出力する電圧振幅回路であって、前記ローサイドスイッチ素子の制御端子にのみ駆動電源VG1を接続し、前記ローサイドスイッチ素子の入力端子と前記ハイサイドスイッチ素子の制御端子とを接続するとともに、前記ローサイドスイッチ素子の入力端子と前記ハイサイドスイッチ素子の出力端子間にダイオードD1を接続し、このダイオードのアノードを負荷Ro,Co及び前記ハイサイドスイッチ素子の出力端子に接続し、このダイオードのカソードを前記ローサイドスイッチ素子の入力端子に接続してある電圧振幅回路。

(もっと読む)

電力増幅器並列システム

【課題】 各電力増幅器の特性間の合致に対する制約が小さく、並列数の増減などに容易に対応し得る電力増幅器並列システムを提供する。

【解決手段】 本発明の電力増幅器並列システムは、増幅対象の電圧信号と、電圧フィードバック信号とを入力し、位相補償を行いつつ増幅する電圧制御部と、電圧制御部から出力された電圧信号を入力信号として電力増幅する、電流出力のディジタル電力増幅器でなる、複数の電圧制御電流源と、各電圧制御電流源からの出力電流を1つの節点で合成して負荷に電力を供給する電流合成部と、この節点の電圧を所定の帰還率で電圧制御部にフィードバックする電圧フィードバック部とを備える。電圧制御電流源の中に、動作電源として、エコエネルギー源による電源を動作電源とするものも混在させることが好ましい。

(もっと読む)

FET増幅回路

【課題】FET増幅素子のスイッチング速度をより高速化したFET増幅回路を実現する。

【解決手段】FET増幅回路10は、バイアス急昇圧回路6と、バイアス急降圧回路7と、を備える。バイアス急昇圧回路6は、FET増幅素子1のゲート側に接続されたバイアス抵抗2の端子と所定の電源Vccとの間に直列に接続されたキャパシタ62と、スイッチングFET61と、を含み、制御信号SCTRがオンのときにスイッチングFET61がオンし、これにより所定の電源Vccからバイアス抵抗2に過渡電流を流してFET増幅素子1のゲートソース間のバイアス電圧を急激に昇圧させる。また、バイアス急降圧回路7は、バイアス抵抗2に並列に接続されたスイッチングFET71を含み、制御信号SCTRがオフのときにスイッチングFET71がオンし、これによりFET増幅素子1のゲートソース間のバイアス電圧を急激に降圧させる。

(もっと読む)

演算増幅器

【課題】入力差動電圧が所定値を超えるとき、スルーレートを加速させてパルス応答速度をさらに高速化させる。

【解決手段】正転入力端子IN+および反転入力端子IN−に接続された差動入力回路(Q1,Q2,I1〜I3)と、該差動入力回路の正転入力端子と反転入力端子に入力する入力差動電圧の極性と大きさに応じた電流の吐き出し/吸い込みを行う出力回路(Q3〜Q6,R1,R2,V1)と、該出力回路の電流吐き出し/電流吸い込みに応じて充電/放電が行われるコンデンサCcとを備える。これに、正転入力端子IN+の電圧が反転入力端子IN−の電圧より所定値以上高くなると、コンデンサCcに対して追加の吐き出し電流を供給する吐き出し電流追加回路(QA2,QA3,QA5,QA7)と、正転入力端子IN+の電圧が反転入力端子IN−の電圧より所定値以上低くなると、コンデンサCcに対して追加の吸い込み電流を供給する吸い込み電流追加回路(QA1,QA4,QA6,QA8)とを設ける。

(もっと読む)

D級アンプ

【課題】必要なS/Nを保持したまま十分に幅広いゲイン調整を行うことができるD級アンプを提供する。

【解決手段】デジタル信号処理回路1と、デジタル信号処理回路1の出力に接続されるD級出力段2と、D級出力段2から出力される信号を平滑する出力フィルタ4と、D級出力段2に接続されるアナログゲイン調整回路3とを備え、アナログゲイン調整回路3からD級出力段2に供給する電流量を調整することにより、D級出力段2のD級増幅ゲインを調整する。

(もっと読む)

差動増幅回路

【課題】出力段のアイドリング電流の増加を招くことなく、負荷電流能力の向上を図る。

【解決手段】

第1のトランジスタ1と第10のトランジスタ10のベース電流を相殺するアイドルベース電流キャンセル部102において、第6及び第7のトランジスタ6,7より構成されたプッシュプル出力段106の第7のトランジスタ7にシンク電流が流れる際に余剰電流となる第10のトランジスタ10のコレクタ電流が、補充電流供給部104の作用により第7のトランジスタ7のベースに供給されて、出力電流能力の向上が図られるものとなっている。

(もっと読む)

差動演算増幅器

【課題】ダイナミックな(動的な)動作時の負荷への十分な電流供給と、スタティックな(静的な)動作時の消費電力の低減と、オフセットの低減と、歪みの低減とが可能な差動演算増幅器を提供する。

【解決手段】差動トランジスタ対10の一方の出力信号を正極性側の電流電圧変換回路20を介して制御端子で受ける正極性側の出力トランジスタ50、60を設け、差動トランジスタ対10の他方の出力信号を負極性側の電流電圧変換回路30を介して制御端子で受ける負極性側の出力トランジスタ70,80を設ける。出力トランジスタ50,70はA級増幅動作域で動作し、出力トランジスタ60,80はB級増幅動作域で動作する。

(もっと読む)

1 - 20 / 29

[ Back to top ]