Fターム[5J500DN25]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | エミッタ(ソース)回路構成 (671) | エミッタ(ソース)帰還抵抗を具備するもの (43)

Fターム[5J500DN25]の下位に属するFターム

Fターム[5J500DN25]に分類される特許

1 - 20 / 42

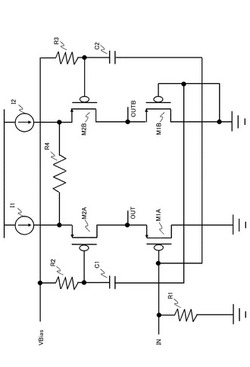

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

金属検出システム作動方法及び金属検出システム

【課題】2つ以上の送信周波数を使用する金属検出システムを提供する。

【解決手段】少なくとも2つの送信周波数グループから選択される送信周波数を有する送信信号を生成する送信装置3と接続される送信コイル4と、受信装置5に含まれる少なくとも1つの増幅装置14,15の信号入力へ出力信号を提供し、出力信号が、システムが平衡状態にあるように相互に相殺する第1及び第2の受信コイル6,7とを備えた、平衡コイルシステムを含む金属検出システム1を作動させる。制御装置16が、少なくとも1つの増幅装置14,15の信号入力と接続される少なくとも1つの制御可能インピーダンス装置12,13の制御入力に提供される制御信号を送信装置3の送信周波数に従って生成し、送信周波数が増減されるとき、インピーダンス値が増減されるような方法で制御信号が、制御可能インピーダンス装置12,13のインピーダンス値を制御する。

(もっと読む)

広帯域アナログ無線周波数を処理する構成要素

【課題】製造及び動作が簡単で、大きい帯域幅で動作することができる、プログラマブルデバイスを提供する。

【解決手段】積分器は、第1の電圧供給端子と第2の電圧供給端子との間に直列接続された、一対のpチャネルトランジスタ、一対の可変抵抗手段、および一対のnチャネルトランジスタを備える。pチャネルトランジスタのドレインが可変抵抗手段のドレインに電流を供給し、可変抵抗手段のソースがnチャネルトランジスタのドレインに電流を供給する。pチャネルトランジスタのゲートは、可変抵抗手段において反対側のトランジスタのドレインに対し、フィードフォワード形態で接続されてもよい。一対のnチャネルトランジスタのゲートに印加された相補的な入力信号によって駆動された積分器は、pチャネルトランジスタと可変抵抗手段との間のノードに相補的な出力を生成する。

(もっと読む)

利得可変回路

【課題】利得制御信号の分配配線を簡素化し、回路の高周波化・広帯域化を実現し、負方向の利得可変幅を増大させる。

【解決手段】利得可変回路は、入力信号Inを増幅する可変利得増幅器(VGA)1と、VGA1の出力信号Out1を増幅する固定利得増幅器(Amp)2と、Amp2の出力信号Out2の振幅を検出して、検出した振幅と予め設定された振幅設定値とが等しくなるようにVGA1の利得を制御する自動利得調整回路(AGC)3とを備える。VGA1は、ギルバートセル型の可変利得増幅器である。

(もっと読む)

ゲイン切り替え回路

【課題】信号の広帯域化を図る。

【解決手段】入力信号に対し、それぞれ所望の減衰量を設定可能なゲイン切り替え部GCk(k=1〜n、nは2以上の整数)と、ゲイン切り替え部GCkの出力をそれぞれ入力に接続し、出力を共通に接続する入力差動対TXkと、それぞれのゲイン切り替え部GCkの減衰量及びそれぞれの入力差動対TXkの活性化を制御するスイッチ制御回路103と、を備え、ゲイン切り替え部GCkは、入力信号を一端に受け、他端を入力差動対TXkの入力端に接続する抵抗素子RPkAと、スイッチ制御回路103によってオンオフが制御されるスイッチ素子SWPkj(j=1〜m、mは2以上の整数)と、一端を抵抗素子RPkAの他端に接続し、他端をそれぞれスイッチ素子SWPkjを介して基準電圧VREFに接続する抵抗素子群PRkと、を備える。

(もっと読む)

サンプルホールド回路及びフィードスルー抑制方法

【課題】入力段差動増幅回路を停止させることなくフィードスルーの抑制が可能なサンプルホールド回路を提供する。

【解決手段】入力差動対10は、差動信号である入力信号IN、INBを所定の増幅率で増幅する。ホールド回路20は、入力差動対10の一方の出力端に接続され、サンプリングクロック信号に基づいて、サンプル動作と、ホールド動作とを行う。出力バッファ30は、ホールド回路20の出力をバッファリングする。補正回路40は、ホールド動作時に、ホールド回路20で生じるフィードスルーと逆相のフィードスルーを発生する。補正回路は、発生したフィードスルーを、出力バッファ30の出力に加える。

(もっと読む)

差動増幅器

【課題】非直線性誤差が少なく広帯域であって、自在にゲインの切り替えを行うことができる差動増幅器を提供する。

【解決手段】差動増幅器1は一対の入力信号が入力されて、その差分に応じた差分を有する一対の信号を出力する入力回路(Q1,Q2、Q5,Q6、RE1,RE2)と、入力回路から出力される一対の信号を用いて入力回路で生ずる歪みを補償する補償回路(Q3,Q4)とを含む入力部11と、入力回路に対して行われる補償回路の歪み補償によって歪みが補償されるとともに入力回路から出力される一対の信号を増幅する複数の増幅回路12a,12bを含む出力部12と、複数の増幅回路12a,12bのうち、動作状態にする増幅回路と非動作状態にする増幅回路との切り替え制御を行う制御回路20とを備える。

(もっと読む)

カレントモードロジックバッファ回路

【課題】回路面積を小さく抑えたまま、入力が開放された状態にあっても、出力からの出力信号の発振の防止が図られたカレントモードロジックバッファ回路を提供する。

【解決手段】ゲートに差動信号の入力を受けドレインから差動信号を出力する一対のMOSトランジスタ1及びMOSトランジスタ2と、MOSトランジスタ2のソースに一端が接続された抵抗15と、MOSトランジスタ1のソースに直接に接続されるとともに抵抗15の他端にドレインが接続されたMOSトランジスタ3とを備えた。

(もっと読む)

演算増幅回路及び表示装置

【課題】回路面積の増加を抑制しつつ、出力電圧バラツキを低減できる演算増幅回路を提供する。

【解決手段】本発明に係る演算増幅回路122Aは差動増幅部31を含む。差動増幅部31は、第1差動対を形成する差動トランジスタ100及び差動トランジスタ101と、第1差動対に電流を供給する電流源トランジスタ102とを含む。演算増幅回路122Aは、さらに、差動トランジスタ100及び差動トランジスタ101の少なくとも一方と、電流源トランジスタ102のドレインとの間に接続された可変抵抗素子21を備える。可変抵抗素子21は、第1端子及び第2端子と、直列に接続された複数の電流電圧変換器41と、第1端子と第2端子との間に接続される直列に接続された複数の電流電圧変換器41の段数を変更することにより、第1端子と第2端子との間の抵抗値を変更する補正電圧選択回路51とを備える。

(もっと読む)

アクティブインダクタおよび差動アンプ回路

【課題】低電源電圧下においても、半導体集積回路上での面積および消費電力の増大を抑えつつ、高域での利得のピーキングの傾きを急峻化する。

【解決手段】P型電界効果トランジスタM1のソースを電源電位VDDに接続し、P型電界効果トランジスタM1のドレインを出力端子outに接続し、N型電界効果トランジスタM2のドレインを電源電位VDDに接続し、N型電界効果トランジスタM2のソースを電流源IBを介して接地電位に接続し、P型電界効果トランジスタM1のゲートをN型電界効果トランジスタM2のソースに接続し、N型電界効果トランジスタM2のゲートを抵抗素子Rpを介してP型電界効果トランジスタM1のドレインに接続する。

(もっと読む)

差動増幅器

【課題】 0でない差動信号が長時間印加されると、差動入力信号が入力される一対のトランジスタの自己発熱がアンバランスになり、オフセット電圧が発生してしまうという課題を解決する。

【解決手段】 差動入力信号が入力される第1のエミッタフォロアと、前記差動入力信号に関連する差動信号が逆極性で入力される差動対を直列に接続し、この第1のエミッタフォロアの出力をメインアンプで増幅して出力するようにした。特定の式を満足するように回路定数が設定すると、自己発熱によるオフセット電圧を0にすることができる。

(もっと読む)

差動増幅回路

【課題】 差動入力信号の電圧範囲に依存しない電圧範囲で出力信号を出力することができる簡易な回路構成の差動増幅回路を提供すること。

【解決手段】 差動増幅回路1は、差動入力電圧が入力される第1差動対をなすNMOSトランジスタN1、N2と、NMOSトランジスタN1、N2のドレイン端子間X1、X2と接続する抵抗素子Raと、ドレイン端子X1、X2が、入力端子に接続されるオペアンプOPと、オペアンプOPの出力電圧および基準電圧が入力される第2差動対をなすNMOSトランジスタN3、N4とを備えている。第1差動対のドレイン端子および第2差動対のドレイン端子はそれぞれ接続されている。

(もっと読む)

差動増幅器

【課題】大きな入力電圧において出力信号の歪が少く、かつ高速動作が可能なこと。

【解決手段】ベース端子に入力信号が印加されると共にコレクタ端子が出力端とされる一対の第1エミッタフォロワ・トランジスタと、ベース端子が第1エミッタフォロワ・トランジスタのエミッタ端子にそれぞれ接続される一対の第2エミッタフォロワ・トランジスタと、ベース端子が第2エミッタフォロワ・トランジスタのエミッタ端子にたすきがけ接続されると共にコレクタ端子が第1エミッタフォロワ・トランジスタのエミッタ端子にそれぞれ接続される一対の増幅トランジスタと、一端が増幅トランジスタのエミッタ端子にそれぞれ接続される一対のエミッタ抵抗と、該エミッタ抵抗の他端に共通接続される第1バイアス電流設定回路と、第2エミッタフォロワ・トランジスタのエミッタ端子にそれぞれ接続される一対の第2バイアス電流設定回路とを具備する。

(もっと読む)

リミッタアンプ回路

【課題】良好な応答性を得ることができ、差動入力信号が入力されていない場合に正相出力信号と逆相出力信号のDC出力レベルが等しくなるのを防ぐことができるリミッタアンプ回路を得る。

【解決手段】差動増幅回路11は、正相入力信号と逆相入力信号とからなる差動入力信号を増幅する。差動増幅回路12は、差動増幅回路11の差動出力信号を増幅する。第1のオフセット調整回路14は、正相入力信号の直流成分と逆相入力信号の直流成分との電圧差に応じて差動増幅回路11の差動出力信号のDCオフセット電圧を調整する。第2のオフセット調整回路18は、差動増幅回路12の差動出力信号の一方の信号の直流成分と基準電圧REFとの電圧差に応じて差動増幅回路12の差動出力信号のDCオフセット電圧を調整する。

(もっと読む)

カスコード増幅器

【課題】 温度変動やプロセスのバラツキによる動作点及び特性の変動を抑えることが可能なカスコード増幅器を実現する。

【解決手段】 カスコード増幅器において、前段増幅回路の差動出力を増幅して出力するカスコード増幅回路と、バイアス電流に基づきカスコード増幅回路にバイアス電圧を供給すると共にバイアス電流及び前段増幅回路のバイアス電流を加算してカスコード電圧を決定しカスコード増幅回路のカスコードトランジスタのベースに印加するバイアス回路とを設ける。

(もっと読む)

増幅装置及び信号の増幅方法

【課題】増幅装置及び信号の増幅方法を提供する。

【解決手段】増幅装置は、信号入力(31)と、帰還入力(32)と、信号出力(33)とを備えた増幅器(3)を有する。第1の結合路(FB1)は、第1のインピーダンス素子(R1)を備え、帰還入力(32)を信号出力(33)に接続する。第2の結合路(FB2)は、直列に接続したフィルタ装置(4)と、バッファ回路(5)と、第2のインピーダンス素子(R2)を有し、帰還入力(32)を信号出力(33)または信号入力(31)に接続する。

(もっと読む)

回路装置、及び、この回路装置を備えたTVチューナ及びTV受像機

【課題】発振動作を起こしにくい。

【解決手段】アンプユニットA1は、2つの入力端子20,21から入力された電圧信号を増幅するとともに、電流信号に変換して出力する。アンプユニットA2は、入力と出力とが帰還抵抗R5,R6を介して接続されることにより、電流信号として入力された入力信号を、電圧信号に変換して2つの出力端子22,23へ出力する。アンプユニットA1は、カレントミラー回路CM1によって電流源CS1からミラーされた電流を動作電流として供給される。アンプユニットA2は、カレントミラー回路CM2によって電流源CS2からミラーされた電流を動作電流として供給される。

(もっと読む)

差動増幅回路及びその差動増幅回路を使用した充電制御装置

【課題】製造ばらつきによってオフセット電圧の分解能が影響されず、温度変化や経時変化にも影響を受けないオフセット調整回路を有する差動増幅回路及びその差動増幅回路を使用した充電制御装置を得る。

【解決手段】製造ばらつきによって、調整抵抗を構成する抵抗R1〜R4の抵抗値が変動しても、バイアス電流源2が該変動を補正するようにバイアス電流i3を変動させるため、調整抵抗における電圧降下は常に一定となり、測定したオフセット電圧Vofに最も近いオフセット補正電圧Vadjを設定することができ、更に、差動増幅回路1が作動中の温度変化に応じて調整抵抗が変化した場合や、経年変化で調整抵抗の抵抗値が変化した場合でも、バイアス電流生成用抵抗Rbも同様に変化をするため、オフセット補正電圧Vadjの変動を抑制することができるようにした。

(もっと読む)

信号取込みプローブにて利用可能なモード選択増幅器回路

モード選択増幅器回路は、入力信号A、B及びCを受けるように結合された多重差動増幅器回路を有する。各差動増幅器回路は、出力モードを表す信号出力を発生するために選択的に動作可能であり、各差動増幅器回路の出力モードは、信号入力の代数的組合せであるA−C、B−C、A−B及び(A+B)/2−Cの1つから選択される。モード選択増幅器回路は、信号取込みプローブにて利用可能であり、種々の信号出力モードを測定試験機器に供給する。  (もっと読む)

(もっと読む)

光信号受信回路およびそれを用いた光信号受信装置

【課題】 低電源電圧化で困難となる、帯域とダイナミックレンジの両立を実現する。

【解決手段】 光信号を受信して電流信号に変換する光電流変換回路(PD)の出力電流信号を受け、電圧信号に変換する電流電圧変換回路10を持ち、その後段に使用される差動回路50に電流源として抵抗を用いて、回路内部の動作電位の設定を容易にする。これによる、差動回路50の出力波形の非対称性の影響を回避するため、差動回路50の他方の入力に用いるリファレンス電位を、電流電圧変換回路10の出力電圧信号から回路60で生成する構成をとる。

(もっと読む)

1 - 20 / 42

[ Back to top ]