Fターム[5J500DN28]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | エミッタ(ソース)回路構成 (671) | エミッタ(ソース)電流可変回路 (18)

Fターム[5J500DN28]に分類される特許

1 - 18 / 18

演算増幅器

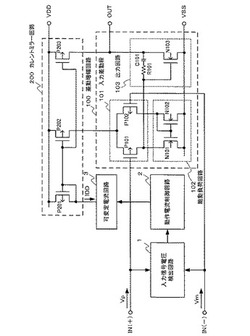

【課題】所定のS/Nを維持しながら消費電流の増加を抑制することのできる演算増幅器を提供する。

【解決手段】実施形態の演算増幅器は、正相信号Vpと逆相信号Vmが入力される差動増幅回路100と、差動増幅回路100へ動作電流を供給するカレントミラー回路200とを有する。この演算増幅器は、入力信号電圧検出回路1が、正相信号Vpと逆相信号Vmとの間の電圧差を検出し、動作電流制御回路2が、その電圧差の大きさに応じた制御信号を出力する。この制御信号の制御により、可変定電流回路3が、カレントミラー回路200へ入力する定電流の大きさを変化させる。

(もっと読む)

半導体装置

【課題】消費電流を削減する。

【解決手段】第1及び第2の入力端子に現れる電位差を第1及び第2の電源に基づいて増幅する差動アンプ(図2のMN1、MN2が相当)と、差動アンプを動作させるバイアス電流を制御するバイアストランジスタ(図2のMN3が相当)と、差動アンプの負荷となるカレントミラー回路(図2のMP1、MP2が相当)と、カレントミラー回路のダイオード接続側と其々の制御端が接続されると共に第1及び第2の電源間に直列に接続される、バイアストランジスタと逆導電型の第1及び第2のトランジスタ(図2のMP4、MP6が相当)を有し、第1及び第2のトランジスタの間の接続ノードをバイアストランジスタの制御端に接続するバイアス制御回路と、を備える。

(もっと読む)

差動増幅回路

【課題】差動増幅回路における入力オフセット電圧の上昇を抑制しつつ、同相入力電圧範囲を拡張する。

【解決手段】本発明による差動増幅回路は、ソース及びバックゲートが第1電流源205に共通接続された差動対トランジスタ201、202を備える差動入力段回路111と、差動入力段回路111の出力端子に接続される出力段回路121と、第1電流源205と出力段回路121の第2電流源206のそれぞれの電流I1、I2を、差動入力段回路111への入力電圧VIN1、VIN2に応じた大きさに調整する電流制御回路101とを具備する。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

半導体装置、データ伝送システム、及び半導体装置の制御方法

【課題】小振幅信号を高速に増幅して出力し、かつ、消費電力の少ないアンプを備える半導体装置を提供する。

【解決手段】クロックに同期してデータが更新される小振幅信号を受信するアンプ部と、アンプ部の出力に接続された出力部と、を備え、アンプ部はクロックに同期して小振幅信号の論理レベルが遷移しうるタイミングで電流源の電流を増加し、遷移しないタイミングで電流を減少する。出力部はクロックに同期してアンプ部の出力データの論理レベルが遷移しうるタイミングで出力インピーダンスを低下させて高速に負荷を駆動すると共に、論理レベルが遷移しないタイミングで出力インピーダンスを増加させて貫通電流が流れることを防ぐ。

(もっと読む)

差動増幅回路、増幅回路及び液晶ディスプレイドライバ

【課題】差動対が線形領域で高精度に動作する差動増幅回路、増幅回路及びこの差動増幅回路を用いた液晶ディスプレイドライバを提供する。

【解決手段】差動増幅回路は、入力電圧V1がゲート端子に与えられるトランジスタM1及びM2と、トランジスタM1、M2のソース端子に出力端が接続される差動対D1、D2と、差動対D1内のトランジスタM3、M4の共通ソース端子に電流を供給する可変電流源I1と、差動対D2内のトランジスタM5、M6の共通ソース端子に電流を供給する可変電流源I2と、を備え、トランジスタM3のゲート端子には入力電圧V2、トランジスタM5のゲート端子には入力電圧V1、トランジスタM4及びM6のゲート端子には入力電圧V3が与えられる。

(もっと読む)

RFシングルエンド/差動変換器

例えば、通信受信機中で使用するための非常に差動なシングルエンド/差動変換器を設計するための技術。例示的な実施形態では、cascompトランジスタを含む補助電流経路が、入力トランジスタ及びカスコードトランジスタを含む主電流経路に結合される。トランジスタは、補助電流経路によって生成された混近変調ひずみ結果物が主電流経路によって生成された混近変調ひずみ結果物を打ち消すように、バイアスされる。別の例示的な実施形態では、主電流経路の電流源トランジスタは、受信した入力信号のレベルに応じて適応的にバイアスされる。例示的な実施形態では、上記技術は、シングルエンド低雑音増幅器(LNA)出力電圧を、通信受信機の差動混合器入力にインタフェースするための変換器を設計するために適用されることができる。  (もっと読む)

(もっと読む)

差動増幅器

【課題】非直線性誤差が少なく広帯域であって、自在にゲインの切り替えを行うことができる差動増幅器を提供する。

【解決手段】差動増幅器1は一対の入力信号が入力されて、その差分に応じた差分を有する一対の信号を出力する入力回路(Q1,Q2、Q5,Q6、RE1,RE2)と、入力回路から出力される一対の信号を用いて入力回路で生ずる歪みを補償する補償回路(Q3,Q4)とを含む入力部11と、入力回路に対して行われる補償回路の歪み補償によって歪みが補償されるとともに入力回路から出力される一対の信号を増幅する複数の増幅回路12a,12bを含む出力部12と、複数の増幅回路12a,12bのうち、動作状態にする増幅回路と非動作状態にする増幅回路との切り替え制御を行う制御回路20とを備える。

(もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れた低消費電流の増幅器を提供する。

【解決手段】トランジスタ対(MN1,MN2)を用いて電流/電圧変換容量素子(CL1,CL2)を第1の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第2の電源から、差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

低雑音トランスコンダクタンス増幅を提供するためのデバイスが提示される。前記デバイスは、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部と、前記PMOSトランスコンダクタンス部に結合されたPMOSカスコード部と、前記RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部と、前記NMOSトランスコンダクタンス部に結合されたNMOSカスコード部と、を含み、前記PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号及び差動同相出力信号を提供する。RF信号を増幅するための方法も提示される。前記方法は、差動RF入力信号を受信することと、前記差動RF入力信号を電流信号に変換することと、前記電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供すること、とを含む。  (もっと読む)

(もっと読む)

集積回路の制御電圧決定方法、TEG回路のゲート電圧決定方法、TEG回路試験方法及び試験装置

【課題】集積回路において、トランジスタのしきい値電圧などの特性変動あるいはばらつきが与える回路動作への影響を受けにくい集積回路およびTEG回路を提供する。

【解決手段】1対の抵抗デバイスMP1,MP2と、1対のN型差動トランジスタMN1,MN2と、該1対のN型差動トランジスタに動作電流を供給する電流源トランジスタMLとを備えた電流モード動作回路において、その電流源トランジスタに流れる電流の制御電圧VLを、N型差動トランジスタのしきい値電圧などの特性変動に対して、集積回路の電圧利得が少なくとも1以上となるよう決定する。

(もっと読む)

半導体集積回路

【課題】マッチング状態設定時の困難性を排除し、出力信号の振幅調整を容易に行うことができる半導体集積回路を提供する。

【解決手段】スイッチング動作により出力信号を形成する信号出力回路1と、信号出力回路1に制御信号を供給して出力信号振幅を制御する制御回路2からなり、制御回路2は信号出力回路1を模した疑似回路部3を有し、疑似回路部3は抵抗R2が接続される一対の接続端子T21、T22を有し、高電位電圧が得られる接続端子T21の電圧レベルと信号出力回路1の高信号レベルを比較し、それらのレベルが同じになるように制御回路2を制御する第1信号レベル制御回路4と、低電位電圧が得られる接続端子T22の電圧レベルと信号出力回路1の低信号レベルを比較し、それらのレベルが同じになるように制御回路2を制御する第2信号レベル制御回路5を有する。

(もっと読む)

差動増幅回路

【課題】差動増幅器の電源変動除去特性及び同相除去特性を向上させること。

【解決手段】正側電源+Vccと負側電源−Vcc間において差動接続されたトランジスタQ1及びトランジスタQ2を有し、正側電源+VccとトランジスタQ1とトランジスタQ2のエミッタ共通接続点との間にバイアス回路14が接続された差動増幅回路1において、トランジスタQ1を流れるエミッタ電流I1、トランジスタQ2を流れるエミッタ電流I2及びバイアス回路14を流れるバイアス電流I3の合成電流Iを検出するトランジスタQ12及び抵抗R10と、トランジスタQ12及び抵抗R10の検出結果に応じて合成電流Iを一定に保持するトランジスタQ11と、を含む定電流回路16を備える。

(もっと読む)

増幅回路

【課題】周波数変換回路や同期検波回路などの掛算回路として構成する場合に、掛算後の出力信号に歪みを生じることがなく、変換利得や検波効率が高くなって、所期の出力信号が確実に得られるようにする。

【解決手段】電圧電流変換器70は、2個のMOS差動対を有し、入力信号電圧+Vinを出力電流io1に変換する。電圧電流変換器80は、2個のMOS差動対を有し、入力信号電圧−Vinを出力電流io2に変換する。負荷抵抗45によって、電流io1と電流io2とを加算し、かつ加算後の電流io(=io1+io2)を出力信号電圧+Voutに変換する。電圧電流変換器70の互いに異なるチャネル型のMOSトランジスタ57および59を局発信号+Loによってオンオフ制御し、電圧電流変換器80の互いに異なるチャネル型のMOSトランジスタ67および69を局発信号−Loによってオンオフ制御する。

(もっと読む)

差動増幅回路

【課題】 増幅率の可変範囲が広い差動増幅回路を提供する。

【解決手段】 このGmアンプ1では、MOSトランジスタ2〜6は相互コンダクタンスgm1を有する第1の副Gmアンプを構成し、MOSトランジスタ2,3,7〜9は相互コンダクタンスgm2を有する第2の副Gmアンプを構成する。Gmアンプ1の相互コンダクタンスはgmt=gm1−gm2となり、その最小値は0になり、最大値はgm1となる。したがって、従来のGmアンプ71のように抵抗素子78などの抵抗値Rによってgm1が制限されないので、gmtの可変範囲が従来よりも広くなる。

(もっと読む)

電圧増幅器

【課題】電圧増幅器においてクリップ電圧値のばらつきを抑える。

【解決手段】電圧増幅器10において、ドレイン電流Idの電流値は、リファレンス抵抗Rbに流れるリファレンス電流に等しくなるように設定されている。リファレンス電流の電流値は、リファレンス抵抗に印加される電圧(Vdd−Vref)とリファレンス抵抗Rbの抵抗値(Rb)によって(Vdd−Vref)/Rbとなる。このため、出力電圧のクリップ電圧値は、リファレンス電流の電流値と第二抵抗R2の抵抗値との積{(Vdd−Vref)×R2}/Rb=(Vdd−Vref)×(R2/Rb)となる。同一プロセスで形成された二つの抵抗の抵抗比を考えた場合、一方の抵抗のばらつきによる変動を他方の抵抗のばらつきが抑えることになる。つまり、抵抗単独のばらつきに対して、二つの抵抗の抵抗比のばらつきは小さく抑えられ、クリップ電圧値のばらつきが小さくなる。

(もっと読む)

検波回路

【課題】 ピーク値包絡線に正確に対応した出力が得られるAM変調信号検波回路を提供する。

【解決手段】 大振幅状態と小振幅状態の2状態のAM変調信号Viを受信しこの2状態を識別する際に、AGC回路の出力信号Voから、キャリア周波数成分を抽出し、信号Voの振幅のピーク位置にタイミングを合わせたクロックパルスCLを出力するタイミング抽出部と、クロックパルスCLのピーク位置にタイミングを合わせたサンプリングクロックパルスSCLを出力するクロック生成部と、比較基準電圧VR2を出力する基準電圧設定部とを備え、クロックパルスSCLの入力時に信号Voと比較基準電圧VR2とをサンプリング比較して比較結果信号TCOを出力し保持するサンプリング比較保持部を備えている。

(もっと読む)

三次変調相殺可変回路

三次相互変調を相殺するCMOSトランスコンダクタを提供する。トランスコンダクタは、トランスコンダクタンス回路及び可変ひずみ回路を含む。トランスコンダクタンス回路は入力電圧を受けて、トランスコンダクタンス成分とIM3成分を有する出力電流を生成する。ひずみ回路は同一の入力電圧を受けて、トランスコンダクタンス回路のIM3成分と同振幅かつ逆位相のIM3成分を有する電流を生成する。制御回路はトランスコンダクタンス回路のIM3の振幅とほぼ等しくなるようにそのIM3成分を調節するようにひずみ回路を調整する。ひずみ回路及びトランスコンダクタンス回路はその出力電流を総和するように構成され、それによりトランスコンダクタンスを比較的変化させずに、IM3成分を効果的に相殺する。 (もっと読む)

1 - 18 / 18

[ Back to top ]