Fターム[5K029DD22]の内容

直流方式デジタル伝送 (8,390) | 伝送システム構成 (1,787) | 伝送路の構成 (708) | 直列伝送路 (251)

Fターム[5K029DD22]に分類される特許

161 - 180 / 251

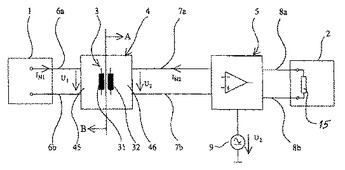

双方向直流絶縁送信チャネル

直流信号および交流信号を電気的に絶縁して送信するための、構成および方法。同じ唯一使用可能な直流絶縁チャネルを使用して、これらの信号を両方向に送信することができる。本構成は、第1の送受信システム(1)、短絡モードの直流変圧器(4)、演算増幅器装置(5)、およびイベント信号発生器(9)を有する第2の送受信システム(2)を含む。  (もっと読む)

(もっと読む)

ビット誤り率測定器

【課題】本発明は、ビット誤り率測定器に関し、クロック位相のオートサーチに要する時間を短縮し、低コストのコストバランスのとれたビット誤り率測定器を提供することを目的としている。

【解決手段】クロックをディレイ回路1により遅延させ、このクロックのタイミングにより、データを再生しそのデータのビットエラー数又はビットエラーレートを求めるビット誤り率測定器において、前記クロックの周波数を測定してその周期を求める周波数モニタ10と、該周波数モニタ10で求めた周期と前記ビットエラー数又はビットエラーレートによりクロックの位相の最適値を求める位相演算部11と、該位相演算部11で求めた前記最適値により、前記ディレイ回路1の遅延量を設定するディレイコントローラ2と、を有して構成される。

(もっと読む)

送信装置、受信装置、伝送システム、および伝送方法

【課題】多値信号の伝送を、分解能を劣化させることがなく、効率的に行うことができる送信装置、受信装置、伝送システム、および伝送方法を提供する。

【解決手段】送信装置2において、多値信号を伝送するにあって、送信すべきデータの各ビットの最大許容連続ビット長を、MSBからLSBに向かって長くし、その長さは、各ビットの重みの逆数に比例した値としたデータフォーマットのnビット送信データ列を生成して、光伝送路5に送出することにより、AC結合を含む広帯域回路において、分解能の高い、あるいは、S/N比の高い多値伝送を可能にする。

(もっと読む)

クロックアンドデータリカバリ回路及びSERDES回路

【課題】クロックアンドデータリカバリ回路の動作余裕度の大きさを測定可能とするSERDES回路の提供。

【解決手段】シリアルデータサンプリング回路(101)と、クロックとデータの位相関係を検出する位相比較器(102)と、位相比較結果(UP/DOWN)に基づき位相制御信号を出力する位相制御器(103)と、互いに異なる位相の複数のクロック信号よりなる多相クロックを受け、位相制御信号に基づき位相を補間したクロック信号をデータサンプリング回路(101)に供給する位相補間器(104)とがループを構成する。この位相制御器(103)は、位相制御信号とは別の位相制御信号Aを生成して別の位相補間器(105)に供給し、多相クロックを受け位相制御信号Aに対応して補間したクロック信号に基づき入力データをサンプルする別のデータサンプリング回路(106)を備え、好ましくは、データをサンプルするための閾値レベルが可変に設定される。

(もっと読む)

通信システム及び通信装置

【課題】マスタとバスを介して接続される複数のスレーブとの間で非同期通信を行う際にバスのドライブレベルが「3」以上の複数規定されている場合でも、1ビット期間の測定を正確に行う。

【解決手段】SbW通信を行うスレーブ11は、コンパレータ12に3段階のドライブレベルに対応するしきい値A,B,Cを設定し、立上りパルス発生部29はバス3のドライブレベルが各しきい値A〜Cを夫々を超えた場合に夫々ワンショットパルスを発生させ、立下りパルス発生部30はバス3のドライブレベルがしきい値Aを下回った場合にワンショットパルスを発生させる。そして、RSフリップフロップ23を、立上りパルス発生部29より出力されるパルスのOR条件でセットして立下りパルス発生部30より出力されるパルスでリセットし、1ビット期間を計測するカウンタ26をRSフリップフロップ23がリセット状態で且つ前記パルスのOR条件が成立した場合にクリアする。

(もっと読む)

シリアル通信装置

【課題】カウントパルスの周波数を上げることなく、誤った符号判定を抑制し得るシリアル通信装置を提供する。

【解決手段】カウントパルス発生部21によりシンクフィールドSFを構成するビット列の1ビット区間よりも十分に短いパルス幅のカウントパルスCpを発生させ、シンクフィールドSFのスタートビットからストップビットまでの間で発生したカウントパルスCpの数をビット長カウント部23によりカウントする。そして、ビット長決定部30よって、ビット長カウント部23によりカウントされたカウントパルスCpの数をビット列のビット数2nで除した商Qおよびその余りSに基づいて1ビット区間の1ビット長を決定し、ビット長決定部30により決定された1ビット長に従った所定タイミングで同期クロック生成部27により同期クロックSynCLK を生成する。

(もっと読む)

電気信号出力装置および半導体レーザ変調駆動装置および画像形成装置

【課題】 出力信号の立ち上がり,立ち下がりをより一層速くすることができて、高速に信号伝送を行うことの可能な電気信号出力装置を提供する。

【解決手段】 信号データに応じてハイかロウかのスイッチングを行なって出力信号を生成し出力ノードに出力するスイッチング部1と、電気信号出力装置の出力インピーダンスを伝送路のインピーダンスに整合させるために設けられているインピーダンス整合部2と、出力インピーダンスを伝送路のインピーダンスに合うようにインピーダンス整合部2を設定する制御手段3と、スイッチング部1のスイッチング時に、出力ノードに補助的に電流を流し込んだり吸い出したりするスイッチング補助部4とを有し、スイッチング補助部4は、電流を流し込んだり吸い出したりする期間をシリアル電気伝送システムの基準クロックのパルス幅よりも短い期間にするように構成されている。

(もっと読む)

電気信号出力装置および半導体レーザ変調駆動装置および画像形成装置

【課題】 出力信号の立ち上がり,立ち下がりをより一層速くすることができて、高速に信号伝送を行うことの可能な電気信号出力装置を提供する。

【解決手段】 シリアル電気伝送システムにおける電気信号出力装置において、信号データに応じてハイかロウかのスイッチングを行なって出力信号を生成し出力ノードに出力するスイッチング部1と、出力インピーダンスを伝送路のインピーダンスに整合させるために設けられているインピーダンス整合部2と、スイッチング部1のスイッチング時に、出力ノードに補助的に電流を流し込んだり吸い出したりするスイッチング補助部4とを有し、スイッチング補助部4は、電流を流し込んだり吸い出したりする期間をシリアル電気伝送システムの基準クロックのパルス幅よりも短い期間にするように構成されている。

(もっと読む)

受信装置

【課題】 クロックの同期を行うことなく高速のシリアル通信で高い通信効率を維持しながら通信を行うことが可能な受信装置を実現する。

【解決手段】 シリアル伝送路を用いてパケット通信を行う受信装置において、シリアル伝送路を伝播する伝送信号を異なる位相のクロック信号のタイミングで取り込んで受信データを生成する複数の受信回路と、これら受信回路でそれぞれ生成された受信データの正否をそれぞれ判定する複数の判定回路と、これら判定回路において正しいと判定された受信データを選択する選択回路とを設ける。

(もっと読む)

電気信号出力装置および半導体レーザ変調駆動装置および画像形成装置

【課題】 多レベルの振幅(多ビットの情報)の出力信号(多値信号)の立ち上がり,立ち下がりをより一層速くすることができて、高速に信号伝送を行うことの可能な電気信号出力装置を提供する。

【解決手段】 シリアル電気伝送システムにおける多レベルの振幅の出力信号を出力する電気信号出力装置であって、信号データに応じてハイかロウかのスイッチングを行なって出力信号を生成し出力ノードに出力するスイッチング部1と、出力インピーダンスを伝送路のインピーダンスに整合させるために設けられているインピーダンス整合部2と、出力インピーダンスを伝送路のインピーダンスに合うようにインピーダンス整合部2を設定する制御手段3と、スイッチング部1のスイッチング時に、出力ノードに補助的に電流を流し込んだり吸い出したりするスイッチング補助部4とを有する。

(もっと読む)

通信装置

【課題】通信線の接続極性が入れ替わっていても、受信した信号レベルを反転させることなくスタートビットを検出することができる通信装置を提供する。

【解決手段】アイドル状態がハイレベルの信号で表され、スタートビットがローレベルの信号で表され、データビット列の先頭のデータビットがハイレベルの信号である通信フレームを用いて、通信信号が所定の時間変化しない場合にアイドル状態であると判断すると共に通信線における実際の信号レベルに関わらず、通信線の信号レベルをハイレベルであるとする一方、通信信号が変化した場合にアイドル状態ではないと判断すると共に通信線における信号レベルを受け付けるハイレベル保持回路103と、ハイレベル保持回路103で受け付けられた信号レベルに基づいてスタートビットを検出して通信フレームの先頭を識別し、データビット列を取得するシリアル信号非同期受信部108とを備えた。

(もっと読む)

シリアル転送用インターフェース

【課題】環境の変化やLSIプロセスによる特性のばらつきが生じる場合であっても、安定で高品質な信号伝送を実現するシリアル転送用インターフェースを提供する。

【解決手段】課題を解決するために、シリアル転送用インターフェース10に、信号波形のひずみを補正する信号波形補正部11と、信号波形を同期クロックにあわせてラッチして後段回路に出力するラッチ部12と、信号波形補正部11のフィルタ特性を所定に範囲で変更するフィルタ特性調整部13と、所望の位相を有する同期クロックを生成するクロック生成部14と、テストパターンの検出やフィルタ特性調整部13及びクロック生成部14の制御を行うパターン判定部15と、を少なくとも備える。

(もっと読む)

調歩同期通信用受信回路

【課題】高速のビットデータを受信することができ、かつ、受信データを正確に再現することができる調歩同期受信回路を提供する。

【解決手段】受信シリアルデータ57のビットレートと同等のスピードで位相が等間隔にずれた複数のクロック0〜nを生成し、この各クロックで受信シリアルデータをサンプリングしそのデータを、複数のレジスタ回路52_0〜52_nに保持する。複数のクロックのうち、受信シリアルデータを最適な位置でサンプリングするクロックを検出し、そのクロックでサンプリングされたデータを保持するレジスタ回路からのデータを出力させる。このような構成では、ビットレートの効率が大幅に向上し、また、各クロックでサンプリングした受信データから最適なデータを選択するようにしたので、クロックの切替で発生するノイズ等の影響を受けることが無く、受信データを正確に再現することが可能となる。

(もっと読む)

送信装置、受信装置、及び送受信装置

【課題】データ信号の送受信における同期のずれを、送信装置に位相比較回路を設けることなく、送信装置側で補正する送信装置、受信装置、及び送信装置と受信装置とを備えた送受信装置を提供する。

【解決手段】データ信号及びクロック信号を並列に受信装置へ送信する送信装置であって、前記クロック信号と前記データ信号との位相差を示すと共に前記受信装置から送信される位相差信号の位相差に応じた時間だけ前記データ信号または前記クロック信号を遅延するので、データ信号の送受信における同期のずれを送信装置側で補正することができる。

(もっと読む)

信号伝送回路

【課題】従来の単一ソースフォロワにおける駆動能力低下の欠点を克服し、電圧モード伝送の低消費電力性を保持しつつ、高速伝送が可能な信号伝送回路を提供する。

【解決手段】ソースフォロワの出力電圧がLowからある一定の電圧に立ち上がる時間はバイアス電圧に依存するため、バイアス電圧を高くして出力電圧の収束電圧を高く設定することで、ある電圧まで立ち上がる時間を短縮できる。そこで、入力データ信号がLowからHiへ遷移した際に、出力電圧の収束値が所定のHi電圧となるようバイアスされた第1のソースフォロワ20と、1クロック周期の後に同Hi電圧となるようバイアスされた第2のソースフォロワ23とを用い、これら2つのソースフォロワ20,23を適切なタイミングで動作させる。

(もっと読む)

制御システム

【課題】線間の容量及びデバイスの容量により信号波形のレベルの低下及び積分値が低下しても正しく通信を行うことができ、コントローラから1対多の通信で複数のデバイスを制御する場合にも制御線の数を増やす必要がない。

【解決手段】本発明の制御システムは、複数のモジュール2−1、2−2、・・・2−nを同一の状態に制御するためのデバイス1の制御に関する信号を予め設定された閾値に基づいて整形する波形整形ブロックを、複数のモジュール2−1、2−2、・・・2−nのうちのいずれかに設け、波形整形ブロックにより整形されたデバイス1の制御に関する信号を順次次段に送出するものである。

(もっと読む)

データ受信装置およびデータ伝送システム

【課題】 多値論理信号の多値論理を精確に識別することができる。

【解決手段】 データ伝送システム1において、データ受信装置300は、受信されたリファレンスクロックに基づいて、多値論理信号の振幅変動に追随し、振幅値を識別する閾値信号を生成する振幅検出回路310と、多値論理信号を増幅する信号増幅回路320と、閾値信号をコンパレータの電圧オフセットとして多値論理信号の識別に用いるコンパレータ部330と、受信ワードクロックの周波数をK倍して、各シンボルにおけるデータを識別するためのトリガーとなる受信ビットクロックを生成し、受信ビットクロックと受信データクロックとに応じて受信シリアルデータを受信パラレルデータに変換するデコーダ340を有している。

(もっと読む)

伝送線路装置とその終端処理方法

【課題】 伝送信号の反射による不要輻射を抑圧する。

【解決手段】 送信信号駆動等価回路部装置11と信号受信等価回路部装置13との間を基板伝送線路部装置12で接続してパルス信号を伝送する伝送システムにおいて、伝送線路部装置12の信号受信等価回路部装置13に接続される端部に、伝送線路インピーダンス相当のインピーダンスを有する一次終端回路121を並列接続し、基板伝送線路部装置12の信号受信等価回路部装置13に接続される端部に、伝送線路インピーダンスの半分相当のインピーダンスを有する二次終端回路を直列接続する。

(もっと読む)

データ受信装置およびデータ伝送システム

【課題】 多値論理信号の多値論理を精確に識別することができる。

【解決手段】 データ・クロック分離回路30は、信号VP、VMの閾値を正しく識別して、信号VP、VMから受信シリアルデータおよび受信ワードクロックを分離して取り出す回路であり、オフセットを変化させることができる可変オフセット回路(オフセット電圧調整回路)31、32、38、39、差動増幅器33、34、加算器35、LPF36、誤差増幅器37、コンパレータ40、41、42、セレクタ43で構成されている。可変オフセット回路31、32、差動増幅器33、34、加算器35、LPF36、誤差増幅器37でネガティブフィードバックループ系が形成されており、誤差増幅器37の誤差信号の出力に基づいて、可変オフセット回路31、32は、その誤差を打ち消すように動作する。

(もっと読む)

データ伝送システム

【課題】 受信側で、多重データの分離を安定して行うことが可能なデータ伝送システムを提供する。

【解決手段】 調歩同期式データと同期式データの両方を送受信可能なデータ伝送システムにおいて、送信側1では、調歩同期式データと同期式データを多重データにしその先頭に、調歩同期式データとして認識されないデータパターンの同期パルスを付加して多重データを構成して送信し、受信側2では、前記同期パルスを検出しそのデータパターンを、その後に続く多重データの分離の開始位置として分離することを特徴とする。

(もっと読む)

161 - 180 / 251

[ Back to top ]