Fターム[5K029DD22]の内容

直流方式デジタル伝送 (8,390) | 伝送システム構成 (1,787) | 伝送路の構成 (708) | 直列伝送路 (251)

Fターム[5K029DD22]に分類される特許

121 - 140 / 251

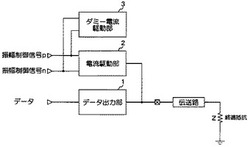

出力装置、多値出力装置、及び半導体集積装置

【課題】ディエンファシス時と非ディエンファシス時の消費電流を一定にすることで、電源変動も一定となり、その結果ジッタの低減を可能にする出力装置を提供する。

【解決手段】入力されたデータを振幅制御して出力するデータ出力部1と、第1及び第2の振幅制御信号に基づいて伝送路に電流を重畳出力して伝送信号の振幅を制御する電流駆動部2と、第1及び第2の振幅制御信号に基づいて電流駆動部2との合計消費電流値が略一定となるように消費電流を制御するダミー電流駆動部3と、を備えて構成されている。

(もっと読む)

半導体装置

【課題】 シリアルデータの高速化にともなう受信性能の低下および連続同符合データ受信によるクロックデータリカバリー回路の精度低下を防止し、尚且つ消費電力の低いクロックデータリカバリー回路を提供する。

【解決手段】 シリアルデータを受信するSerDes回路101と、並走クロック信号を受信する参照SerDes回路102とを有し、SerDes回路101は、参照SerDes回路102の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。

(もっと読む)

シリアルデータ通信システム、及びシリアルデータ通信方法

【課題】マスター装置からスレーブ装置へシリアルデータを送信する際において、通信エラーを即座に知ることができる。

【解決手段】マスター装置からスレーブ装置に送信されるシリアルデータTxDには、同じ構成のダミーデータdummyが2バイト以上連続するように付加されており、スレーブ装置は該ダミーデータdummyを認識した場合には、通信エラー処理を行うようになっている。いま、ノイズ等の影響により、シリアルデータが符号TxD2に示すようにΔtだけシフトしてしまったとすると、期間A5及びA6ではETXもシフトしているために認識されず、データ受信終了の処理はされない。しかし、A7の期間では、1つ目の0xFFの一部と2つ目の0xFFの一部とが受信されて0xFFが認識されることになるので、スレーブ装置は通信エラー処理を即座に行うことができる。

(もっと読む)

シリアルデータ通信システム、及びシリアルデータ通信方法

【課題】クロック信号との同期を取らなくてもスレーブ装置からマスター装置へのシリアルデータ送信を可能とする。

【解決手段】スレーブ装置は、シリアルデータRxD1を送信した後、端子の状態をハイレベルにする。マスター装置は、その信号0xFFを受信した場合に、全データの受信終了としてデータ解析を開始する。いま、スレーブ装置からマスター装置に送信されるシリアルデータが符号RxD2に示すようにΔtだけシフトしたとすると、期間A5及びA6ではETXもシフトしているために認識されず、データ受信終了の処理はされない。しかし、A7の期間では、1つ目の0xFFの一部と2つ目の0xFFの一部とが受信されて0xFFが認識されることになり、データ受信終了の処理がされる。これにより、クロック信号CLKとの同期を取らなくても、マスター装置へのシリアルデータ送信が可能となる。

(もっと読む)

差動信号出力装置

【課題】電源電圧の変動によって伝送信号に生じるジッタを抑制することができる差動信号出力装置を提供すること。

【解決手段】伝送データを差動信号として出力する差動信号出力装置において、伝送データを表す信号を増幅し、増幅した信号から差動信号を生成する第1差動信号生成回路4と、伝送データの基準クロックに同期し、伝送データが遷移しないビットにおいてのみ遷移するダミーデータを生成するダミーデータ生成回路3と、ダミーデータを表す信号を増幅し、増幅した信号から差動信号を生成する第2差動信号生成回路5と、を備える。

(もっと読む)

半導体集積回路の信号伝送装置

【課題】マルチレベル送信動作の有無、動作速度、および出力信号のスイング幅を調整できる半導体集積回路の信号伝送装置に関し、選択的にマルチレベル送信動作を行う。

【解決手段】マルチレベル送信動作の有無によって複数のビットの入力信号を直列又は並列に出力するマルチレベル送信制御手段と、マルチレベル送信制御手段から直列又は並列に伝送される信号の形態に対応して選択的にマルチレベル送信動作を行う信号処理手段とを含むことを特徴とする。

(もっと読む)

送信装置

【課題】高速データ信号における波形品質を保つための様々な規格値を同時に満たすような送信装置を提供する。

【解決手段】出力信号TXOP,TXONを、ドライバ回路部110において、電源電圧VDDaをもとに抵抗分割で生成し、出力信号TXOP,TXONの振幅を、出力振幅補正部120において、電源電圧の変化に応じて生成した電流I1により補正する。これにより、電源電圧VDDaのばらつきに起因する出力信号TXOP,TXONの振幅のばらつきが補正される。

(もっと読む)

送信装置、受信装置および同期式シリアル通信システム

【課題】データ種別の切換誤検出が容易で、2以上の種別データを通信する際にデータ種別の切換え判別を容易に行える同期式シリアル通信システムの提供を目的とする。

【解決手段】データ信号設定をクロック信号の立上り(または立下り)エッジで行い、データ信号読込みをクロック信号の立下り(または立上り)エッジで行う同期式シリアル通信において、2種類のデータを送る場合にデータ種別の切換え時にデータ信号設定をクロック信号の立下り(または立上り)エッジで行い、データ信号読込みをクロック信号の立上り(または立下り)エッジで行う様に切換え、データ種別の区間中それを継続することを特徴とする。

(もっと読む)

1線式データ通信方法及び通信装置

【課題】内部ICの回路構成が簡潔で、ICの小型化を可能にした1線式データ通信装置を提供する。

【課題の解決手段】1線式データ通信装置内部のICの受信部1は、1本の信号線を介して異なるパルス幅にそれぞれ対応する複数のデータを有するデータ信号が入力される入力端子2と、この入力端子2から入力されたデータ信号を反転するインバータ3と、各データのパルスの立ち上がりまたは立ち下がりをクロックタイミングとして抽出するクロックタイミング抽出部4と、前記インバータから出力されたデータ信号のデータのパルス幅に基づいて複数のデータのうちどのデータであるかを判別するデータ判別部5と、このデータ判別部5で判別したデータをクロックタイミング抽出部4から出力されたクロックタイミングを受けて取り込むメモリ部6を備える。

(もっと読む)

デジタル信号伝送装置,デジタル信号伝送方法及びデジタル信号伝送システム

【課題】固定クロックレートのシリアルデジタル信号の伝送時の波形周期の乱れを、ローコスト且つフレキシブルな集積化が可能なデバイスを用いて補正し、しかも伝送レート幅が広い場合にも容易に補正する。

【解決手段】シリアルデジタル信号のクロックレートよりも高速なクロックを生成するクロック生成手段6と、入力されたシリアルデジタル信号が書き込まれ、書き込まれたシリアルデジタル信号が、クロック生成手段6で生成されたクロックを読出しクロックとして読み出される記憶手段1と、記憶手段1の読出しアドレスを制御することにより、記憶手段1から読み出されるシリアルデジタル信号の波形周期を増減制御する周期制御手段5とを備える。

(もっと読む)

クロックのデューティ比を活用した高速度シリアル通信

【課題】 シリアルデータの送受信を向上させる。

【解決手段】 シリアルデータの送受信の際に、送信したいデータが、例えば“00…”又は“11…”のように0又は1が複数ビット連続しているような構造である場合、連続しているビット数に応じて送信側100が出力する同期クロック121のデューティ比を変更する。その際の送信側からの出力データ120は、送信したいデータが“00…”ならば0、“11…”ならば1とする。受信側130は受信データが0か1かを認識し、更に同期クロックのデューティ比に応じて、受信データ0又は1が何ビット連続している構造かを判断し、そのビット数分だけデータをデータ受信シフトレジスタ133に格納する。これにより、同期クロック121の1周期の間に複数ビットのデータ120の送受信が可能となる。

(もっと読む)

超広帯域無線通信装置

【課題】10GHz程度の超広帯域を簡易な構成で利用可能とすることで、短距離高速通信を低価格で実現可能とする超広帯域無線通信装置を提供する。

【解決手段】クロック153aをクロック152aより所定時間だけ遅らせることで、入出力処理部153は入出力処理部152より所定時間だけ遅れて動作するようにしている。バイアス手段154は、入出力処理部153からトリガ信号22が入力されると、これに一定のバイアスを付加している。コンパレータ155は、入出力処理部152からトリガ信号21を入力するとともに、バイアス手段154からバイアスが付加されたトリガ信号22を入力し、トリガ信号21がトリガ信号22よりも大きいときだけ、所定の出力を行うよう構成されている。

(もっと読む)

ドライバ回路

【課題】複雑な回路構成を必要とすることなく、伝送損失を受けた信号を模擬した模擬信号を可変的に生成し、DUTに内蔵された高域強調回路の正確な試験を実現することができるドライバ回路を提供する。

【解決手段】入力信号に応じて、伝送損失を受けた信号を模擬した模擬信号を出力するドライバ回路10において、入力信号が入力され、入力信号と同一波形の信号を出力信号として出力するメインドライバ18と、入力信号が入力され、入力信号を反転した波形の信号を出力信号として出力するサブドライバ20と、サブドライバ20の出力信号が入力され、サブドライバ20の出力信号の高域を強調した信号を出力信号として出力する高域強調回路22と、メインドライバ18の出力信号と高域強調回路22の出力信号とを加算した模擬信号を出力する加算回路24とを有している。

(もっと読む)

直列通信システムにおける直列データの送受信方法及び装置とこのための直列通信システム

本発明は、直列通信システムにおいて信号の変化を最小にすることにより効率的な直列データの送受信方法及び装置とこのための直列通信システムを開示する。直列通信システムにおいてコーディングされた並列データを直列データに変換し、上記直列データを送信する方法は、上記コーディングされた並列データの情報ビットが圧縮されないように所定のビット値を有するビットとして定義される上記情報ビットが1番目に発見される位置を決定するステップと、上記決定された位置に到達するまで上記1番目に発見される情報ビットと上記1番目に発見される情報ビットの次の少なくとも1つのビットを圧縮された直列データとして直列に送信するステップと、を含む。  (もっと読む)

(もっと読む)

高速デジタルデータ伝送装置

【課題】システムLSI1とメモリ2、3間に波形整形回路5、15を配置し、波形整形回路5、15で入力デジタルデータを自動波形整形してその波形歪成分を適確に除去可能な高速デジタルデータ伝送装置を提供する。

【解決手段】システムLSI1と外部接続された1つ以上のメモリ2、3を備え、システムLSI1と1つ以上のメモリ2、3間でデジタルデータを伝送するもので、システムLSI1は、1つ以上のメモリ2、3に接続されたデジタルデータラインに波形整形回路9、15を配置し、波形整形回路9、15は、1つ以上のメモリ2、3から供給されるデジタルデータを微分して微分パルスを形成する微分回路20と、形成した微分パルスとデジタルデータとを重畳処理する歪除去回路手段21からなり、歪除去回路手段21における微分パルスとデジタルデータとの重畳処理は、デジタルデータに微分パルスを重畳し、波形整形によりその波形歪成分の除去処理を行うものである。

(もっと読む)

極性判定装置、極性判定方法、極性設定装置および基地局装置

【課題】高い精度で極性を判定することができるとともに、ノイズによる極性の誤判定を防止することができる極性判定装置等を提供する。

【解決手段】極性判定装置11は、パルス信号生成回路12、Dフリップフロップ13、及び誤判定防止回路14を備える。パルス信号生成回路12は、同期信号S10の立ち上がりのタイミングで所定のパルス幅を有するパルス信号S12を出力する。Dフリップフロップ13は、クロック端に入力されるパルス信号S12のタイミングにおいてD入力端に入力される同期信号S10の論理レベルを、同期信号S10の極性を判定する判定信号S13として出力する。誤判定防止回路14は、Dフリップフロップ13から出力される判定信号S13の論理レベルが変化した場合に、変化する前の論理レベルを同期信号S10の所定周期分だけ継続出力することにより同期信号S10の極性の誤判定を防止する。

(もっと読む)

シリアルデータ伝送方法、送受信装置及び1対の送受信装置のシリアルデータ伝送方法

【課題】外来のノイズなど使用環境に応じて、伝送パラメータの最適化が可能なシリアルデータ伝送方法、送受信装置及びシリアルデータ伝送方法を提供すること。

【解決手段】送受信装置30のシリアルデータ伝送方法において、受信したシリアルデータのエラーを検出するステップ(S113)と、エラーの検出頻度が所定値を超える場合、受信したシリアルデータの入力レンジを増減幅する第1の電圧変換器41の出力電圧を増大させるステップ(S125)と、送信するシリアルデータを増減幅する第2の電圧変換器22の出力電圧の増大を要求するステップ(S126)と、通信相手の送受信装置から受信するシリアルデータの入力レンジを増減幅する第3の電圧変換器21の出力電圧を増大させる設定が完了した旨の通知を受信した場合(S129)、送信するシリアルデータを増減幅する第4の電圧変換器42の出力電圧を増大させるステップ(S130)と、を有する。

(もっと読む)

信号等化器

【課題】コイルを使用することなくかつ伝送線路をそのまま等化器の回路部品に使用して、GHz級の高い周波数においても優れた信号減衰を補償する信号等化器を提供する。

【解決手段】送信端と受信端の間を接続して信号を伝送する主伝送線路TL1と、前記主伝送線路の受信端側に前記受信端と並列に接続された受信側終端抵抗R2と、前記受信側終端抵抗に並列に接続された、伝送線路TL2と前記伝送線路とインピーダンス値が異なる終端抵抗R3との直列回路からなり、前記主伝送線路の受信端側に所望の特定周波数帯域での電圧振幅を他の周波数帯域より大きくする周波数特性を与える周波数特性調整用回路FR1と、を備えた。

(もっと読む)

半導体集積回路

【課題】シリアルデータ通信を行なう際に発生するシリアルデータのジッタを、外部装置を使用することなく測定できるBIST回路を備えた半導体集積回路を提供する。

【解決手段】半導体集積回路は、パターンジェネレータにより生成したテスト用パラレルデータをシリアライザによりシリアルデータに変換し、そのシリアルデータをデシリアライザによりパラレルデータに変換し、エラーディテクタによりテスト用パラレルデータと照合しビット・エラー・レートを算出する。その際、CDR回路により生成されたリカバークロックの位相を位相調整回路によりコードに対応したシフト量分シフトし、対応するコードと算出したビット・エラー・レートをレジスタに記憶した後、レジスタに記憶されたコードとコードに対するビット・エラー・レートを読み出し、演算回路によりシリアルデータのジッタ量を算出する。

(もっと読む)

シリアル通信装置およびその位相差調整方法

【課題】クロック信号とデータ信号の位相関係を効率良く個々に最適な値に調整する。

【解決手段】送信器10に各信号の位相調整を行うための調整用信号を出力する調整用信号出力機能が設けられている。また、受信器20には、各信号の遅延量を設定可能な可変遅延部21と、各信号の位相状態を検出する位相検出部22と、検出された位相状態に応じて可変遅延部による各信号の遅延量を調整する遅延調整部23とが設けられている。位相調整時には、送信器10から調整用信号を出力させ、受信器20の位相検出部22によって各信号の位相状態を検出させて、検出された位相状態に応じて遅延調整部23によって可変遅延部21による各信号の遅延量を調整させることにより、データ信号とクロック信号の位相関係を最適化して、データ信号が安定した部分でデータを読み取らせる。

(もっと読む)

121 - 140 / 251

[ Back to top ]