Fターム[5K029DD22]の内容

直流方式デジタル伝送 (8,390) | 伝送システム構成 (1,787) | 伝送路の構成 (708) | 直列伝送路 (251)

Fターム[5K029DD22]に分類される特許

141 - 160 / 251

64B/66B符号化処理用データ生成方法及び回路

【課題】64B/66B符号化処理に使用される、より有効なデータの生成方法及び回路を提供する。

【解決手段】パケットデータPD並びにその先頭情報SI及び末尾情報TIを受信した時、情報SI及びTIに基づいてパケットデータPDの先頭及び末尾にそれぞれ先頭識別バイトS及び末尾識別バイトTを付加した書込ユーザデータUD_Wと、両識別バイトS及びTの位置を表示する制御データCD_Wとを対応させてメモリの所定のアドレスA0から順次書き込む。アドレスA0から、順次8バイトづつのユーザデータUD及びこれに対応する制御データCDを読み出して64B/66B符号化回路に与える。該読出ができない期間T_UR中、8nバイト分(n≧1)のアイドルバイトC及びそれを表示する制御データCD、或いは保守管理用情報の先頭及び末尾にそれぞれ識別バイトS及びTを付加した8nバイト(n≧2)の保守管理用ユーザデータ及び両識別バイトS及びTの位置を表示する制御データCDを該64B/66B符号化回路に与える。

(もっと読む)

シリアルクロック及びデータリカバリのための信号インタリービング

【課題】シリアルデータストリームからタイミング情報及びデータを回復させるクロック及びデータリカバリ(CRD)システム及び方法を提供する。

【解決手段】CDRシステム(100)は回復状態のクロック/データ信号を生じさせるサンプリング回路(105)及びインタリービングフィードバックネットワーク(110)を有する。このネットワークは、回復信号に基づき制御信号を生じさせる論理回路(115)、制御信号に基づき大域クロック信号の4つの位相から選択を行う第1マルチプレクサ(120)、選択大域クロック信号に基づき遅延信号を生じさせる第2マルチプレクサに結合されている第1遅延セル組を含む第1遅延ロックループ(130)及び1組の移相フィードバック信号を生じさせる第2遅延セル組を含む第2遅延ロックループ(135)を有する。

(もっと読む)

信号送信方法、信号受信方法および送信回路、受信回路

【課題】より確実な信号処理を可能とする信号伝送技術を提供する。

【解決手段】送信回路20のパラレルシリアル変換部22は、同期クロックCK_SYNCよりもn倍(nは2以上の整数)以上高速な伝送クロックに同期してn本の信号を多重化してシリアル形式へ変換する。パラレルシリアル変換部22は、タイミング上の制約が厳しい信号を最初に処理することにより、その信号が最初に含まれる形で信号フレームを形成する。受信回路30のシリアルパラレル変換部32は、伝送クロックCK_TRSに同期して、シリアル形式の信号を、パラレル形式の信号に展開する際、シリアル形式にて受信した各信号のタイミングに応じて、順次、後段の回路へ出力する。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】スケルチ検出回路は、差動信号の電位振幅が、スケルチレベルを超えているかどうかを検出し、その検出信号を出力するピーク検出回路と、検出信号のパルス幅を、そのパルス幅の時間を含めて、差動信号のデータの1周期分の時間以上の時間だけ延長するパルス幅延長回路とを備える。ここで、ピーク検出回路は、差動信号の電位振幅に応じた電位を持つ第1および第2の信号を出力する入力アンプ回路と、入力アンプ回路と同一構成であり、スケルチレベルに相当するリファレンス電圧に応じた電位を持つ第3および第4の信号を出力するレプリカアンプ回路と、第1および第2の信号に応じて流れる合成電流と第3および第4の信号に応じて流れる固定電流とを比較し、その電流差に応じて、差動信号の電位振幅がリファレンス電圧を超えているかどうかを表す検出信号を出力する電流比較回路とを備える。

(もっと読む)

送信デバイス及び電気回路並びに消費電流安定化方法

【課題】出力対象にするデータが存在するデータ有効期間では上記データを出力し、存在しないデータ無効期間ではダミーデータを出力する送信デバイスにおける消費電流の変動を抑制する。

【解決手段】送信デバイス30内のセレクタ16は、データ有効期間ではデータD1を選択し、データ無効期間では、ダミーデータ生成回路17が生成したダミーデータ5を選択する。ダミーデータ生成回路17は、データ有効期間において出力されるデータとのデータ変化率の差分が小さいダミーデータを生成する。例えば、データ変化率が50%のダミーデータ5や、データ無効期間の直前におけるデータD1のデータ変化率に応じたデータ変化率を有するダミーデータ5を生成する。

(もっと読む)

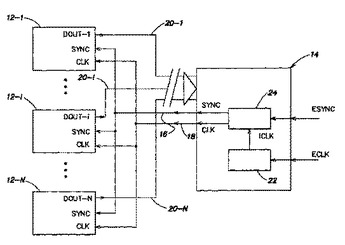

シリアルディジタルデータ通信インターフェイス

伝播遅延が数クロックサイクル長までおよび、ゆっくりと変動する可能性のある、データ送信機12からデータ受信機14へのデータ伝送のシリアルプロトコルおよびインターフェイス。データ受信機は、データ送信機にクロックを供給する。受信機または送信機のいずれかによって供給される同期信号は、クロックによって制御される転送レートで、データ伝送のフレームを始動させる。同期信号は、フレーム長として知られている、データヘッダーとそれに続く所定の数のデータビットの送信を調整する。データ受信機は、ヘッダービットを使用して、後続のデータビットをサンプリングする時間を決定する。フレームの長さは、ビット誤りを発生させるほど大きく伝播遅延ライン特性が変化しないことの十分な見込みを得るように限定される。システムは、各フレームの始点において、再同期する。  (もっと読む)

(もっと読む)

パルス同期復調装置

【課題】高速なパルス無線伝送において、低消費電力で簡易な構成によって受信パルス信号を同期捕捉して復調することのできるパルス同期復調装置を提供する。

【解決手段】オン・オフ・キーイング変調方式による受信パルス信号は、伝送レートの半分の周波数のクロック信号で動作するAD変換部10及び11によってシンボルが交互に標本化される。同期時には、標本化タイミング調整部20及び21の遅延量を異ならせてシンボルパルスの異なる2点の位相を標本化し、得られた標本値の比較に応じて可変遅延部40の遅延量を調整して同期を確保する。復調時には、可変遅延部40の遅延量を保持して、標本化タイミング調整部20及び21の遅延量を同じ値に切り替えてシンボルパルスを交互に標本化し、得られた標本値を復調処理部60において閾値判定して、結果を並列直列変換することで復調出力を得る。

(もっと読む)

送信装置、受信装置、伝送システム、変調方法、および復調方法

【課題】コスト高、大型化を招くことなく、スキューの発生を抑止でき、多値信号の伝送を、分解能を劣化させることがなく、効率的に行うことができる送信装置、受信装置、伝送システム、変調方法、および復調方法を提供する。

【解決手段】3ビット(8値)の振幅多値変調信号に変換し、その変調信号の先頭または最後尾に2値で反転するフレーム同期信号FSYNCを付加して伝送することで1本のシリアルデータとして伝送する送信装置2と、送信装置2から受信したフレーム同期信号FSYNCに基づいて、クロック信号CLK2を再生し、再生したクロック信号CLK2に基づいて受信したデータ信号のサンプリング等によりアナログ・デジタル変換を行って、データ再生(復調)を行う受信装置3とを有する。

(もっと読む)

自動終端回路

【課題】自動終端回路を提供すること

【解決手段】自動終端回路は、それ自体を伝送線路に接続するための出力端子を有する可変終端抵抗デバイスを含み、可変終端抵抗デバイスは、付随する終端抵抗を有する。自動終端回路は、帰還を用いて可変終端抵抗デバイスに付随する終端抵抗を自動的に調整するように動作可能であり、帰還は少なくとも出力端子での出力電圧に基づく。

(もっと読む)

通信装置

【課題】コストを削減することができるとともに、小型軽量化を図ることができる「通信装置」を提供すること。

【解決手段】アナログ信号とデジタル信号とが混在された信号から、アナログ信号取得手段33によってアナログ信号のみを取得し、デジタル信号取得手段34によってデジタル信号のみを取得することによって、通信情報を含むアナログ信号の送受信と、通信情報を含むデジタル信号の送受信とを、ケーブル5における同一の芯線10を用いて行うこと。

(もっと読む)

送信装置、受信装置、送信方法、受信方法及び集積回路

【課題】誤り訂正情報を持たないシリアル通信により、情報の授受を行う機器において、通信により生じたエラーを修正することが出来る受信装置を提供することを目的とする。

【解決手段】本発明において、受信回路117の備える補完部122は、エラービットに1又は0を補完した2種類の補完ブロックを生成し、判定部127は、前記2種類の補完ブロックのうち、有効ブロックテーブル含まれる有効ブロックと一致する1の補完ブロックを確定ブロックとして採用する。

(もっと読む)

信号伝送システム、信号伝送方法及びプログラム

【課題】シリアルデータバスを用いた多対1ノード間のデータ転送を簡単な構成で良好に行うことができる信号伝送システム、信号伝送方法及びプログラムを提供する。

【解決手段】シリアルバス4を介して複数のスレーブノード3から1つのマスターノード1へのデータ伝送する際、シリアルデータに埋め込まれるクロック信号の位相を予めマスターノード1側の基準クロック信号に合わせることにより、スレーブノード3が切り換わっても再同期のオーバーヘッドが生じないようになる。

(もっと読む)

信号品質最適化装置及び信号品質最適化システム

【課題】高速なシリアル伝送における信号の品質を最適化する装置及びシステムを提供する。

【解決手段】受信部1は、受信データを入力するとともに、前記受信データの補正を指示する調整制御信号を入力した場合には前記調整制御信号に従って前記受信データを補正して出力し、前記調整制御信号を入力しない場合には前記受信データを補正せずに出力するイコライザ11と、

イコライザ11が出力したイコライザ出力データを入力し、入力したイコライザ出力データのBERを計測し、計測したBERの計測結果に基づき前記調整制御信号を生成し、生成した前記調整制御信号をイコライザ11に出力する一連の動作を、イコライザ11から入力するイコライザ出力データのBERが最低になるまで繰り返すBER計測機能部13とを備えた。

(もっと読む)

データ転送装置

【課題】複数の入出力回路の間で高速のデータ信号を転送するデータ転送装置において、転送エラーの発生を低減すること。

【解決手段】各データ処理装置10は、他のデータ処理装置からテスト信号を受信し、入出力回路101がこれを正しく受信できたかどうかを判定する比較器110と、入出力回路に対し、信号入力時の基準となる参照電圧を与えるとともに、比較器の判定結果、正しく受信できるための最適な参照電圧を求めて記憶部208に記憶する参照電圧制御回路102とを備える。参照電圧制御回路102は、データ送信元となるデータ処理装置毎に参照電圧の最適値を求めて記憶部208に記憶する構成とする。

(もっと読む)

同時スイッチングノイズを低減するプリアンブルを含むDCバランスエンコーディングされたデータのための送受信方法及びシステム

【課題】同時スイッチングノイズをさらに減少させる方法及びシステムを提供する。

【解決手段】DCバランスエンコーディングされたデータの最初のワードの伝送に起因した同時スイッチングノイズを減らすために所定のロジック値を有する少なくとも一つのビートであるが、前記DCバランスエンコーディングされたデータで前記所定のロジック値を有するビットの最大数未満である前記所定のロジック値を有する中間数のビットを提供するように構成されるダミーデータであるプリアンブルを伝送することによって、前記DCバランスエンコーディングされたデータは伝送される。前記プリアンブルは、一つ以上の固定及び/または可変ダミーデータを含みうる。

(もっと読む)

終端抵抗調整方法、半導体集積回路及び半導体装置

【課題】本発明は、終端抵抗調整方法、半導体集積回路及び半導体装置に関し、半導体装置内の終端抵抗を最適な抵抗値に設定するためのキャリブレーションを正確に行うことを目的とする。

【解決手段】第1のノードと電源電圧及び接地電圧の一方との間に接続された電流源回路と、第1のノードと電源電圧及び接地電圧の他方との間に並列接続可能に設けられた複数の第1の抵抗を備えたモニタ用抵抗部と、第2のノードと前記他方との間に並列接続可能に設けられた複数の第2の抵抗を備えた終端抵抗部と、第1のノードの電圧と基準電圧とを比較して比較結果を出力する比較回路と、キャリブレーションを行う時には、比較結果に基づいてモニタ用抵抗部の第1の抵抗を選択的に並列接続する制御部と、第2のノードに接続された外部端子とを備え、終端抵抗部の抵抗値を制御する時には、制御部は比較結果に基づいて終端抵抗部の第2の抵抗をモニタ用抵抗部の第1の抵抗と同様の構成に選択的に並列接続するように構成する。

(もっと読む)

デジタルオーディオインターフェース信号復調回路

【課題】回路規模と消費電力を増大させずに、基準クロックの変更に回路を変更することなく対応できるようにする。

【解決手段】レート判別部101によって、基準クロックの立上りエッジ、または立下りエッジの何れか一方を用いて、デジタルオーディオインターフェース信号の変化点から次の変化点までの区間長を基準クロックのサイクル数で計数して、サンプリング周波数を判別する。次に閾値決定部103によって、判別したサンプリング周波数に対応した閾値を、閾値テーブル102から呼び出し、その閾値に基づいて、デジタルオーディオインターフェース信号中のパルスが、複数種類の単位パルスの何れに対応するかをパターン判別部104で判別する。そして、ビット抽出・プリアンブル検出部105で、パターン判別部104の判別結果に基づいて、同期パターンの検出および復調したデジタルオーディオ信号を出力する。

(もっと読む)

同時双方向データ送受信システム

【課題】 トランスペアレントが保証され、正確に且つ高速なデータ伝送が行える1本の伝送線路による同時双方向送受信を可能にすることにある。

【解決手段】 パラレルデータTPDをパラレル−シリアル変換回路1aでシリアルデータTSD0に変換する。このシリアルデータは伝送線路上の直流バランスを保障していないデータである。このシリアルデータを符号化回路1cにより伝送線路上の直流バランスを保障できるシリアルデータTSD1、例えば、マンチェスタコードによるデータに変換し、データ送受信回路1dを介して伝送線路1e上に送出する。データ送受信回路1dは伝送線路1e上の信号から受信信号RSD1のみを抽出し、複合化回路1fで元のシリアルデータRSD0を得ると共に同期信号CLK3を抽出し、得られたシリアルデータをシリアル−パラレル変換回路1gでパラレルデータRPDに変換する。

(もっと読む)

ビット変化低減符号化装置及び方法、ビット変化低減復号化装置及び方法、データ送信装置及び方法、並びに、データ受信装置及び方法

【課題】 画像データの転送速度を維持しながら、シリアル伝送路における高周波成分を低減可能なシリアル伝送装置を提供する。

【解決手段】 画像データ送信装置10において、送信対象画素データPBD1と送信対象画素データと隣接する隣接画素データPBD2に対して2回の排他的論理和処理を行って隣接するビット間の変化を低減させる等ビット長変換を行うビット変化低減符号化装置11と、等ビット長変換された画素データPBD7をシリアルデータSBD7に変換するパラレルシリアル変換装置12を備え、画像データ受信装置15側において、受信したシリアルデータSBD7を画素データPBD7に変換するシリアルパラレル変換装置17と、隣接画素データPBD2を用いて画素データPBD7に対して等ビット長変換の逆変換を行うビット変化低減復号化装置18を備える。

(もっと読む)

振幅判定値設定方法

【課題】 伝送系における群遅延及び電界強度の低下などによりディジタル映像信号に歪みが生じた場合でも、デコードエラーの発生率を低く抑えることのできる振幅判定値設定方法を提供する。

【解決手段】 所定の期間、入力信号を2値化およびデコードして、デコードデータのエラーの数をカウントすると、振幅判定値に対して、所定のステップ値で終了値に近づくように演算処理を行い、振幅判定値を更新する振幅判定値更新ステップと、開始値から終了値まで所定のステップ値で振幅判定値を変更しながら取得した、振幅判定値を各値とした場合のエラーの数より、エラーの数が最小となる振幅判定値を最適な振幅判定値として選択する振幅判定値選択ステップとを備えた。

(もっと読む)

141 - 160 / 251

[ Back to top ]