Fターム[5K029DD29]の内容

直流方式デジタル伝送 (8,390) | 伝送システム構成 (1,787) | 受信機;受信局 (155)

Fターム[5K029DD29]に分類される特許

1 - 20 / 155

信号伝達装置及びこれを用いたモータ駆動装置

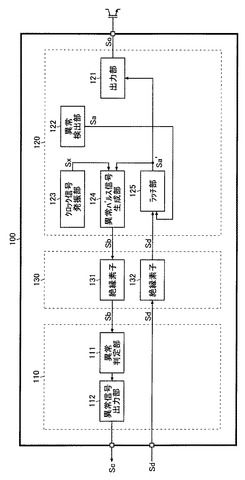

【課題】ドライバチップの異常検出期間が短過ぎると、異常パルス信号のパルス生成が停止された後、異常判定期間の経過前に異常パルス信号のパルス生成が再開されてしまい、コントローラチップでドライバチップの異常を認識することができなくなるおそれがあり、2つの回路を絶縁しつつ一方の異常を確実に他方に伝達することのできる信号伝達装置、及びこれを用いたモータ駆動装置を提供する。

【解決手段】信号伝達装置100は、第1回路110と第2回路120との間を絶縁しながら信号伝達を行うものであり、第1回路110は、第2回路120から伝達される異常パルス信号Sbを監視して第2回路120の異常有無を判定し、第2回路120は、第2回路120で異常が検出されてから少なくとも第1回路110で第2回路120の異常有無が判定されるまで異常パルス信号Sbを異常状態に保持する。

(もっと読む)

通信システム

【課題】比較的安価な構成でリンギング現象を効果的に抑制可能な通信システムを得る。

【解決手段】幹線20の分岐点N1及びN3からそれぞれ放射状に6本の支線21、分岐点N2から図中上下に2本の支線22、合計14本の支線21及び22が接続される。なお、12本の支線21はそれぞれ第1の長さで設けられ、2本の支線22は上記第1の長さより長い第2の長さで設けられる。14本の支線21の端部に14個の非終端ECUであるECU2〜ECU15が接続される。ECU2〜7及び10〜15はそれぞれ抵抗値1800Ωの抵抗R2を有している。さらに、ECU8及び9はそれぞれ抵抗値600Ωの抵抗R3を有している。これら抵抗R2及び抵抗R3はリンギング現象抑制用の補助抵抗として機能する。

(もっと読む)

バイポーラ/ユニポーラ変換回路

【課題】入力信号の振幅レベルが変化した場合でも、最適なバイアス値を設定する。

【解決手段】バイポーラ/ユニポーラ変換回路1は、入力信号Iと正極バイアス値V(+)及び負極バイアス値V(−)とを比較し、比較の結果に基づき入力信号をRZ信号に各々変換するRZ変換回路2及び3と、各々のRZ信号の論理和を演算する論理和回路4と、論理和回路4から出力された両極RZ信号AをNRZ信号に変換するNRZ変換回路7と、両極RZ信号に基づき、入力信号の入力状態を検出する入力断検出回路10と、入力断検出回路10の検出結果に基づき、正極及び負極バイアス値を設定するバイアス設定回路12と、各々のRZ信号が所定の符号化規則に従っているか否かを検出する符号則誤り検出回路11とを備え、バイアス設定回路12は、各々のRZ信号が符号化規則に従っていないことが検出された場合に、正極及び負極バイアス値を設定する。

(もっと読む)

電子機器、電子機器の制御方法および電子機器システム

【課題】ビデオ信号などのデジタル信号を他の電子機器との間で双方向に効率よく伝送可能とする。

【解決手段】シンク機器130とシンク機器140は例えば別部屋に配置されたテレビ受信機である。シンク機器間はケーブル300により接続される。このケーブル300には、Data0〜Data5の6本の差動信号レーンが用意され、機器間でデジタル信号の双方向伝送が可能である。また、ケーブル300には、双方向通信ラインが用意されている。この双方向通信ラインは、例えば、HDMIのCECラインと同等の双方向制御ライン、あるいは、双方向差動通信ラインとして構成される。機器間でデジタル信号を伝送する際、機器間で双方向通信ラインを利用して通信が行われ、使用レーン数、使用レーン番号、伝送方向、搬送クロック周波数などの伝送路構成が決定される。この決定に基づいて、各機器のデータ送受信部132,142における伝送路構成が制御される。

(もっと読む)

送受信装置及び信号伝送装置

【課題】一対の信号線からなる差動信号線に接続された送受信部が差動信号線を介して送信側又は受信側の何れに接続された場合にも通信を行うことが可能な送受信装置、及びそれを備えた信号伝送装置を提供する。

【解決手段】送受信装置1は、第1の信号線21及び第2の信号線22からなる差動信号線20を介して送信側又は受信側に接続され、送信側に接続されたときは第1の信号線21によって信号を受信し、受信側に接続されたときは第2の信号線22によって信号を送信する送受信部10と、送受信部10によって送信又は受信される信号を処理する信号処理部14とを備える。

(もっと読む)

超広帯域無線通信装置

【課題】10GHz程度の超広帯域を簡易な構成で利用可能とすることで、短距離高速通信を低価格で実現可能とする超広帯域無線通信装置を提供する。

【解決手段】 クロック153aをクロック152aより所定時間だけ遅らせることで、入出力処理部153は入出力処理部152より所定時間だけ遅れて動作するようにしている。バイアス手段154は、入出力処理部153からトリガ信号22が入力されると、これに一定のバイアスを付加している。コンパレータ155は、入出力処理部152からトリガ信号21を入力するとともに、バイアス手段154からバイアスが付加されたトリガ信号22を入力し、トリガ信号21がトリガ信号22よりも大きいときだけ、所定の出力を行うよう構成されている。

(もっと読む)

パルス信号受信装置及び伝送システム

【課題】ノイズの影響による伝送エラーの発生を抑えることができるパルス信号受信装置及び伝送システムを提供する。

【解決手段】パルス信号受信装置20は、ダブルエッジ変調方式によって変調されたパルス信号PSを受信する受信部21と、受信部21で受信されたパルス信号のエッジ間隔を測定するエッジ間隔測定タイマ22aと、パルス信号PSの幅の基準値を示すパルス幅基準値に対するエッジ間隔測定タイマ22aで測定されたエッジ間隔の偏差を検出するパルス幅偏差検出部22cと、パルス幅偏差検出部22cで検出された偏差を用いてエッジ間隔測定タイマ22aで次に測定されるエッジ間隔を補正するパルス幅補正部22bと、パルス幅補正部22bで補正されたパルス信号を復号してディジタル信号D2を得るパルス幅デコード部23とを備える。

(もっと読む)

信号断検出回路、信号断検出方法及び光受信器

【課題】異なるビットレートの信号を時分割で受信した場合においても、ビットレートに関係なく信号断検出時のビットエラーレートを等しくし得る信号断検出回路を提供する。

【解決手段】信号断検出回路1は、複数のビットレートのそれぞれに固有の光受信レベルの閾値(201,601)を用い、信号入力部10の出力信号102に含まれる当該各ビットレートの信号についてその有無を検出する信号検出部(20,60)と、信号入力部10の出力信号102が複数のビットレートのいずれに属するかを判別するビットレート判別部70と、ビットレート判別部70で判別されたビットレートについて信号検出部(20,60)が信号の無を検出した場合に、信号断を示す信号(ローレベル電圧のLOS信号804)を出力する信号断アラーム生成部80と、を備えたことを特徴とする。

(もっと読む)

単一導体上のデータの非同期通信のための方法と装置

【課題】 単一導体上のデータの非同期通信のための方法と装置を提供する。

【解決手段】 本発明は、集積回路チップ内部または集積回路チップ間、例えば小型積層チップ内に存在する複雑な集積システムにおけるデータの非同期通信に関する。本発明によると、送信は単一交換導体上で行われる。データは、送信データ項目の第1の値を表す第1のレベル(0)、送信データ項目の第2の値を表す第2のレベル(Vdd)、および非活性レベルを表す第3のレベル(Vmed)の少なくとも3つのレベルの電位の形式でこの導体Cech上に送信される。確認応答信号がデータと同じ交換導体上に送信される。この信号は好ましくは、受信器により交換導体を非活性電位レベルに強制設定する形式で、受信器により生成され、送信器はこの強制設定を検出する。

(もっと読む)

受信回路、送信回路、通信システム、及び通信システムの送信設定方法

【課題】信号遷移発生用の符号化を用いることなくデータとクロックとを1つの信号に纏めて送受信可能な送信回路及び受信回路を提供する。

【解決手段】送信回路は、データ信号とクロック信号とを重み付け加算することにより生成した信号を送信する。また受信回路は、受信した第1の信号の信号遷移からクロック信号を抽出するクロック抽出回路と、抽出されたクロック信号を第1の信号から減算することにより第2の信号を生成する減算回路と、抽出されたクロック信号に応じたタイミングにおいて第2の信号をデータ判定するデータ判定回路とを含む。

(もっと読む)

受信回路

【課題】ビット幅の広いデジタル演算を必要とせずに、小さい回路面積及び消費電力で適応等化処理を実現できる受信回路を提供する。

【解決手段】受信回路は、等化係数に応じた等化処理を受信信号に施して等化された信号を出力する等化回路と、等化された信号と第1閾値との大小関係に応じた0及び1の信号値を有する第1の信号を求め、等化された信号と第2閾値との大小関係に応じた0及び1の信号値を有する第2の信号を求め、第1の信号中に現れる所定の0及び1のパターンの出現回数と第2の信号中に現れる所定の0及び1のパターンの出現回数との差分を計算する誤差計算回路と、差分に応じて等化係数を調整する適応等化制御回路とを含む。

(もっと読む)

送信装置、送信方法、受信装置、受信方法、送受信システムおよびケーブル

【課題】後方互換性を確保しつつ、高いデータレートでの信号伝送を可能する。

【解決手段】ソース機器110およびシンク機器120をHDMIケーブル200により接続する。ソース機器110は、現行HDMIおよび新HDMIの双方に対応している。ビデオデータ等のデジタル信号を伝送するための差動信号チャネルは、現行HDMIが3チャネルであるのに対して、新HDMIでは例えば6チャネルとされる。ソース機器110の制御部113は、ケーブル200が新HDMIに対応し、かつシンク機器120が新HDMIに対応している場合、データ送信部112を新HDMIの動作モードに制御する。一方、制御部113は、少なくとも、シンク機器120が現行HDMIにのみ対応していると判断する場合、あるいはケーブル200が現行HDMIに対応していると判断する場合、データ送信部112を現行HDMIの動作モードに制御する。

(もっと読む)

通信装置および通信装置の製造方法

【課題】通信回路に供給されるシステムクロックの異常検出の確実性を高めることができる通信装置を提供する。

【解決手段】CMOS回路を有するシステムクロック生成回路3は、周波数f1を持つシステムクロックSCKを生成する。CMOS回路を有する監視クロック生成回路4は、周波数f1より低い周波数f2を持つ監視クロックWCKを生成する。通信制御回路5は、システムクロックSCKの供給を受けて動作し、バス通信線2を通じて外部機器との通信を行う。クロック監視回路7は、システムクロックSCKの周波数と監視クロックWCKの周波数との相対関係を監視する。クロック監視回路7は、その相対関係が変化するとシステムクロックSCKが異常であると判断し、異常検出信号Saを出力する。通信I/F回路6は、異常検出信号Saが出力されるとバス通信線2を開放する。

(もっと読む)

伝送回路および信号伝送方法

【課題】主信号および補助信号を少ない配線数の伝送路で伝送する信号伝送技術を提供する。

【解決手段】主信号および補助信号を伝送する伝送回路は伝送路と重畳・分離部とを有する。重畳・分離部は、主信号を伝送路に送信する送信回路と伝送路から主信号を受信する受信回路のいずれか一方または双方に備えられ、伝送路上の信号に自回路からの補助信号を重畳し、伝送路上の信号から、自回路からの補助信号と他回路からの補助信号のいずれか一方または両方を分離する。

(もっと読む)

伝送装置、及び誤り訂正データの付加方法

【課題】比較的良好な伝送路において多値データに生じる隣接レベルへの誤りを効率的に訂正可能な誤り訂正データの付加方法を提供すること。

【解決手段】K値データが取り得るレベル値Li、Li+1に対応する2ビット値Bi、Bi+1の間のハミング距離が1であり、かつ、レベル値Lj、Lj+2に対応する2ビット値Bj、Bj+2が互いに異なるように、前記K値データを、対応する2ビット値の列に変換する第1の2値化ステップと、前記第1の2値化ステップにおける変換で得られた2ビット値の列から、1ビット誤り訂正機能を持つ誤り訂正データを算出する誤り訂正データ算出ステップと、前記誤り訂正データ算出ステップにて算出された誤り訂正データをK値の誤り訂正データに変換して前記K値データに付加する誤り訂正データ付加ステップと、を含む、誤り訂正データの付加方法が提供される。

(もっと読む)

通信信号処理装置及び通信装置

【課題】反射波の影響による通信信号の誤判定を生じにくくする。

【解決手段】レシーバ140では、コンパレータ141が、第1通信線11及び第2通信線12の電位差がしきい値を上回る場合にドミナントを表す信号をRx信号(受信信号)として通信コントローラへ出力し、その電位差がしきい値以下である場合にレセッシブを表す信号をRx信号として通信コントローラへ出力する。また、ワンショットトリガタイマ回路144が、ドミナントからレセッシブへの変化時から一定時間の間はハイレベルの信号を出力することによりアナログスイッチ145をオン状態にして第1通信線11及び第2通信線12を短絡する。したがって、その一定時間の間は、第1通信線11及び第2通信線12を介して受信される通信信号に関係なく、レセッシブを表す信号がRx信号として通信コントローラへ出力される。

(もっと読む)

障害予知ユニット

【課題】デバイスへの入力信号が高周波かつ低振幅であっても障害発生を正確に予知することが可能であり、かつ、回路規模の大型化及び高コスト化を抑えることが可能な障害予知ユニットを提供する。

【解決手段】障害予知ユニットは、レベル低下部と、第1及び第2のバッファゲートと、比較部と、処理部とを具備する。レベル低下部は、入力されたデジタル信号の信号レベルを所定のレベルだけ低下させた低下信号を生成する。第1のバッファゲートは、前記デジタル信号に基づいて第1の出力信号を生成する。第2のバッファゲートは、前記低下信号に基づいて第2の出力信号を生成する。比較部は、前記第1及び第2の出力信号を比較し、前記第1及び第2の出力信号が一致か不一致かを示す比較結果を生成する。処理部は、前記比較結果に基づいて、将来的に障害が発生するか否かを判断する。

(もっと読む)

半導体集積回路装置

【課題】外部のデバイスに接続される回路とLSI内部の回路との間におけるタイミング設計を不要とすること。

【解決手段】半導体集積回路装置は、外部デバイスに対して接続されるインタフェース回路であって第1のクロック信号が供給される第1の回路と、第1のクロック信号を分周した第2のクロック信号が供給される第2の回路と、第2のクロック信号を第1のクロック信号に基いて遅延させた送受信タイミング信号を生成するタイミング生成回路と、第2の回路から受信した信号を第1のクロック信号に同期してサンプリングする複数段のシフトレジスタと該複数段のシフトレジスタに対する入出力信号に含まれるハイレベルの信号とロウレベルの信号の多数決を送受信タイミング信号に同期して行うとともに多数決により決定された信号を第1の回路に出力する多数決回路とを有する第1の位相調整回路とを備えている。

(もっと読む)

時刻情報取得装置、および、電波時計

【課題】 演算量および演算時間を少なくしつつ、正確に標準時刻電波に含まれる符号を取得する。

【解決手段】 平均値追従回路19は、受信回路16からの入力信号から直流成分を除去して、当該入力信号の平均値を中心として、当該平均値より大きい値および平均値より小さい値の何れかを示す出力信号を生成する。信号比較回路18の相関値算出部25は、入力波形データの平均値および予測波形データの平均値の算出を行なうことなく、入力波形データのデータ値と、予測波形データのデータ値とを乗算して演算値を算出し、当該演算値の総和を、入力波形データと予測波形データとの間の共分散値に相当する相関値として算出する。たとえば、CPU11は、最適値を示した予測波形データに基づいて、タイムコードにおける秒先頭位置を特定する。

(もっと読む)

クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法

【課題】クロック情報及びデータ情報を含む信号を受信する受信器、並びにクロック埋め込みインターフェース方法を提供する。

【解決手段】クロック情報及びデータ情報を含む差動信号対を受信するにおいて、差動信号対の共通電圧レベルの変化を利用してクロック信号及びデータを復元できる、クロック情報及びデータ情報を含む信号を受信する受信器及びクロック埋め込みインターフェース方法である。

(もっと読む)

1 - 20 / 155

[ Back to top ]