Fターム[5K029GG01]の内容

直流方式デジタル伝送 (8,390) | 送信部 (677) | 情報源との同期 (14)

Fターム[5K029GG01]に分類される特許

1 - 14 / 14

通信システム,トランシーバ

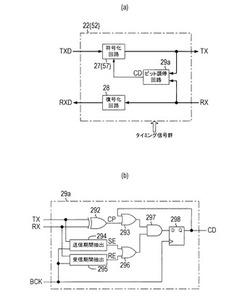

【課題】調歩同期式のシリアル通信をバス通信路に適用した通信システムにおいて応答性のよい多重通信を実現する。

【解決手段】符号化復号化部22において、符号化回路27は、UARTから出力されるブロックデータからなるNRZ符号の送信データTXDを、伝送路符号(PWM符号)に符号化し、復号化回路28は、バス通信路から取り込んだ受信データRXをNRZ符号に復号化する。ビット調停回路29は、符号化前の送信データTXDと復号化後の受信データRXDをビット単位で比較し、信号レベルが不一致である(調停負けした)場合にハイレベルとなる衝突検出信号CDを出力する。この衝突検出信号CDの変化に従い、符号化回路27は、UARTから出力中のブロックデータの送出が終了するまでの間、データバス通信路上へのデータの出力を中止する。

(もっと読む)

長距離光伝送装置、及び長距離光伝送システム

【課題】長距離伝送路区間における通信速度がより高速化しても、比較的簡素な構成で安定した通信を実現する。

【解決手段】40Gbpsで通信を行うメディアコンバータ6,8は、光トランシーバ20、フレーム処理部22、FEC24〜30、長距離TR32〜38、及び波長フィルタ40を備えている。また、これらの間では、電気信号を4本のレーンでパラレル転送する。FEC24〜30、及び長距離TR32〜38は10Gbpsの通信速度に対応しており、各レーン別に転送された電気信号に対してFECを生成し、電気信号を光信号に変換する。

(もっと読む)

クロックド・シリアル・インタフェース

【課題】様々な波形のコントロール信号を生成し出力できるクロックド・シリアル・インタフェース(CSI)を提供する。

【解決手段】コントロール信号の波形を決定するパターンデータが書換可能に格納される複数のシフトレジスタと、これらシフトレジスタ内のパターンデータに応じてコントロール信号を生成する生成手段と、を備える。具体的には、CSI60は、3つのシフトレジスタ81,82,83を有し、これらシフトレジスタ内のパターンデータに応じた波形のコントロール信号を生成し出力する。

(もっと読む)

信号伝送システム及び受信装置

【課題】ネットワークケーブルに含まれる1対の信号線でオーディオ信号を伝送することができる信号伝送システム及び受信装置を提供する。

【解決手段】デジタルオーディオ信号がLANケーブル10内の一対の信号線を介して受信装置3に平衡伝送され、チャネルクロック(LRCK)及びビットクロック(BCK)は、当該一対の信号線を介して受信装置3に非平衡伝送される。受信装置3では、ビットクロックに基づいてシステムクロック(SCK)が作成され、LRCK、BCK及びSCKに基づいて、デジタルオーディオ信号がアナログオーディオ信号に変換されて出力される。送信装置2及び受信装置3のFG(フレームグランド)の有無にかかわらず、チャネルクロック(LRCK)が正確に送信装置2から受信装置3に伝送されるように、LRCK電位自動補正回路25が受信装置3に設けられている。

(もっと読む)

同時スイッチングノイズを低減するプリアンブルを含むDCバランスエンコーディングされたデータのための送受信方法及びシステム

【課題】同時スイッチングノイズをさらに減少させる方法及びシステムを提供する。

【解決手段】DCバランスエンコーディングされたデータの最初のワードの伝送に起因した同時スイッチングノイズを減らすために所定のロジック値を有する少なくとも一つのビートであるが、前記DCバランスエンコーディングされたデータで前記所定のロジック値を有するビットの最大数未満である前記所定のロジック値を有する中間数のビットを提供するように構成されるダミーデータであるプリアンブルを伝送することによって、前記DCバランスエンコーディングされたデータは伝送される。前記プリアンブルは、一つ以上の固定及び/または可変ダミーデータを含みうる。

(もっと読む)

情報処理装置、及び信号伝送方法

【課題】ヒンジ部に配線される信号線の数を低減させた情報処理装置を提供すること。

【解決手段】直流成分を含まず、かつ、クロックの半周期毎に極性が反転する符号を用いて映像データを符号化して符号化信号を生成する符号化部、第2のモジュールが有する発光素子を駆動するための直流成分を含む駆動信号に前記符号化部で生成された符号化信号を重畳して伝送する信号重畳部を有する第1のモジュールと、前記第1のモジュールから受信した信号に含まれる前記駆動信号と前記符号化信号とを分離する信号分離部、前記信号分離部で分離された符号化信号の極性反転周期を検出し、当該検出結果に基づいて前記クロックを再生するクロック再生部、前記クロック再生部で再生されたクロックを用いて前記符号化信号から前記映像データを復号する映像データ復号部を有する第2のモジュールと、を備える、情報処理装置が提供される。

(もっと読む)

デジタル信号伝送装置及びデジタル信号伝送方法

【課題】クロックのばらつきに対して誤伝送を抑制できる非同期式のデジタル信号伝送装置を提供する。

【解決手段】デジタル信号伝送装置10は、複数チャンネルのパラレル入力信号を第一のクロック信号MCLK1に同期してシリアルデータに変換するエンコーダ20と、シリアルデータを第一のクロック信号MCLK1とは非同期に動作する第二のクロック信号MCLK2に同期して複数チャンネルのパラレル出力信号に変換するデコーダ30とを備える。シリアルデータは、複数チャンネルのパラレル入力信号の論理値の組み合わせに対応して異なる周期と異なるデューティとを有する。

(もっと読む)

データ転送システムおよびデータ送信装置

【課題】オーディオデータと、他の、サブコードデータ、訂正結果フラグ、セクタ情報等の付加情報を同時に転送する場合に、別途に通信線を増加する必要がなく、また、付加情報を足した分、転送速度が遅くなってしまうことのないデータ転送システムを提供する。

【解決手段】転送クロックBCLKによりバイフェーズ変調した付加情報ビットを含む極性変調信号MLRCKを生成し、この極性変調信号MLRCKを、極性信号線を用いて転送クロックのタイミングで伝送する構成とした。

(もっと読む)

符号化装置

【課題】符号効率が良く、かつ簡単に符号化データとの同期をとることができる符号化技術を提供することを目的とする。

【解決手段】符号化装置150は、2ビットの情報データを所定の符号則に従って4ビットの符号化データに変換する。符号化装置で使用される符号則においては、情報データがとり得る4種類のビット列に関して、いずれか1種類のビット列は、ビット位置が連続する2ビットの各値が“1”を示す4ビットのビット列と、全ビットの値が“0”を示す4ビットのビット列とに交互に変換される。そして、その他の種類の各ビット列は、符号化後のビット列が互いに異なるように、1ビットだけの値が“1”を示す4ビットのビット列に変換される。

(もっと読む)

時間依存型デジタル装置を直列に相互接続するためのシリアル・バス・インターフェースおよび方法

【課題】 デジタル・シリアル・バスのためのシリアル・ピアツーピア・インターフェースおよびこれを操作するための方法を提供することにある。

【解決手段】 開示されたシリアル・バス・インターフェースは、スレーブからの応答が期待される定義済み間隔を除き、ほとんどの時間、バス・マスタのドライバ・バッファをアクティブに保持する。これは、スレーブの非終端遠端で反射されたマスタから送信された要求パケットの要求エコーが終端されることを保証するものである。このような信号エコーに関する移動時間は、マスタとスレーブとの間のワイヤ長の距離あるいは伝送ラインの電気特性またはその両方によって定義することができる。スレーブは、要求パケットを受信し、何らかの処理時間を追加し、プログラム可能遅延素子によって遅延された応答を送信することができる。応答パケットは、追加の移動遅延後にマスタに到着することができる。その時点で、要求エコーはすでに終端されており、もはやデータ伝送を妨害しない。プログラム可能遅延素子は、応答パケットがマスタ側に到着する点まで正確に前述の間隔を移動する。このような応答が受信された後、ドライバ・バッファはもう一度活動化され、スレーブ側の一致したドライバ・バッファは非活動化される。アクティブ終端のため、応答エコーは、追加の一往復後にキャンセルされる。その時間中、スレーブ側のレシーバ・バッファ上の入力はすべて無視される。  (もっと読む)

(もっと読む)

中央制御機器と少なくとも1つのローカルデータ処理機器のデータ処理機器インターフェースとの間のデータ線路上でのデータ伝送方法及び装置

本発明は、中央制御機器(ECU)が、データパケット(DP)の要求のためにデータ線路(PDL)を介して周期的に同期パルス(Sync)をデータ処理機器インターフェース(61,62)に送出し、それに対してローカルデータ処理機器(S1,S2)はデータパケット(DP)を中央制御機器(ECU)に送信する、中央制御機器(ECU)と少なくとも1つのローカルデータ処理機器(S1,S2)のデータ処理機器インターフェース(61,62)との間のデータ線路(PDL)上でデータを伝送するための方法及び装置に関する。本発明によれば、ローカルデータ処理機器(S1,S2)が同期パルスの後で第1のデータパケット(DP)の伝送前に電気的な放電パルス(Dis)を生成し、これによって同期パルス(Sync)によるデータ処理機器インターフェース(61,62)の充電に対処する。  (もっと読む)

(もっと読む)

パルス駆動回路及びパルスリンギング抑制回路

【課題】 本発明は、パルス駆動回路及びパルスリンギング抑圧回路において、入力信号が急激に変化するようなとき、例えば、周波数が高く、ゲインが高い時の入力信号の立ち上がり、立ち下がり時の電圧変動を出力信号に伝えてリンギングをリンギング抑制回路により有効に抑える様にする。又、リンギング抑制調整回路の制御信号を切り替えることによってリンギング抑制回路を調整し、入力信号の電圧変動を伝えるゲインと遅延時間をそれぞれ制御することで、リンギングが変化した場合に対してもリンギングを抑制する様に出来るものを得る。

【解決手段】 本発明のパルス駆動回路及びパルスリンギング抑圧回路は、パルス駆動回路1にリンギング抑制回路5a,5bを設け、入力パルスの立下り或いは立下りを出力信号の立ち上がり或いは立下りにより交流的に加算し、出力波形に生ずるリンギングを軽減すると共にリンギング抑制回路5a,5bの遅延量又は/及び遅延時間τを調整可能なものを得る。

(もっと読む)

多重伝送システム

【課題】 有線伝送路を介してベースバンド信号および短パルス変調信号を送受信し、短パルス変調信号を正確に復調することができる多重伝送システムを提供すること。

【解決手段】 第1の送受信部10および第2の送受信部20は、光伝送路30を介して接続されている。第1の送受信部10は、データを変調することによって得られる短パルス変調信号を第1の光信号に変換して、第2の送受信部20に送信する。第2の送受信部20は、ベースバンド信号を第2の光信号に変換して、第1の送受信部10に送信する。第2の送受信部20において、遅延制御部108は、ベースバンド信号の立ち上がり、または立ち下がり期間中に短パルス変調信号のパルスを受信しないように、ベースバンド信号の遅延時間を制御する。また、短パルス変調信号のビットレートは、ベースバンド信号のビットレートの整数倍である。

(もっと読む)

基準信号を用いて同期伝送を行う装置および方法

【課題】 送信装置と受信装置の間で複数ビットのパラレルデータを伝送する際に、ビット間のデータ信号のばらつきを抑えながら高速伝送を実現する。

【解決手段】 送信側チップ701および受信側チップ702は、共通の基準信号から同期信号を生成する。パタン発生器711は、同期信号をトリガとしてトレーニングパタンを発生し、出力回路714は、トレーニングパタンおよび通常データを送信する。入力回路721は、クロック信号の位相を調整して、調整後のクロック信号と受信したデータ信号を出力する。パタン検出器722は、データ信号列からトレーニングパタンを検出してライトポインタ(WP)を初期化し、リードポインタ(RP)は同期信号により初期化される。リングバッファ724では、ライトポインタが示すバッファにデータ信号が格納され、リードポインタが示すバッファからデータが出力される。

(もっと読む)

1 - 14 / 14

[ Back to top ]