Fターム[5K047MM44]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | D/A変換回路 (22)

Fターム[5K047MM44]に分類される特許

1 - 20 / 22

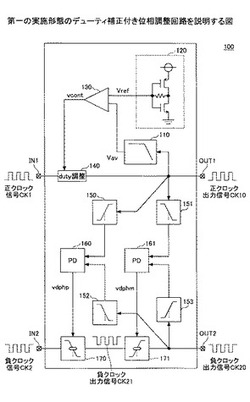

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

クロック再生成回路およびこれを用いたデジタルオーディオ再生装置

【課題】従来のビデオ共用オーディオ再生装置では、PLLを用いるためにオーディオクロック品質が劣化してしまうという課題があった。

【解決手段】一定時間入力クロックをカウントするカウンタと、前記カウンタの出力値を元にして基準クロックを分周する可変分周器と、非同期サンプリングレートコンバータを持ち、前記可変分周器のクロック出力を前記非同期サンプリングレートコンバータの入力クロックとして、前記非同期サンプリングレートコンバータの出力を出力とするように構成する。

(もっと読む)

無線通信装置及び無線通信方法

【課題】受信シンボル用のシンボルタイミングに基づいて送信シンボルを生成し、かつ送信シンボルレートを一定に保つことができる無線通信装置を提供する。

【解決手段】受信シンボルの検出に用いるシンボルタイミング毎に、送信シンボルを生成して変調用のデジタルデータに変換し、FIFO方式の第1のバッファに書き込む変調データ生成手段と、第1バッファから所定速度で前記デジタルデータを読み出してアナログ信号に変換し、搬送波の変調に供するD/Aコンバータとを備えた無線通信装置において、第1バッファが保持するデータ数を適切に維持すべく、前記シンボルタイミング毎に生成する送信シンボルの数を制御する制御手段(ステップ52〜61)を設ける。

(もっと読む)

ストリーミングデータ補償方法およびデジタル信号受信装置

【課題】非同期パケット通信におけるストリーミングデータ補償方法であって、パケット不足およびパケット過剰のいずれにも対応可能であり、1パケットに多くの補償を行わなくてすむストリーミングデータ補償方法を提供する。

【解決手段】本受信機は送信装置から送信されたパケット化されたデータを受信する受信機1と、DSP2で構成されたパケット補償部およびパケット補償部から出力されたデジタル信号を音声に変換するデジタル−アナログコンバータ(以下、単に、DAC3とする。)を備えている。更に具体的には、パケット補償部には、受信機1から受け取ったパケット化されたデータを順に書き込むライトポインタ(以下、単に、WPとする。)と、r_data_buf21、x_data_buf22およびp_data_buf23の3種類のバッファ、およびバッファのデータを読み込みDAC3に送信するリードポインタ(以下、単に、RPとする。)を備えている。

(もっと読む)

半導体集積回路及びマイクロコンピュータ

【課題】 高精度で内蔵発振を行うことができる半導体集積回路を提供する。

【解決手段】 半導体集積回路は、記憶回路(20)と、外部で生成される外部クロック信号(RCLK)の周波数に内部クロック信号(VCLK)の周波数を一致させる制御情報を生成し前記記憶回路に格納する論理回路(2)と、前記記憶回路に保持された制御情報に基づいて内部クロック信号を生成する発振回路と、前記制御情報を格納する不揮発性記憶装置(6)と、を有し、前記内部クロック信号を内部回路の同期動作に用い、前記不揮発性記憶装置に格納された前記制御情報は前記半導体集積回路のリセット後、前記記憶回路にロードされる。

(もっと読む)

デジタルテレビ放送の音声同期装置

【課題】VCXO及び高周波数のクロックを使わずにデジタルテレビ放送の音声同期装置を提供すること。

【解決手段】デジタルテレビ放送の音声同期装置は、入力クロックを逓倍した一定周波数のクロックを所定の分周比で分周して基本クロックを発生するクロック発生部と、放送波に含まれる基準時間情報とクロック発生部が発生した基本クロックでカウントした時間情報を比較する比較部と、比較部で得られた時間差分に関する情報に基づいて、クロック発生部に基本クロックの周波数の調整を指示する制御部と、基本クロックに基づいてサンプリングクロックを生成するサンプリングクロック生成部と、オーディオサンプリングクロック及び放送波に含まれる音声データを、音声DACのサンプリングクロックと同期するようサンプリング変換するサンプリングレート変換部を備える。クロック発生部は、制御部からの指示に応じて、分周比が異なるクロックを所定のクロックパルス数間隔で挿入する。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

コンテンツデータ送受信システム、コンテンツデータ送信装置、コンテンツデータ受信装置、コンテンツデータ送信方法、コンテンツデータ受信処理方法

【課題】IEC60958(IEC61937)によりDSD信号を適切に伝送可能とする。

【解決手段】送信装置は、IEC61937に対応するサブフレームに対して、DSD信号を16ビットずつ格納し、Cビットにより形成されるチャンネルステイタス情報においては、Additional format informationを“001”としてDSD信号であることを示す。さらに、サブフレームにおけるtime slot27には、“0”を格納して、IEC61937で規定するシンクワードPaが現れることがないようにし、DSDに未対応の受信装置が、DSD信号のバースト受信を開始してしまうことがないようにする。

(もっと読む)

周波数同期方法及び装置

【課題】デジタル/アナログ変換部の分解能を増やすことなく、また電圧制御発振器の可変範囲を狭くすることなく周波数誤差を低減させることのできる周波数同期方法及び装置を提供する。

【解決手段】局部発振信号により、高周波の受信信号をベースバンドのデジタル信号に変換したときの周波数誤差を丸め処理又は切り捨て処理した後、アナログ信号に変換し、該アナログ信号に対応した該局部発振信号を生成する。該丸め処理又は切り捨て処理した時の切り捨て成分に対応する周波数のデジタル信号を生成し、この生成したデジタル信号の周波数成分を該ベースバンドのデジタル信号の周波数成分からキャンセルする。

(もっと読む)

光トランシーバ

【課題】送信光信号の伝送速度の精度の劣化を抑えることが可能な光トランシーバを提供する。

【解決手段】本発明の一実施形態に係る光トランシーバ1は、電気信号と参照クロック信号が入力され、電気信号を参照クロック信号に同期して出力する伝送速度補償手段20と、伝送速度補償手段の出力を光信号に変換する電気/光変換手段30と、参照クロック信号を生成する信号発生器40と、信号発生器の温度を検知して当該温度に対応した制御信号を出力する制御回路60とを有し、参照クロック信号の周波数が制御信号により安定化されていることを特徴とする。

(もっと読む)

データフローアダプタ

【課題】第1の要求信号のレートで第1のデータを受け付け、第2の要求信号のレートで第1のデータに対応する第2のデータを送出するアダプタ回路を提供する。

【解決手段】前記回路を、第1の要求信号のレートで変更され得る、3つの命令のうち1つを指示する制御データを生成する制御装置と、第1の要求信号及び制御データに基づき第3の要求信号を送出し、第1の要求信号の活性化毎に、制御データに応じて第3の要求信号を0回、1回、又は2回活性化処理する処理装置と、処理可能な、第3の要求信号の活性化のそれぞれに対して第1のデータの値を記憶し、第2の要求信号の活性化毎に第2のデータを送出するFIFO型メモリとを備える構成とする。

(もっと読む)

デジタル回路、通信装置、及び受信装置

【課題】簡易な構成により、デジタル信号の読み取りを行えるデジタル回路、通信装置、及び受信装置を提供すること。

【解決手段】デジタル信号の入力を受け入れるDA変換部23と、デジタル信号の切替タイミングを示すトリガ信号を取得するクロック信号選択部22と、互いに位相の異なる複数のクロック信号を生成するクロック信号生成部21と、を含み、クロック信号選択部22は、取得したトリガ信号に基づいて、クロック信号生成部21により生成された複数のクロック信号のうちのいずれかを選択し、DA変換部23は、クロック信号選択部22により選択されたクロック信号に基づき、デジタル信号を読み取る、ことを特徴とする。

(もっと読む)

同期信号発生装置ならびにそれを用いる無線通信装置および無線通信システム

【課題】ハンドオーバーなどの無線通信端末の円滑な通信を実現するために、隣接する基地局とのフレームタイミングを同期させるにあたって、該基地局のコストを削減する。

【解決手段】PHS通信部2のフレームタイミングを規定する発振器10の発振周波数が、GPS受信機22によって得られた1PPS信号に基づいて、較正部30のPLL動作によって較正されるようにした同期信号発生装置4において、PHSアンテナ40によって検出された隣接基地局のタイミングと自機のタイミングとの差をフレームタイミング算出部42によって算出し、GPS信号を受信できず、発振器10の自走期間が長くなり、前記算出結果が所定の閾値を超えると、フレームタイミング異常判定部43は出力制御スイッチ44を切換え、発振器10からPHS通信部2への信号を遮断し、通信動作を休止させる。したがって、発振器10に、精度が低く安価な電圧制御発振器11を使用できる。

(もっと読む)

通信機器および通信機器システム

【課題】通信機器において音声データを処理するA/D変換器やD/A変換器の誤動作を抑制することが可能な技術を提供する。

【解決手段】通信機器1は複数の基地局を切り替えてそれらと通信する。通信機器1は自走クロック信号SC8Kに同期して動作するA/D変換器16およびD/A変換器26を備える。A/D変換器16はアナログ音声データSAMDをデジタル音声データSDMDに変換し、D/A変換器26はデジタル音声データRDMDをアナログ音声データRAMDに変換する。通信機器1は、自走クロック信号SC8Kを生成し、当該自走クロック信号SC8Kを、通信中の通信相手機器の動作タイミングに同期した網同期クロック信号NC8Kに同期させる自走クロックPLL部34を更に備える。

(もっと読む)

クロック再生用PLL引込み時間短縮装置

【課題】自走RTS値生成のための自走作成パラメータの計算をする回路の複雑化を回避

【解決手段】CRTS差分周期検出部23は受信RTS値が増減するまでの周期を検出し、CBR信号周波数予測部24はRTS差分周期検出部からのRTS値差分周期からCBR信号周波数偏差を求める。初期演算部25は、CBR信号周波数予測部で予測したCBR信号周波数偏差からVCXO制御用デジタルデータを生成する。PLL30は、初期演算部からのVCXO制御用デジタルデータ、またはCDV吸収バッファからの受信RTS値に基づくVCXO制御用デジタルデータを切替指示信号43により選択してCBR信号のクロックを発生しCDV吸収バッファに供給する。

(もっと読む)

SRTS受信装置

【課題】 周波数が急変した場合でも周波数引込みを高速に行う。

【解決手段】 電圧制御発信回路121は、受信されデジタル化されたRTS情報に基づいてユーザクロックを発生する。N分周カウンタ122は、ユーザクロックをRTS情報の転送周期におけるユーザ信号のビット数で分周してリング信号を出力する。位相比較回路115は、RTS情報とリング信号の位相を比較し、周波数変動検出回路116は、この位相差によりRTS情報の周波数変動を検出する。セレクタ119は、常時は、低速引込み用AMP118の出力を受け入れているが、位相差が所定の閾値以上になると、高速引込み用AMP117の出力を受け入れてD/Aコンバータ120ヘ出力する。

(もっと読む)

デジタルシステム

【課題】PLL回路が発生するクロックを基準クロックとし、入力信号であるアナログ信号をデジタル変換してデジタル処理を施し、処理結果をアナログ変換して出力するデジタルシステムにおいて、PLL回路が発生するクロックに含まれるジッタの影響を最小限に抑制すること。

【解決手段】遅延器4の遅延時間は、デジタル処理回路3と遅延器4の合計遅延時間がクロックのジッタの周期と等しくなるように調整してある。これによって、基準クロックに含まれるジッタ周期の倍数の時間分だけデジタル処理した信号を遅延させてからアナログ変換するので、入力段のA/D変換器2から出力段のD/A変換器5までの遅延時間をジッタ周期と合致させることができ、出力アナログ信号に対するクロックに含まれるジッタの影響を最小限に抑えることができる。

(もっと読む)

クロック再生回路

【課題】映像クロックの総累積値を制御入力としながら、送信側から伝送するクロック情報を小さくすることができるクロック再生回路を提供する。

【解決手段】レジスタ13は、クロックの累積値を自然数Nで除算した剰余であるクロック再生情報を保持し、レジスタ17は、VCXO25のクロックの累積値を前記自然数Nで除算した剰余を保持する。桁上がり・桁下がり判定器18,19はそれぞれ、レジスタ13,17の値から桁上がり又は桁下がりが発生したか否かを判定する。アップダウンカウンタ20は、桁上がり・桁下がり判定器18,19の桁上がり又は桁下がりの回数に応じて値を増減する。乗算器21は、アップダウンカウンタから出力をN倍する。加算器22は、レジスタ13の値とレジスタ17の値との差分値を乗算器21の出力に加算し、これをPLLの制御量とし、VCXO25を制御する。

(もっと読む)

情報信号伝送装置、及び情報信号伝送方法

【課題】 情報信号(例えば、音声信号)を伝送するためにデジタル信号に変換し、伝送後にアナログ信号に変換する場合、該信号が正確に復元されるようにする。

【解決手段】音声信号を例にして説明すると、音声アナログ信号SLA,SRAはAD変換部20によってデジタル信号SLD,SRDに変換されるが、そのためのクロック信号CPはクロック信号発生部21から供給される。伝送された音声デジタル信号SLD,SRDはDA変換部30によってアナログ信号SLA,SRAに変換されるが、そのためのクロック信号CPRBは、クロック信号発生部21にて発生されて受信器3の側に伝送されてきたものである。この装置によれば、AD変換及びDA変換は同一のクロック信号発生部21にて発生されたクロック信号に基づき行われるので、サンプリング周波数を完全に一致させることが可能となり、音声信号を正確に復元することができる。

(もっと読む)

1 - 20 / 22

[ Back to top ]