Fターム[5K047MM50]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | 発振器 (249) | VCO、VFO (145)

Fターム[5K047MM50]に分類される特許

1 - 20 / 145

クロックデータ再生回路

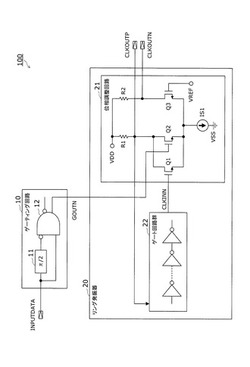

ゲーティッドVCO回路

【課題】ジッタやクロックデューティ比のずれが抑えられた良好なクロック成分を抽出する。

【解決手段】リング発振器20の位相調整回路21において、ゲート回路群22から出力された自走クロック信号CLKINNを入力とするMOSトランジスタQ1、およびゲーティング回路10からのゲーティング信号GOUTNを入力とするMOSトランジスタQ2の並列接続回路と、基準となるレファレンス電圧VREFを入力とするMOSトランジスタQ3とが差動対をなすCML回路を構成し、当該CML回路で得られた自走クロック信号CLKINNとゲーティング信号GOUTNとの論理和またはその反転論理をクロック出力信号CLKOUTとして出力する。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

光受信装置

【課題】連続信号対応の汎用的なCDR回路を備えた制御LSIに、応答特性を損なうことなくシリアルデータ信号を入力する。

【解決手段】光受信装置は、データ信号期間/無信号期間を問わず信号を出力し続けるLA回路6と、LA回路6の出力信号からクロックを抽出しデータを再生するバーストCDR回路2とを備える。バーストCDR回路2は、LA回路6の出力信号とタイミングの合った再生クロックを出力する第1の電圧制御発振器と、第1の電圧制御発振器と同一の周波数で発振する第2の電圧制御発振器と、第2の電圧制御発振器の出力と参照クロックとを周波数比較して、第1、第2の電圧制御発振器を所望のデータレート周波数で発振させる周波数制御信号を出力する周波数比較器と、LA回路6の出力信号の識別再生を再生クロックに基づいて行う識別回路とを有する。

(もっと読む)

クロック・データ再生部及びその電力制御方法並びにPONシステム

【課題】PONシステムの端末装置におけるクロック・データ再生部が省電力状態から起動する時の無駄な電力消費を低減し、かつ、迅速に確実な通信が可能となるようにする。

【解決手段】通常モード又は省電力モードの設定が可能であり、電圧制御型発振器243を含み、入力信号からクロック信号及びデータ信号を抽出する位相ロックループLpを備えたクロック・データ再生部24Aは、参照クロック信号を逓倍して出力する参照クロック逓倍回路249を備えるとともに、同じ電圧制御型発振器243を含み、位相ロックループLpが省電力モードから通常モードに移行する前に、参照クロック逓倍回路249を用いて電圧制御型発振器243による同期発振のトレーニングを行う周波数トレーニングループLfを備えている。

(もっと読む)

CDR回路

【課題】ジッタの抑圧と応答時間の短縮とを両立させる。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO11と、G−VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO12と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ回路3と、入力データ4のデータ信号期間の少なくとも一部において、ゲーティング回路10の出力パルスが再生クロック7に与える影響を、入力データ4の同期信号期間と比較して小さくするよう制御する可変減衰器16とを備える。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

IP受信装置、IP送信装置、およびTS受信装置

【課題】 精度の高いタイミングによる再生を可能にするIP受信装置、IP送信装置、およびTS受信装置を提供する。

【解決手段】 外部のIP送信装置12からIPパケットを受信する受信部41と、受信したIPパケットに基づいて、外部のIP送信装置と当該IP受信装置との同期状態を示すパケットを生成して、外部のIP送信装置12に送信する送信部45をもつIP受信装置13。

(もっと読む)

クロック再生回路及びクロックデータ再生回路

【課題】安定した再生クロック信号を高速に生成することができるクロック再生回路を提供することを課題とする。

【解決手段】クロック再生回路は、入力データに同期して第1のクロック信号をサンプリング及びホールドする第1のサンプルホールド回路(312)と、第1のクロック信号に対して周波数が同じで位相が90度異なる第2のクロック信号を入力し、入力データに同期して第2のクロック信号をサンプリング及びホールドする第2のサンプルホールド回路(313)と、第1のクロック信号及び第2のサンプルホールド回路の出力信号をミキシングする第1のミキサ回路(314)と、第2のクロック信号及び第1のサンプルホールド回路の出力信号をミキシングする第2のミキサ回路(315)と、第2のミキサ回路の出力信号から第1のミキサ回路の出力信号を減算することにより再生クロック信号を出力する減算器(316)とを有する。

(もっと読む)

伝送システム、スレーブ伝送装置及びクロック同期方法

【課題】SYNC盤を設置することなく複数の伝送装置間でクロックの同期をとること。

【解決手段】複数の伝送装置のうちの一つであるマスタ伝送装置は、制御装置から複数の伝送装置に供給される共通のクロックである共通クロックと自装置で用いるクロックであるマスタクロックとの差分値を示す第一の差分値を算出する第一の算出部を備える。また、マスタ伝送装置は、第一の差分値をマスタ伝送装置以外のスレーブ伝送装置に通知する通知部を備える。一方、スレーブ伝送装置は、共通クロックと自装置で用いるクロックであるスレーブクロックとの差分値を示す第二の差分値を算出する第二の算出部を備える。また、スレーブ伝送装置は、マスタ伝送装置により通知された第一の差分値に第二の差分値が一致するように、スレーブクロックを生成する電圧制御発振器を制御する制御部を備える。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

差動4位相偏移変調の位相補間ベースのクロック及びデータの回復

【課題】方法は、N個の入力ストリームを受け取る工程を含む。

【解決手段】N個の入力ストリームおける入力データ・ビットに基づいて、回復されたクロック信号を生成する工程であって、回復されたクロック信号はクロック周波数及び回復されたクロック位相を有する工程と、回復されたクロック位相に対する個別の位相オフセットにおける個別の位相及びクロック周波数を有する回復されたクロック信号に基づいてN個の入力ストリームのうちの一入力データ・ビットストリームに対するクロック信号を生成する工程と、N個のそれぞれのクロック信号と、N個の入力ビットストリームそれぞれとの間の位相差を検出する工程と、それぞれの位相差をなくすようN個のクロック信号の位相を調節する工程である。

(もっと読む)

カメラシステム、信号遅延量調整方法及びプログラム

【課題】複数のカメラを非同期伝送網によって接続した場合に、映像信号のタイミングを確実かつ容易に調整する。

【解決手段】映像を取得する複数のCHU200と、非同期伝送網を介して複数のCHU200のそれぞれに対応して接続され、複数のCHU200のそれぞれから映像信号を取得する複数のCCU300と、複数のCCU300のそれぞれで取得される映像信号の遅延量を映像のフレーム単位で調整するCNU700と、を備える。

(もっと読む)

カメラシステム、信号遅延量調整方法及びプログラム

【課題】複数のカメラを非同期伝送網によって接続した場合に、映像信号のタイミングを容易に調整する。

【解決手段】映像を取得する複数のCHU200と、非同期伝送網600を介して複数のCHU200のそれぞれに対応して接続された複数のCCU300と、複数のCCU30で取得されるCHU200の映像の遅延量が同一となるように調整するCNU700と、を備える。この構成により、複数のカメラを非同期伝送網によって接続した場合に、映像信号のタイミングを容易に調整することが可能となる。

(もっと読む)

クロックリカバリ回路

【課題】データ信号に長期間エッジが存在しない場合でも、データ受信の耐性を損なわず、一定のループゲインを保つクロックリカバリ回路を提供する。

【解決手段】ループフィルタ40は制御電流を制御電圧に変換しかつ平滑して出力し、電圧制御発振器50は制御電圧に対応する周波数を有するクロック信号CLKを発生し、周波数比較回路部10はクロック信号CLKの周波数を基準クロック信号Frの周波数と比較して、比較結果に応じた制御電流をループフィルタ40に出力し、位相比較器21及びチャージポンプ22はデータ信号DATAの位相をクロック信号CLKの位相と比較して、比較結果に応じた制御電流をループフィルタ40に出力し、受信データ長測定回路31はデータ信号DATAのデータ長を測定して期待値と比較し、データ長が期待値以上のときに制御信号S1を出力し、入力電圧制御回路は制御信号S1に応じた制御電流をループフィルタ40に出力する。

(もっと読む)

1 - 20 / 145

[ Back to top ]