Fターム[5L106CC16]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538) | ブロック単位で切り換えるもの (109)

Fターム[5L106CC16]に分類される特許

1 - 20 / 109

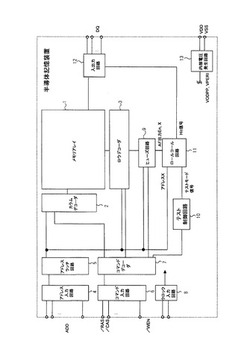

半導体記憶装置及びそのテスト方法

【課題】ロールコールテストに要する工数を削減できる半導体記憶装置及びそのテスト方法を提供する。

【解決手段】不良アドレスが格納される不揮発性の記憶素子を備えた半導体記憶装置にロールコールテスト時にマスク用テストモード信号を出力するテスト制御回路とロールコール回路とを備える。ロールコール回路は、アドレス信号と不良アドレスとをビット単位で比較し、その比較結果を出力する。また、ロールコール回路は、マスク用テストモード信号が入力されると、アドレス信号の所望のビットに対応する比較結果をマスクして上記アドレス信号と不良アドレスとが一致していることを示す値を出力すると共に、マスクされていないビットに対するロールコールテストを可能にする。

(もっと読む)

メモリシステム

【課題】不良メモリチップが発生した場合でも、並列駆動可能な組み合わせ数を最大限確保可能なメモリシステムを提供すること。

【解決手段】物理バンク内の不良メモリチップが識別可能な不良メモリチップ情報に基づき、不良メモリチップを使用せずに各レーン内において並列アクセス可能なメモリチップ数が最大となるように、論理バンクを構成する複数の物理バンクの組み合わせを動的に設定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不良ブロック情報を適切に管理することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は不揮発にデータを記憶する複数のメモリセルを配列してなる複数のブロック、並びにメモリセルと接続されるワード線、及びビット線を有するメモリセルアレイと、メモリセルアレイ内に設けられ、ブロックが不良ブロックであること示す不良ブロック情報を不揮発に記憶可能に構成された不良ブロック格納領域と、ワード線を選択するロウデコーダと、メモリセルに対するデータの書き込み、消去及び読み出しを制御する制御回路とを備える。制御回路は、不良ブロック格納領域に書き込まれた不良ブロック情報をビット線を介して外部へ出力する出力動作を実行可能に構成されるとともに、外部から入力された不良ブロック情報をビット線を介して不良ブロック格納領域に書き込む第1の書き込み動作を実行可能に構成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】製品テストの高速化を実現した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、データを記憶する複数のメモリセルからなるブロックを前記カラム方向に複数並べたメモリセルアレイと、前記ブロックが不良ブロックであることを示す不良ブロック情報を保持する不良ブロック情報保持回路を有するロウデコーダと、複数の前記ブロックからなるブロックグループに対して、当該ブロックグループ内の前記複数のブロックそれぞれに対応する前記不良ブロック情報を同時且つ集約的に参照して当該ブロックグループに不良ブロックが含まれているかを検知する第1検知ステップを実行する不良ブロック検知回路とを備える。

(もっと読む)

半導体記憶装置

【課題】ヒューズセットを用いた冗長セル列の選択の簡易化を図る。

【解決手段】半導体記憶装置は、メモリセルブロック40−1,・・・と、複数の冗長セル列41−11,・・・と、冗長判定信号をそれぞれ出力する複数のアドレス判定回路50−11,・・・と、前記冗長判定信号に基づき、アドレス信号をデコードして冗長セル列41−11,・・・及びメモリセルブロック内のメモリセル列を選択する複数のデコーダ60−11,・・・とを備えている。各アドレス判定回路は、不良メモリセルの位置を示す冗長位置情報を持つヒューズ51a−1〜51a−8と、メモリセルブロックを選択するためのブロック選択情報を持つヒューズ51a−9と、を有するヒューズセット51Aを備え、前記冗長位置情報がアドレス信号と一致するか否かを判定し、この判定結果にブロック選択情報を付加した冗長判定信号を出力する。

(もっと読む)

DRAMをスタックする方法及び装置

【課題】スタックドメモリチップをシグナルインテグリティ等の問題を排除するように構成する。

【解決手段】第1の速度でアクセス可能な複数のセルから構成されるメモリコアを備え、垂直方向にスタックされた複数のDRAM集積回路と、第1の速度よりも大きい速度で、DRAM集積回路とメモリバスとの間でインタフェースを設けるインタフェース集積回路と、メモリスペアリングとを備え、スタックされたDRAM集積回路が(p+q)個のDRAM集積回路を備え、p個のDRAM集積回路が、メモリ集積回路の作業プールとして用いられる複数のDRAM集積回路を備え、q個のDRAM集積回路が、メモリ集積回路のスペアプールとして用いられる複数のDRAM集積回路を備える。

(もっと読む)

メモリシステム

【課題】

実施形態は、信頼性を向上可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、複数のワード線と、複数のビット線と、制御ゲートに前記ワード線が接続され、ドレイン端に前記ビット線が接続されたメモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページごとに不良の前記ビットの個数が第1閾値以下である良ブロックに関するデータが保持された記憶領域とを備え、前記第1閾値は、不良ブロックか否かの判定に用いる第2閾値よりも小さいことを特徴とする。

(もっと読む)

半導体集積回路及びその制御方法

【課題】積層されたチップの面積を効率的に使用し、リペア動作のための非同期パラメータを減少させることができるようにした半導体集積回路及びその制御方法を提供する。

【解決手段】半導体集積回路100は、マスターチップである第1チップ及び第1チップに積層されたスレーブチップである第2チップを備え、第2チップに第1メモリ領域BK0〜BK7が形成されるとともに、第1チップに前記第1メモリ領域の不良をリペアするための第2メモリ領域BK0SRAM〜BK7SRAMが形成される。

(もっと読む)

不揮発性半導体記憶装置の領域設定方法および不揮発性半導体記憶装置

【課題】カンパニー領域専用のブロックが不要な不揮発性半導体記憶装置の領域設定方法を提供する。

【解決手段】不揮発性半導体記憶装置1のメモリセルアレイ2のブロックに不良ブロックが含まれていた場合に、ブロックにユーザー領域とカンパニー領域とを設定する方法において、メモリセルアレイは複数のバンクに分かれていて、各バンクはユーザー領域として使用する複数の通常ブロックと、1つ以上の冗長ブロックとを有していて、カンパニー領域を所定バンクの冗長ブロックに初期設定するステップと、通常ブロックのうちのいずれかが不良ブロックであった場合に、当該不良ブロックの代わりに使用する代替ブロックを、当該不良ブロックが属するバンクの冗長ブロックに設定するステップと、代替ブロックがカンパニー領域と重なった場合に、カンパニー領域を、空いている冗長ブロックに移動させるステップとを有している。

(もっと読む)

不揮発性半導体メモリ

【課題】 読み出し動作を高速に実行し、読み出しマージンを向上する。

【解決手段】 複数の不揮発性のレギュラーメモリセルにそれぞれ接続された所定数のレギュラービット線および所定数のレギュラーワード線とを各々含む一対のメモリ領域を有するレギュラーセクタと、一対のメインビット線と、一対のメモリ領域の間に配置され、一方および他方のメモリ領域のレギュラービット線を一方および他方のメインビット線にそれぞれ接続するスイッチと、リファレンスメモリセル、リファレンスビット線、リファレンスワード線を有するリファレンスセクタと、読み出し動作時に、リファレンスビット線を、データが読み出されるレギュラーメモリセルに接続されるメインビット線と異なるメインビット線に接続するリファレンススイッチと、メインビット線の電圧差を差動増幅するレギュラーセンスアンプとを有している。

(もっと読む)

半導体集積回路装置、制御記憶装置の制御方法及びプログラム

【課題】ブロック単位で構築された冗長構成の利点を最大限利用すると共に、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても対処可能にする。

【解決手段】エラー検出部22は、読み出し制御部21が通常の運用時における制御装置3の動作を規定する通常運用データを冗長メモリ11,12から読み出す前に、通常運用データを格納するブロックに対してチェック処理を行う。当該チェック処理によるエラー情報はエラー情報保持部13に保持させる。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、エラーが検出されたブロックに冗長構成的に対応する健全なブロックが存在するか否かを判定し、健全なブロックが存在する場合には、通常運用データの読み出しを行う。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

半導体集積回路及び制御方法

【課題】LSIの機能増加に伴い外部端子数が増加傾向にある。更に、回路の微細化が進み、パッケージサイズも小型化が進んでいる。このため、LSIの外部端子数の削減が求められている。

【解決手段】本発明は、複数の外部記憶デバイスから1つを選択して、実行プログラムをロードする半導体集積回路であって、複数の内蔵ヒューズ回路を備えるヒューズ部と、前記内蔵ヒューズ回路が示す値に応じて選択した外部記憶デバイスからの実行プログラムをロードする処理部と、を有する半導体集積回路である。

(もっと読む)

不良解析装置及び不良解析方法

【課題】レイヤを跨る不良を検出し、不良タイプの分類を行う。

【解決手段】本実施形態の不良解析装置は、各レイヤに対応するフェイルビットマップにおける不良タイプの分類を行う分類部と、異なるレイヤの不良セルを組み合わせるためのルールを格納する記憶部と、前記分類部による分類結果のうち前記ルールに合致する分類結果をグループ化する判定部と、を備える。前記ルールは、基点不良、前記基点不良の組合せ対象なる関連不良、前記基点不良と前記関連不良との関係を規定する組合せ条件、及び組合せ不良名称を含む。前記判定部は、1つのレイヤの前記分類結果から前記基点不良を抽出し、他のレイヤの前記分類結果から前記組合せ条件に合致する前記関連不良を抽出し、抽出した前記基点不良及び前記関連不良をグループ化して前記組合せ不良名称を付与する。

(もっと読む)

テスト回路及びそれを利用した半導体メモリ装置

【課題】 不良検出率を向上させた半導体メモリ装置のテスト回路及びリペア効率性を向上させた半導体メモリ装置を提供する。

【解決手段】 第1のメモリブロックのメモリセルグループから出力される複数の第1のテストデータ信号を組み合わせて当該メモリセルグループの不良の可否を検出する第1の不良検出部と、第2のメモリブロックのメモリセルグループから出力される複数の第2のテストデータ信号を組み合わせて当該メモリセルグループの不良の可否を検出する第2の不良検出部と、複数の第1及び第2のテストデータ信号を共通的に組み合わせて第1及び第2のメモリブロックのメモリセルグループの不良の可否を検出する共通不良検出部と、第1及び第2の不良検出部の不良検出結果に応じて、第1及び第2の不良検出部の不良検出結果または共通不良検出部の不良検出結果を最終不良検出結果として出力する不良判断部とを備える。

(もっと読む)

半導体メモリ装置のリペア回路及びリペア方法

【課題】効率的にリペアアドレスをプログラミングすることができる半導体メモリ装置のリペア回路及びリペア方法を提供すること。

【解決手段】メモリブロックから出力される複数のテストデータ信号によって不良の可否を判断し、不良と判断されたメモリブロックに該当するアドレスを格納するリペアアドレス検出部と、リペアアドレス検出部に格納されたリペアアドレスを電気的にプログラミングするアンチヒューズ部とを備えることを特徴とする。

(もっと読む)

不揮発性メモリコントローラ及び不揮発性記憶装置

【課題】不良ブロックが発生しても、新たなデータの書き込みが可能な不揮発性メモリコントローラ及び不揮発性記憶装置を提供する。

【解決手段】コントローラ102は、ホスト機器200からの論理アドレスに基づいて物理ブロックに対するデータの書き込み及び/又は読み出しを制御する制御部108と、有効論理アドレス範囲内の1箇所以上の部分領域を論理不良クラスタとし、当該論理不良クラスタの論理アドレスの情報を格納する論理不良クラスタテーブル112と、物理ブロックに格納されるデータの、有効論理アドレス範囲の論理アドレスと物理ブロックの物理アドレスとの対応情報を格納するアドレス変換テーブル109とを備え、制御部108は、論理不良クラスタテーブル112に格納された論理アドレスに対するホスト機器200からのデータの書き込み命令を受けた場合、当該論理アドレスに対するデータの前記物理ブロックへの書き込みの反映を不可とする。

(もっと読む)

半導体記憶装置

【課題】半導体装置におけるヒューズ素子のトリミング時間を短縮する。

【解決手段】メモリアレイARY0、ARY1は、それぞれ正規領域108と予備領域110を含む。ヒューズ回路FS0、FS1は、正規領域108のアドレスのうち予備領域108へのアクセスに代替されるべきアドレスである救済アドレスを記憶する。ヒューズ回路FS0、FS1にそれぞれ対応して救済判定回路RJ0、RJ1が設けられる。救済判定回路RJ0、RJ1は、指定アドレスが救済アドレスか否かを判定する。アクセス制御回路ACは、その判定結果にしたがって、メモリアレイARY0、ARY1からアクセス先を特定する。アクセス制御回路ACは、救済判定回路RJ0により一致判定がなされたときには、CX13T<1:0>にしたがってメモリアレイARY0、ARY1のいずれかを選択し、選択した側のメモリアレイARYに含まれる予備領域110をアクセス先として選択する。

(もっと読む)

不揮発性半導体記憶装置

【課題】ECC動作を消去モードの最初に行うことで、高速読み出し動作可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置10は、データ格納用の不揮発性メモリセルが配列されたメモリ領域(メイン消去ブロック110−2〜110−n)と、メモリ領域が不良領域である場合にメモリ領域と置換される冗長領域(冗長用消去ブロック110−1)と、消去動作を示すコマンドが入力されると、消去動作に先立って前記メモリ領域からデータを読み出し、誤り検出を行い、誤り検出結果に基づいて前記冗長領域へと置換する前記不良領域を検出する制御部(制御部12)と、を備える。

(もっと読む)

半導体装置及びその制御方法

【課題】複数ブロックの消去動作を容易に中断可能な半導体装置及びその制御方法を提供すること。

【解決手段】複数のブロックBLKと前記ブロックBLKを選択するデコーダ11とを備え、複数の前記ブロックBLKにつき一括してデータを消去可能であり、前記デコーダ11が、少なくともデータの読み出し時及び書き込み時には不良ブロック情報を保持し、複数の前記ブロックBLKに対する一括消去時には消去対象となるブロックの情報を保持するNAND型フラッシュメモリ2と、前記消去対象となるブロックBLKの情報を保持可能なSRAM30と、前記一括消去時において、前記消去対象となるブロックBLKの情報を前記SRAM30から読み出して、前記デコーダ11にセットするコントローラ4とを具備する。

(もっと読む)

1 - 20 / 109

[ Back to top ]