Fターム[5L106EE08]の内容

半導体メモリの信頼性技術 (9,959) | 障害・試験箇所 (1,040) | 電源 (43)

Fターム[5L106EE08]に分類される特許

1 - 20 / 43

半導体記憶装置

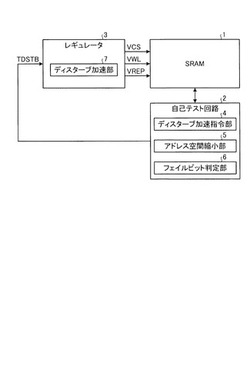

【課題】メモリセルの各トランジスタの特性のランダムばらつきについてのテストを効率化する。

【解決手段】メモリセルMCの動作をテストする自己テスト回路2と、自己テスト回路2からの加速指令に基づいて、メモリセルMCのディスターブが加速するようにワード線WL1〜WLnの電圧VWLまたはメモリセルMCのセル電源電圧VCSを設定するレギュレータ3とを備える。

(もっと読む)

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

半導体装置及びこれを備える半導体システム並びにその動作方法

【課題】内部でデータ基準電圧を生成する半導体装置を提供すること。

【解決手段】本発明の半導体装置は、設定されたデータパターンを有する比較データを外部から印加されて設定された電圧レベル差を有してスイングさせることによって、その論理レベルを明確に区分して格納するデータ格納部と、テスト進入/脱出コマンドにより定義されるテスト動作区間の間に、外部から印加されるレベルテストコードに応答してその電圧レベルが決定されるデータ基準電圧のレベルに基づいて、設定された時間ごとに前記設定されたデータパターンを有する状態で外部から印加されるテストデータの論理レベルを決定し、論理レベルの決定された前記テストデータと前記比較データの論理レベルを比較してテスト結果信号を生成するテスト動作部と、前記テスト進入コマンドに応答してアクティブになり、前記テスト結果信号に応答して非アクティブになるテスト動作測定信号を生成するテスト動作測定信号生成部と、を備える。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

半導体集積回路テスト方法

【課題】複数のメモリを備えた半導体集積回路において、IRドロップによる誤動作を回避しつつ、効率の良いメモリテストを実現すること。

【解決手段】半導体集積回路に含まれる複数のメモリのそれぞれを単体でテストした場合に消費される電流を参照し、該複数のメモリから同時にテストすべき複数のメモリを被テストメモリとして選択する工程と、前記複数の被テストメモリを同時にテストした場合に消費される総消費電流をシミュレーションにより生成する工程と、前記総消費電流および前記半導体集積回路のレイアウト情報に基づいて、前記半導体集積回路におけるIRドロップを算出する工程と、算出した電圧降下が所定の許容値以内であるか否かを判定する工程と、前記電圧降下が前記所定の許容値を超えた場合には、前記複数のメモリから同時にテストすべきメモリを再度選択し直す工程と、を含む。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイの占有面積を低減すると共に、使用する電源の容量および占有面積を低減することができる半導体記憶装置の提供を図る。

【解決手段】オープンビット線方式のコアアーキテクチャを有する半導体記憶装置であって、複数のアレイ領域BK0〜BK8,BK0’を有し、前記各アレイ領域は、当該アレイ領域の両端のエッジ部分に配置され、冗長ワード線WLrdのみを有する2つの冗長アレイブロックBK0,BK0’と、前記2つの冗長アレイブロック間でそれぞれセンスアンプSAを介して交互に配置され、リアルワード線WLrlのみを有する複数のリアルアレイブロックBK1〜BK8と、任意の第1アレイ領域で前記リアルワード線を前記冗長ワード線に置き換えるワード線の冗長処理を行うとき、当該第1アレイ領域の電源容量を増大する電源容量制御手段と、を有する。

(もっと読む)

半導体装置およびテスト方法

【課題】基板電位を生成するためのポンプ容量素子に適したストレス電圧をポンプ容量素子に供給することが可能な半導体装置およびテスト方法を提供する。

【解決手段】所定電位と前記所定電位よりも低い特定電位とを交互に出力するオシレータ回路と、オシレータ回路から出力された、所定電位と特定電位とを受けるポンプ容量素子を含み、ポンプ容量素子の充放電により、出力電位を、目標とする基板電位に下げるチャージポンプ回路と、を有する半導体装置は、ポンプ容量素子のテストの実行を指示するテスト指示信号を受け付けると、所定のストレス電圧をポンプ容量素子に供給するためのテスト電位を、ポンプ容量素子の一端に供給するテスト回路を含む。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

内部電位発生回路

【課題】内部電位のずれを短時間で調整することができる内部電位発生回路を提供することを課題とする。

【解決手段】内部電位発生回路は、参照電位テストモードにおいてクロック信号に同期してカウントを行う参照電位カウンタ(205)と、参照電位カウンタのカウント値に応じた参照電位を生成する参照電位発生回路(203)とを有し、第1の内部電位発生回路は、参照電位テストモードにおいて参照電位カウンタのカウントに並列してクロック信号に同期してカウントを行う第1のカウンタ(225)と、参照電位テストモードにおいて第1のカウンタのカウント値に応じて外部電位を抵抗分割した第1の比較電位を生成する第1の比較電位発生回路(223)と、第1の比較電位が参照電位発生回路により生成される参照電位より低いときには第1の内部電位を昇圧する第1の電位発生回路(226)とを有する。

(もっと読む)

半導体記憶装置及びその回路の電位測定方法

【課題】大規模な半導体記憶装置における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体記憶装置を提供する。

【解決手段】メモリ素子が縦横にマトリックス状に配列されたメモリセルアレイと、接地ノードあるいは電源ノードに接続する枝配線を有する半導体記憶装置において、電源ノードあるいは接地ノードに接続する少なくとも1つの枝配線の複数箇所に電圧測定点を接続したモニター用スイッチを有し、クロック信号に同期して前記モニター用スイッチのゲートを順に開くスイッチ選択信号発生回路を有し、前記スイッチ選択信号発生回路で選択されてゲートが開かれたモニター用スイッチを介して前記電圧測定点の電位を測定する。

(もっと読む)

半導体装置

【課題】欠陥箇所を容易に特定できるようにする。

【解決手段】電気的機能部はアクティブモードおよびスタンバイモードに応じて電気的に動作する。この電気的機能部は、アクティブモードでは複数のノードの電圧が変化して所定の電気的動作を行う。また、電気的機能部は、スタンバイモードでは複数のノードのうち少なくとも2つ以上のノードの電位が同一の所定電位となるが、スタンバイモードにおいて外部コマンドが与えられることに応じて同一の所定電位となる2つのノードに電位差が与えられるように構成されている。

(もっと読む)

半導体記憶装置および半導体記憶装置の試験方法

【課題】ストレス試験の条件設定の自由度が大きく、様々な欠陥を検出可能な半導体記憶装置及び半導体記憶装置の試験方法を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、行列状に配置された複数のメモリセル10と、メモリセルの行毎に対応して配線された複数のワード線WLと、メモリセル10の列毎に対応して配線された複数のビット線対BL、XBLと、テストモードの書き込み期間に、ワード線WLに第1の電圧を印加することでメモリセル10へデータを書き込み、書き込み期間の後のストレス印加期間に、ビット線対BL、XBLにプリチャージ電圧を印加すると共に、前記書き込み期間よりも長い時間、ワード線WLに任意の電圧値である第2の電圧を印加する制御回路と、を有する。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】簡単な構成により、用途が異なるパッドを同一のパッドで兼用することができる半導体装置および半導体装置の制御方法を提供する。

【解決手段】半導体装置100は、共用パッド120と、電源電位を生成する内部発生電源部110と、共用パッド120と内部発生電源110との間を接続状態または非接続状態にするNMOSスイッチ140と、共用パッド120に電源電位と異なる特定電位が供給された場合には、NMOSスイッチ140を非接続状態にするとともに、特定機能を指示する特定指示信号を出力し、共用パッド120に特定電位が供給されない場合には、NMOSスイッチ140を接続状態にする制御部130と、を含む。

(もっと読む)

半導体装置及び半導体装置の評価方法

【課題】大規模なSRAMセルの特性を高精度に測定する半導体装置及びそれを用いた評価方法を提供する。

【解決手段】m行n列のマトリクス状に配列されるSRAMセルを有する評価セルC11〜Cnmと、SRAMセルのSNM特性を測定する際にSRAMのラッチノードへ入力電圧を供給し、或いは出力電圧を検出する第1の主入出力線V0等と、評価セルを選択するための行選択信号供給用の行選択線X1〜Xmと、列選択信号供給用の列選択線Y1〜Ynと、入力される行選択信号と列選択信号に応じてSRAMセルの選択/非選択を表す選択信号を出力する選択回路10と、を備え、選択信号供給回路に入力される選択制御信号等により行選択信号と列選択信号を生成し、評価セル各々に設けられた第1のトランジスタT1〜第6のトランジスタT6を切り替え、SRAMセルの測定評価を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルアレイ内に格納しておいた自装置に関する情報を、起動時に高速かつ低消費電流でシフトレジスタに設定する不揮発性半導体記憶装置を提供すること。

【解決手段】起動時に必要な自装置のデータを格納する不揮発性のメモリセルアレイと、それぞれが複数個のシフトレジスタを有したシフトレジスタR1a〜R1dと、メモリセルアレイ内の自装置に関するデータをFDとしてシフトレジスタR1a〜R1dの何れかに格納させる冗長・トリミング値セット回路11と、を備え、冗長・トリミング値セット回路11は、シフトレジスタR1a〜R1dの何れか1つを順番に指定したFBA<1:0>とFDとをシフトレジスタR1a〜R1dに送信し、シフトレジスタR1a〜R1dは、FBA<1:0>によって自らが指定されている場合に、FDを自らのシフトレジスタに格納する。

(もっと読む)

半導体集積回路

【課題】 ラッチアップの発生を防止し、内部回路に所望のストレスを印加する。

【解決手段】 第1電圧生成回路は、電源電圧より高い第1高レベル電圧を生成する。第2電圧生成回路は、電源電圧より高く、第1高レベル電圧より低い第2高レベル電圧を生成し、バーンイン試験時に停止する。第3電圧生成回路は、電源電圧より低い第3高レベル電圧を生成する。複数の内部回路は、第1高レベル電圧を受けて個別に動作するとともに、バーンイン試験中に動作する。電圧制御回路は、バーンイン試験時に第2高レベル電圧線を第3高レベル電圧線に接続する。寄生トランジスタは、第1高レベル電圧をベースで受け、第2高レベル電圧をエミッタで受ける。複数の内部回路の動作により第1高レベル電圧が一時的に低下するときに、第2高レベル電圧を低い値に設定することで、寄生トランジスタがオンすることを防止できる。

(もっと読む)

半導体装置

【課題】電源スイッチをテストする場合におけるチップ面積の増加を抑える。

【解決手段】SRAM回路ブロックSRB1〜SRB4と、SRAM回路ブロックSRB1〜SRB4の電源端子と半導体装置の電源線との間に並列形態でそれぞれ接続される電源スイッチSW10〜SW13、SW20〜SW23、SW30〜SW33、SW40〜SW43を備える。SRAM回路ブロックSRB1は、SRAM回路ブロックSRB1に係るアドレス信号A0、A1を入力してデコードするデコード回路を含み、デコード回路のデコード結果に応じてSRAM回路ブロックSRB2に対応する電源スイッチSW20〜SW23のそれぞれをオンオフするように制御する。

(もっと読む)

内部電源回路、半導体装置、及び半導体装置の製造方法

【課題】内部電源回路の電流供給能力が過剰となり、無駄な消費電流が発生することを防止する。

【解決手段】内部電源配線19Aを介して半導体装置10の内部回路12に電源電圧を供給する内部電源回路11であって、内部電源配線19Aに共通接続された複数の電力供給部30a〜30cと、複数の電力供給部30a〜30cのうちの少なくとも一部に関し、活性化及び非活性化のいずれか一方を選択する内部電源制御回路17とを備えることを特徴とする。

(もっと読む)

不揮発性半導体メモリ及びそのテスト方法

【課題】不揮発性半導体メモリのテスト時に、電源電圧を変えることなく、電圧生成回路によって生成される駆動電圧を容易に変えること。

【解決手段】トリミングコード出力回路は、複数のトリミングコードのうちいずれか1つを電圧生成回路に出力する。電圧生成回路は、電源電圧及びトリミングコードに依存して変化する駆動電圧を生成する。制御回路は、生成された駆動電圧を不揮発性メモリアレイに印加する。複数のトリミングコードは、適正トリミングコードとテスト用トリミングコードを含む。テスト用トリミングコードは、適正トリミングコードと異なっており、テスト時にのみ用いられる。テスト時、トリミングコード出力回路はテスト用トリミングコードを電圧生成回路に出力し、電圧生成回路はテスト用トリミングコードに従って駆動電圧を生成する。テスト以外の場合、トリミングコード出力回路は適正トリミングコードを電圧生成回路に出力し、電圧生成回路は適正トリミングコードに従って駆動電圧を生成する。

(もっと読む)

1 - 20 / 43

[ Back to top ]