Fターム[5M024AA01]の内容

Fターム[5M024AA01]の下位に属するFターム

低電圧化 (61)

動作電流の低減 (514)

回路(動作)切り替え (32)

部分動作 (135)

バックアップ電流の低減 (33)

その他 (34)

Fターム[5M024AA01]に分類される特許

1 - 10 / 10

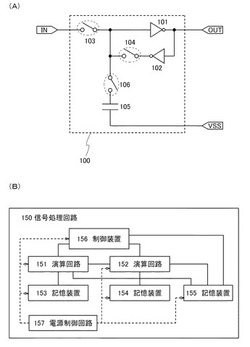

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

多重バス電荷共有

【課題】柔軟な多重化および選択電荷共有機能を有する電荷共有回路。

【解決手段】電荷共有回路は、一の第1の入力バスの対と、一の第2の入力バスの対と、一の出力バスの対とを含む。一のキャパシタC1は、一の第1の内部ノードEQ1と、一の第2の内部ノードEQ2との間に接続される。一の第1の回路は、第1の内部ノードEQ1と、第1の入力バスの対、第2の入力バスの対、および、出力バスの対とを選択的に接続する。第2の回路は、第2の入力ノードEQ2と、第1の入力バスの対、第2の入力バスの対、および、出力バスの対とを選択的に接続する。第3の回路は、第1の入力バスの対を基準電圧に選択的に接続する。第4の回路は、第2の入力バスの対を基準電圧に選択的に接続する。

(もっと読む)

半導体集積回路

【課題】半導体記憶回路から論理回路へのデータ転送速度を向上させる。

【解決手段】出力データ制御回路20がハイレベルからローレベルに切り替えたデータDOBiを出力した場合、CMOSインバータ31の出力はハイレベル、CMOSインバータ32の出力はローレベルになる。しかし、Pチャンネル型MOSトランジスタ40pのソース−ゲート間の電位差があまり大きくないため、Pチャンネル型MOSトランジスタ40pはすぐにオンにならず、最終段CMOSインバータ40の出力がすぐにハイレベルにならない。このときNチャンネル型MOSトランジスタ50のゲートにCMOSインバータ31の出力であるハイレベルの電圧が供給されるので、Nチャンネル型MOSトランジスタ50はオンになる。よって、Nチャンネル型MOSトランジスタ50により最終段CMOSインバータ40の出力が持ち上げられ、ハイレベルになる。

(もっと読む)

異なる選択された信号値の信号生成を実現する集積回路装置のスイッチキャパシタ電荷共有技術

【課題】効率的な電荷共有および正確な目標値の信号レベルの生成を実現する集積回路デバイスのためのスイッチキャパシタ電荷共有技術が開示される。

【解決手段】電荷を共有する回路の信号レベルは、同じ電圧レベルを有する必要はない。本願明細書中に開示される本発明の技術の特定の実施形態では、例えば、2つの異なる信号、または、2つの異なる信号グループの間で電荷を共有するためにスイッチキャパシタが用いられる。キャパシタの大きさは、様々な信号の要求される信号レベルを得るよう調整されることができる。

(もっと読む)

半導体記憶装置

【課題】安定化容量の直列接続された複数のセルキャパシタの接続点の中間電位を適切に制御できるようにすることを目的とする。

【解決手段】電源電圧を昇圧し昇圧電圧VPPをメモリコア12に供給する昇圧電源回路11、昇圧電圧VPPを供給する電源線と接地の間に直列接続された安定化容量14を構成するセルキャパシタC1,C2、及びセルキャパシタC1,C2の接続点に中間電位Vbiasを供給するバイアス発生回路13に加え、さらに昇圧電圧VPPを設定値に下げるクランプ回路15を備え、昇圧電源回路11が昇圧動作を停止する場合に、クランプ回路15により昇圧電圧VPPを設定値にクランプし、その後の通常動作への移行時に中間電位Vbiasが昇圧電圧側や接地電位側に大きく逸脱することを防止できるようにする。

(もっと読む)

半導体記憶装置

【課題】GIDLによるスタンバイ電流を抑制するワード線駆動回路の提供。

【解決手段】ゲートが共通に入力信号MWLBに接続された、第1、第2の電源RAI、VKKにソースがそれぞれ接続され、互いに導電型の異なる第1及び第2のMOSトランジスタ12、18と、第1及び第2のMOSトランジスタのドレインの間に接続され、第1のMOSトランジスタと同一導電型の第3のMOSトランジスタ16を備え、第2及び第3のMOSトランジスタのドレイン同士の接続点がワード線WLに接続され、MWLBはHIGH電位とされ、第2のトランジスタ18がオンのとき、第3のMOSトランジスタ16のゲートにはMWLBのHIGH電位よりも低い電位が供給される。第3のMOSトランジスタ16のゲートには、HIGH電位がMWLBのHIGH電位よりも低い信号SECが供給されるか、又は固定のGND電位が供給される。

(もっと読む)

半導体装置

【課題】微細化が進みセルキャパシタの容量値が小さくなった場合、データ線を低電圧化すると、読み出し信号量が著しく低下して、読み出し時に誤動作が生じ、チップの歩留まりを低下させてしまう。

【解決手段】サブアレイごとにエラー訂正回路を有する。また、読出し動作および書き込み動作のいずれの動作においても、エラー訂正回路による誤動作の検出および訂正動作を行う。さらに、エラー訂正回路に加えて救済回路を有し、ハードエラーによる不良セルを冗長ビットと置換する。

(もっと読む)

メモリ制御装置および制御方法

【課題】 リフレッシュ動作を必要とする揮発性メモリの低消費電力化を実現する。

【解決手段】 揮発性メモリが必要とするリフレッシュ動作を制御するメモリ制御装置において、揮発性メモリへデータを書き込む時のアドレス位置を書き込みポインタとして記憶し、書き込みポインタが先頭に戻る度に値を反転する書き込みフラグを記憶する書き込みアドレス記憶部と、揮発性メモリからデータを読み込む時のアドレス位置を読み込みポインタとして記憶し、読み込みポインタが先頭に戻る度に値を反転する読み込みフラグを記憶する読み込みアドレス記憶部と、書き込みポインタと、書き込みフラグと、読み込みポインタと、読み込みフラグと、から揮発性メモリに書き込まれたすべてのデータが読み込まれたか否かを判定する判定信号を生成するポインタ制御部と、判定信号によりリフレッシュ動作を続けるか否かを制御するリフレッシュ制御部と、を備える。

(もっと読む)

半導体メモリ

複数のフラグは、複数の揮発性のメモリセルにより構成されるメモリセルグループに対応してそれぞれ形成されている。各フラグは、メモリセルが第2記憶モードでデータを記憶していることをセット状態として示す。メモリセル毎にデータを保持する第1記憶モードから各メモリセルグループのメモリセルに同一のデータを保持する第2記憶モードに切り替える切り替え動作において、各フラグは、対応するメモリセルグループの最初のアクセスに応じてリセットされる。このため、各メモリセルグループ毎に、最初のアクセスのみ第2記憶モードでアクセスされる。上記切り替え動作において、フラグに応じたモードでメモリセルをアクセスすることで、半導体メモリを管理するシステムは、切り替え動作の間もメモリセルに自在にアクセスできる。この結果、実質的な切り替え時間をなくすことができる。  (もっと読む)

(もっと読む)

半導体装置、回路、これらを用いた表示装置、及びこれらの駆動方法

【課題】 フローティングボディを有するMOS型トランジスタを用いた回路において生じる履歴効果による動作不良を抑制し、電気的特性に優れた装置を提供する。また、これらMOS型トランジスタを構成要素として含むセンスアンプ回路、ラッチ回路の感度を向上させる。

【解決手段】 第1の期間(有効期間)にMOS型トランジスタの電気的特性を利用して、第1の回路以外の回路で必要とされる信号を出力し、前記第1の期間を除いた第2の期間(休止期間)に、MOS型トランジスタのゲート−ソース間にこのMOS型トランジスタのしきい値以上のステップ波形電圧を与える。

(もっと読む)

1 - 10 / 10

[ Back to top ]