Fターム[5M024AA18]の内容

Fターム[5M024AA18]に分類される特許

1 - 20 / 33

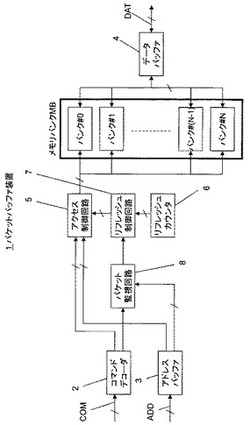

バッファメモリ装置及び通信装置

【課題】 リフレッシュの有無をリアルタイムに判定でき、しかも、優先データを扱うことが可能なパケットバッファ装置を提供する。

【解決手段】 対象としているパケットバッファ装置は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うものである。そして、メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

電子機器

【課題】冷却装置の冷却機能による筐体内の温度変化に拘わらず、適切なリフレッシュレートを設定でき、筐体内の回路基板に実装された電子部品に含まれるSDRAMにおけるデータ損失を適確に防止できる電子機器を提供する。

【解決手段】 この電子機器におけるCPU3は、SDRAM1がセルフリフレッシュのモードへ移行する前にDRAMコントローラ2経由で温度センサ10により測定した温度情報に基づいて、セルフリフレッシュのモード時のリフレッシュレートを決定するためのモードレジスタであるSRTの設定値を決定する温度レンジ決定機能を持ち、DRAMコントローラ2のグラフィック/メモリコントローラ2aを指示してSDRAM1のSRTの設定値を変更する。これにより、SDRAM1は、CPU3の温度レンジ決定機能により決定されたSRTの設定値に応じて設定されたリフレッシュレートに従ってセルフリフレッシュのモードへ移行する。

(もっと読む)

半導体記憶装置、メモリシステム、及び半導体記憶装置のリフレッシュ制御方法

【課題】リードライトアクセスが必要ないときに低消費電力で待機すると共に、リードライトアクセスが必要になったときに遅滞なくアクセスできる半導体記憶装置、メモリシステム及び半導体記憶装置におけるリフレッシュ制御方法を提供する。

【解決手段】クロックに同期して外部から与えられたコマンドに応答し、リードライト動作を行う動作モードと、外部からリードライトコマンドを受け付けないパワーダウンモードと、を有する半導体記憶装置であって、パワーダウンモードにおいて、外部から与えられた信号に応答してリフレッシュを行う。パワーダウンモードにおいてもメモリコントローラからリフレッシュ制御が行えるので、パワーダウン解除後に遅滞なくアクセスできる。

(もっと読む)

録画機器及び揮発性メモリのリフレッシュ方法

【課題】複数の揮発性メモリを備えた録画機器において、揮発性メモリのリフレッシュサイクルをできるだけ長くし、消費電力を低減できるようにする。

【解決手段】録画再生機器は、複数の揮発性メモリを備えたメモリディスク10を有し、メモリディスク10に録画データを記録する。メモリディスク10は、複数の揮発性メモリを構成する所定の単位(メモリチップなど)毎に規定されたリフレッシュサイクルの規定値に対して、規定値よりも長いリフレッシュサイクルの実力値を決定し、リフレッシュサイクルの規定値及び実力値に基づいて、所定の単位毎にリフレッシュサイクルを制御することにより、複数の揮発性メモリのリフレッシュ動作を行う。

(もっと読む)

半導体装置

【課題】セルフリフレッシュモード時における消費電流を高速アクセス動作を損なうことなく低減する。

【解決手段】動作モード指示信号がリフレッシュモードを指定するときにメモリアレイのリフレッシュを行なう領域を指定するリフレッシュ領域指定アドレスをアドレスレジスタ(87)に格納する。リフレッシュアドレス発生回路(20b、86,88)は、動作モード指示信号がリフレッシュモードを指定するとき、リフレッシュ領域指定アドレスが指定する領域内のメモリセルのリフレッシュを行なうようにリフレッシュアドレスを発生する。リフレッシュ系回路は、リフレッシュタイマ(85)から所定の周期で発行されるリフレッシュ要求に従って、リフレッシュアドレス発生回路からのリフレッシュアドレスに従って選択されたメモリセルのリフレッシュを行なう。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】リフレッシュビジーレイトが低く、データ保持時の消費電力が少なく、微細化に優れた半導体記憶装置およびその駆動方法を提供する。

【解決手段】半導体記憶装置は、ボディの第1の面に設けられた第1のゲートと、ボディの第2の面に設けられた第2のゲートと、ソース線ドライバと、センスアンプとを備え、データ保持状態において、ボディに電荷が流れ込むように、第1のゲート電位は、ソースおよびドレインのうち一方の電位よりも高くかつソースおよびドレインのうち他方の電位よりも低くなるように設定され、さらに、ボディから電荷が流れ出るように、第2のゲート電位は、ソース電位、ドレイン電位および第1のゲート電位のいずれよりも絶対値として大きくなるように設定され、データ保持状態において、単位時間にボディに流れ込む第1の電荷量と単位時間にボディ領域から流れ出る第2の電荷量とがほぼ等しくなる平衡状態にメモリセルを維持する。

(もっと読む)

半導体記憶装置

【課題】リフレッシュビジーレイトが小さく、データ保持時の消費電流が低く、さらに、小型化に優れた半導体記憶装置を提供する。

【解決手段】このメモリは、フローティングボディを含む複数のメモリセル、ドレイン層に接続された複数のビット線、ゲート電極に接続された複数のワード線および、メモリセルから論理データを読み出し、あるいは、書き込むセンスアンプを備え、メモリセルの論理データの劣化を回復させるリフレッシュ動作を実行する際に、ボディ内の蓄積電荷の多い状態を示す第1の論理データを記憶するメモリセルに所定電流よりも多い第1の電流を流し、ボディ内の蓄積電荷の少ない状態を示す第2の論理データを記憶するメモリセルに所定電流よりも少ない第2の電流を流すバイポーラ作用を生じさせるように単数または複数のビット線および複数のワード線を同時に駆動することによって、複数のメモリセルを同時にリフレッシュする。

(もっと読む)

半導体記憶装置

【課題】リフレッシュビジーレイトが小さく、データ保持時の消費電流が低く、さらに、小型化に優れた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ソース層と、ドレイン層と、ボディと、ボディの第1面と第2面に面する第1および第2のゲート電極と、ゲート電極を駆動するドライバと、センスアンプとを備え、リフレッシュ動作のうち第1のリフレッシュでは、第1のゲート電位は読出し/書込み時の第1のゲート電位と同極性の電位であり、第2のゲート電位は読出し/書込み時の第1のゲート電位と逆極性の電位であり、第2のリフレッシュ動作では、第1のゲート電位は読出し/書込み時の第1のゲート電位と逆極性の電位であり、第2のゲート電位は読出し/書込み時の第1のゲート電位に対して逆極性の電位であり、第1のリフレッシュ動作における第2のゲート電位は、第2のリフレッシュ動作における第2のゲート電位よりもソース層の電位に近い。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】リフレッシュビジーレイトが小さく、データ保持時の消費電流が低く、さらに、小型化に優れた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体層内に設けられたソース層、ドレイン層、ボディ領域と、ボディ領域の第1の面上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜を介して第1の面に設けられた第1のゲート電極と、ボディ領域の第2の面に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して第2の面に設けられた第2のゲート電極とを備え、リフレッシュ動作時に、ソース層の電位を基準として互いに逆極性の電圧を第1および第2のゲート電極に印加することによって、ドレイン/ソースからボディ領域へ第1の電流を流し、かつ、ボディ領域から第2のゲート電極へ第2の電流を流し、リフレッシュ動作の1周期内における第1の電流に基づく電荷の量と第2の電流に基づく電荷の量とがほぼ等しくなる平衡状態へメモリセルを遷移させる。

(もっと読む)

半導体メモリ

【課題】 リフレッシュ動作が必要なメモリセルを有する半導体メモリにおいて、低消費電力モード中の消費電力を削減する。

【解決手段】 半導体メモリは、ビット線に接続されているメモリセルのうち、1つの第1メモリセルと少なくとも1つの第2メモリセルを含む複数のパーシャル領域を有している。動作制御回路は、低消費電力モード中に、リフレッシュ制御信号に応答して、第1および第2メモリセルを同時にリフレッシュする。リフレッシュ制御回路は、低消費電力モードから通常動作モードに移行するときに、リフレッシュ制御信号を通常動作モード時と同じ間隔で出力するとともに、前回のリフレッシュ動作から所定時間が経過したメモリセルのみにリフレッシュ動作を実行する。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】データ保持期間におけるリフレッシュ動作の消費電力を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、フローティングボディ内の多数キャリアの数によって論理データを記憶するメモリセルMCと、複数のメモリセルに接続された複数のビット線BLと、複数のメモリセルに接続された複数のワード線WLと、メモリセルのデータを読み出し、メモリセルへデータを書き込むセンスアンプS/Aと、メモリセルからデータを一旦読出しかつ該データと同一論理データを該メモリセルへ書き戻すリフレッシュ動作を指示するリフレッシュコントローラREFCと、データ読出しモードまたはデータ書込みモードにおいては、或るリフレッシュ動作と次のリフレッシュ動作との間のリフレッシュ間隔を第1の間隔とし、データ保持モードにおいては、リフレッシュ間隔を第1の間隔よりも長い第2の間隔とするリフレッシュ間隔タイマTmr1、Tmr2とを備えている。

(もっと読む)

ダイナミックランダムアクセスメモリアレイの電力を低減するための方法および集積回路装置

【課題】DRAMベースのメモリ装置および埋込DRAMが組込まれたものにおいてリフレッシュ動作を行なうための従来のアプローチの欠陥を克服する。

【解決手段】クロック(CLK)サイクルをカウントすることにより、クロック信号はDRAMに与えられるPVTについて安定した周波数を示すのでリフレッシュ時間(tREF)はPVTに従って変動せず、チップに配置される内部タイマがこれらのパラメータに直接に従って変動する。主要な内部クロック(ICLK)信号は、スリープモード(ZZモード)に入った後、装置のチップまたは埋込メモリの周辺を伝搬しないよう抑制される。このときさらに、関連する回路の多くは、典型的にはパワーゲーティングトランジスタに負のゲート−ソース電圧(VGS)を与える昇圧されたレベルを有する信号によって、電力を保存するためパワーゲーティングされることができる。

(もっと読む)

半導体記憶装置

【課題】低消費電力スタンバイモードにおいて、安定にメモリセルの記憶データを保持する。

【解決手段】高圧電源制御回路(15)は、電源供給が遮断されるスタンバイサイクル時、負電圧(VBB)を伝達するグローバル負電圧線(69)とサブアレイブロックに対応して設けられるローカル負電圧線(71)とを分離し、また、接地電圧(VSS)を伝達するグローバル接地線(72)とローカル接地線(77)を分離する。これらのローカル接地線およびローカル負電圧線は、対応の電源からの遮断前に、高電圧線(67)を介して高電圧(VPP)レベルに充電される。ワード線(WL<0>−WL<m>)から負電圧線または接地線へのリーク電流経路は遮断され、非選択状態のワード線を確実に非選択電圧(VPPレベル)に維持することができる。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ時の消費電流を削減でき、パーシャルリフレッシュ時のポーズ時間を短縮してデータの信頼性を確保することが可能な半導体記憶装置を提供する。

【解決手段】保持回路は、メモリセルアレイの全体的なセルフレッシュを行うフルセルフリフレッシュ(FSR)と、メモリセルアレイの部分的なリフレッシュを行うパーシャルアレイセルフリフレッシュ(PASR)とを切替える制御信号を保持する。リフレッシュアドレスカウンタは、リフレッシュアドレスを発生する。アドレス切替回路は、保持回路から供給される制御信号に応じて外部から供給される外部アドレスの上位ビットを単位セルブロック内のワード線の選択アドレスとし、FSR及びPASRのどちらにおいても、リフレッシュアドレスカウンタにより発生されたリフレッシュアドレスの下位ビットを前記単位セルブロック内のワード線の選択アドレスとする。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの動作方法

【課題】 リフレッシュ動作を確実に実行し、半導体メモリの誤動作を防止する。

【解決手段】 リフレッシュ動作の許可/禁止を示すパーシャルリフレッシュ情報が、外部入力に応じて設定され、パーシャル設定信号として出力される。リフレッシュ要求信号は、リフレッシュ動作が許可されているメモリブロックに対応して周期的に出力される。パーシャルリフレッシュ情報が外部入力により変更されている間に、全てのメモリブロックのリフレッシュ動作を許可するために、パーシャル設定信号はマスクされる。これにより、パーシャルリフレッシュ情報の変更タイミングと、リフレッシュ要求信号の発生タイミングが重なった場合にも、リフレッシュ要求に応答するリフレッシュ動作が禁止されることを防止できる。この結果、リフレッシュ動作を確実に実行でき、半導体メモリの誤動作を防止できる。

(もっと読む)

電子装置、画像処理装置及び電源供給制御方法

【課題】終端電源の電圧が規定の電圧に達しない状態でDRAMアクセスをして、不正なデータの読み出しや、保持データの破壊等の不具合を生じさせることがないようにする。

【解決手段】DRAM212と該DRAMを制御するためのDRAMコントローラ115とを有する。DRAMコントローラ115とDRAM212とはデータ伝送通信線211により接続される。終端電圧供給手段209はDRAMコントローラ115からの制御信号を受けて、データ伝送通信線211に電源の供給を行う。DRAMコントローラ115は、DRAM212のリフレッシュモードを解除するときに、終端電圧供給手段209に電源の供給を開始させ、終端電圧供給手段209が電源供給を開始してから、DRAM212がリフレッシュ解除状態となるまで、DRAM212に対するアクセスを待たせる。

(もっと読む)

半導体記憶装置及びそのリフレッシュ制御方法

【課題】待機時の電源電流を低減して低消費電力化を図るともにチップ面積の増大を抑止するダイナミック型の半導体記憶装置の提供。

【解決手段】ノーマル動作時にアクセスされたロウアドレスに対応するワード線をRAM101に記憶しておき、セルフリフレッシュへのエントリ時、ノーマル動作期間中にアクセスされたロウアドレスに対応するワード線に接続するメモリセルのデータを読み出しデータに対する検査ビットを符号器115で付加して検査ビット領域に書き込み、電源投入後の最初のセルフリフレッシュエントリの初期化処理として、ワード線単位でメモリセルのデータ保持時間の検査を行い、該検査結果に基づきワード線のリフレッシュ周期の設定値を決定し該設定値をRAM101に書き込むことでワード線毎のリフレッシュ周期の設定が行われ、リフレッシュ動作による誤り検出時、誤り訂正回路で誤りを訂正する。

(もっと読む)

半導体記憶装置

【課題】スタンバイ時の消費電流を低減することが出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置が、複数のメモリバンクと、メモリバンク毎に設けられ、メモリバンク内のセンスアンプをアレイ電圧より高い電圧であるオーバードライブ電圧で駆動する電源を供給するアクティブ用オーバードライブ電圧発生回路と、メモリバンクに共通に設けられ、メモリバンク内のセンスアンプのスタンバイ時における電圧を予め設定された電圧に一定に保つ電源であるスタンバイ用オーバードライブ電圧発生回路と、メモリバンクとスタンバイ用オーバードライブ電圧発生回路とを接続するメモリバンク毎の電源接続回路と、を有し、メモリバンク毎のアクティブ用オーバードライブ電圧発生回路の出力が、メモリバンクとメモリバンク毎の電源接続回路との接続点に接続される。

(もっと読む)

1 - 20 / 33

[ Back to top ]