Fターム[5M024BB22]の内容

DRAM (26,723) | 改良の場所/タイミング (5,148) | 場所 (3,103) | リフレッシュ回路 (333)

Fターム[5M024BB22]に分類される特許

1 - 20 / 333

半導体装置

【課題】不要にリフレッシュ周期が変更されることによる無駄な消費電流を削減する。

【解決手段】複数の半導体チップを備え、複数の半導体チップのうちの第1の半導体チップは第1の温度センサを有し、第1の半導体チップとは異なる第2の半導体チップはリフレッシュ動作を必要とする半導体チップであって、第1の半導体チップの第1の温度センサの出力結果に応じて第2の半導体チップのリフレッシュ周期が変更される。

(もっと読む)

セルフリフレッシュパルス生成回路

【課題】セルフリフレッシュモード入り後初期期間に周期が制御されたセルフリフレッシュパルスを生成することにより、リフレッシュフェイルを防止することが可能なセルフリフレッシュパルス生成回路を提供する。

【解決手段】セルフリフレッシュパルス生成回路は、セルフリフレッシュモード入り後初期期間の終了時点でレベルが遷移する制御信号を生成する制御信号生成部と、前記セルフリフレッシュモードにおいて、前記制御信号に応答して、周期が制御されたセルフリフレッシュパルスを生成するセルフリフレッシュパルス生成部とを備える。

(もっと読む)

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

バッファメモリ装置及び通信装置

【課題】 リフレッシュの有無をリアルタイムに判定でき、しかも、優先データを扱うことが可能なパケットバッファ装置を提供する。

【解決手段】 対象としているパケットバッファ装置は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うものである。そして、メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

温度情報出力装置の温度情報出力方法

【課題】温度情報出力装置の面積を増やさなくとも動作可能な温度範囲を増やすことができる、温度情報出力装置の温度情報出力方法を提供する。

【解決手段】温度を感知し、当該温度に対応する第1の電圧VTEMPを出力するステップと、第1の電圧VTEMPと第2の電圧DACOUTとを比較するステップと、この比較結果に基づいて、デジタルコードDIGITAL_CODEを加減するステップと、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTを生成するステップとを含み、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTの変化幅が温度区間別に異なる。

(もっと読む)

半導体メモリ素子の駆動方法

【課題】セルフリフレッシュ(SR)モードにおける不要な電流消費を最小化できる半導体メモリ素子の駆動方法を提供する。

【解決方法】1)各行のリフレッシュタイム特性に対応する第1格納値を初期化し、2)第1格納値が設定された行のうちの第1行目に対して、各列のデータを第2格納値として格納し、3)リフレッシュ周期の設定のための検出動作を行い、その結果に応じて第1格納値を設定し、4)第2格納値を第1行に再格納し、5)残りの全ての行に対して第1格納値の設定が完了するまで、又は、SRモードが終了するまで2)〜4)を繰り返し、6)SRモードを脱出した後、ノーマルアクティブモードで書き込み動作を行う行に対応する第1格納値を「0」に設定し、7) 2)〜6)をSRモードの度に繰り返す工程を含み、第1格納値によって選択されたリフレッシュ周期によって残りの行に対するリフレッシュ動作の実行又は省略の可否を決定する。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、セルフリフレッシュモードにエントリすると、オシレータ150を用いてリフレッシュ動作を周期的に実行する。セルフリフレッシュモードにおいて1回のリフレッシュ動作に要する時間をオートリフレッシュの1/4に短縮するとともに、リフレッシュ動作の実行頻度を4倍とする。これにより、セルフリフレッシュイグジットコマンドSRXを発行した後、ロウ系のコマンドの投入が禁止される期間を短縮することが可能となる。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードにエントリしている期間中においてもデータ端子のインピーダンス制御を可能とする。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、インピーダンス制御信号ODTを受信する入力バッファ回路72をセルフリフレッシュモード中においても常時活性化させるとともに、セルフリフレッシュモード中においては、内部クロック信号ICLK0に同期してインピーダンス制御信号IODT0をラッチするラッチ回路84をバイパスさせる。これにより、外部クロック信号CKを使用することなく、セルフリフレッシュモード中におけるインピーダンス制御信号ODTの入力が可能となる。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREとセルフリフレッシュイグジットコマンドSRXを交互に周期的に発行する。半導体装置10は、セルフリフレッシュコマンドSREに同期してリフレッシュ動作を例えば1回だけ実行し、セルフリフレッシュイグジットコマンドSRXに応答してDLL回路200の状態更新を実行する。これにより、セルフリフレッシュイグジットコマンドSRXを発行した後、ロウ系のコマンドや位相制御された内部クロック信号ICLK1を必要とするコマンドを短時間で発行することが可能となる。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10がセルフリフレッシュモードにエントリしているか否かにかかわらず外部クロック信号CKを連続的に発行する。半導体装置10は、セルフリフレッシュモードにエントリしている期間に外部クロック信号CKの入力バッファ回路71とDLL回路200を間欠的に活性化させる。これにより、セルフリフレッシュモード中においてもDLL回路200の状態が間欠的に更新され、正しく位相制御された内部クロック信号ICLK1が得られる状態に保たれる。したがって、セルフリフレッシュモード中における入力バッファ回路71の消費電力を削減しつつ、セルフリフレッシュモードからイグジットした後、位相制御された内部クロック信号ICLK1を必要とするコマンドを短期間で投入することが可能となる。

(もっと読む)

半導体記憶装置及びそのリフレッシュ制御方法

【課題】アクセス頻度が高いプレートのリフレッシュ動作頻度を上げる技術を提供する。

【解決手段】半導体装置において、プレートへのアクセス頻度を検出し、アクセス頻度が所定の閾値を超えたときに活性信号を出力するディスターブカウンタ回路と、オートリフレッシュコマンド時に活性信号を検出すると、アクセス頻度が所定の閾値以上のプレートについてのリフレッシュ割り込み信号を出力するリフレッシュカウンタ回路とを提供する。

(もっと読む)

エラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法

【課題】エラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法を提供する。

【解決手段】半導体メモリ装置のチップ内部でデータ・スクラビングを行うエラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法であって、該メモリ装置のリフレッシュ方法は、メモリ装置の対応する部分について、スクラビングのない少なくとも1つのリフレッシュを行う段階と、メモリ装置の対応する部分について、スクラビングを有する少なくとも1つのリフレッシュを行う段階と、を含む。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体記憶装置およびその駆動方法

【課題】小面積かつ低消費電力であるリフレッシュタイミング検出回路を有する半導体記憶装置を提供する。

【解決手段】酸化物半導体を用いた第1のトランジスタ、および第1のキャパシタからなるメモリセルをマトリクス状に有するメモリセルアレイと、pチャネル型である第3のトランジスタ、第2のキャパシタおよび酸化物半導体を用いた第2のトランジスタを有する参照セル、ならびに抵抗素子およびコンパレータを有するリフレッシュタイミング検出回路と、を有するメモリモジュールにおいて、第1のトランジスタを介して第1のキャパシタに電位が与えられると第2のトランジスタを介して第2のキャパシタに電位が与えられ、第2のキャパシタの電位に応じて第3のトランジスタのドレイン電流値が変化し、第3のトランジスタのドレイン電流値が任意の値より大きくなると、メモリセルアレイおよび参照セルのリフレッシュ動作を行う。

(もっと読む)

半導体装置

【課題】セルフリフレッシュのピーク電流値を低減し、セルリフレッシュからのExit時間を短縮する半導体装置を提供する。

【解決手段】リフレッシュ活性化信号(REFACT0〜REFACT3)が入力されると、内部のメモリセルをリフレッシュする少なくとも2以上のメモリバンク(bank0〜bank3)と、オートリフレッシュコマンドが入力されると、メモリバンクのうち全てのメモリバンクのリフレッシュ動作を活性化するリフレッシュ活性化信号をメモリバンク各々に対して出力して第1のリフレッシュ制御動作を行い、セルフリフレッシュコマンドが入力されると、メモリバンクのうち一部のメモリバンクのリフレッシュ動作を活性化するリフレッシュ活性化信号を当該一部のメモリバンクに対して出力して第2のリフレッシュ制御動作を行うリフレッシュ制御回路(22)と、を備える。

(もっと読む)

メモリ装置のリフレッシュ方法、リフレッシュアドレス生成器及びメモリ装置

【課題】メモリ装置のリフレッシュ方法、リフレッシュアドレス生成器及びメモリ装置を提供する。

【解決手段】リフレッシュレバレッジングを利用してメモリ装置をリフレッシュするように、リフレッシュアドレスがリフレッシュ周期で生成される。リフレッシュアドレスが第2アドレスの時、第2アドレスを有する第1ストロングセルの代わりに第1アドレスを有するウィークセルに対するリフレッシュが実行される。リフレッシュアドレスが第3アドレスの時、第1ストロングセルまたは、第3アドレスを有する第2ストロングセルのうち、いずれか1つに対するリフレッシュが実行される。メモリ容量が減少するように、第1、第2及び第3アドレスうち、ただ1つに対するアドレス情報が保存される。他の実施形態において、リフレッシュレバレッジングを実行するように、リフレッシュアドレスが少なくとも1つの所定のアドレスの時、フラグによってウィークセル、第1ストロングセルまたは、第2ストロングセルのうち、いずれか1つに対するリフレッシュが実行される。

(もっと読む)

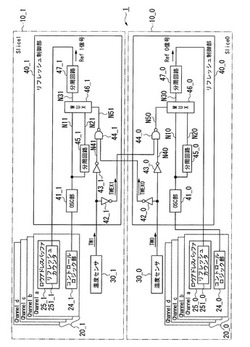

半導体装置及びシステム

【課題】互いに独立に動作する複数の記憶領域に対するリフレッシュ動作の起動タイミングが重ならないように制御可能な半導体装置及びシステムを提供する。

【解決手段】本発明は、互いに独立に動作する複数の記憶領域と、これらの記憶領域の動作をそれぞれ独立に制御する複数の制御回路と、リフレッシュ起動制御回路40とを備えている。リフレッシュ起動制御回路40は、オシレータ信号N0を出力するオシレータ41と、オシレータ信号N0に基づいて活性化タイミングが互いに異なる複数のリフレッシュ起動信号RSを生成するリフレッシュ起動信号生成回路42(2分周回路50〜52及びデコーダ53)とを備え、リフレッシュ要求を受けた制御回路に対応する記憶領域が、対応するリフレッシュ起動信号RSの各活性化タイミングに応答してリフレッシュされる。

(もっと読む)

半導体記憶装置および半導体記憶装置のリフレッシュ方法

【課題】システム全体の処理の効率を向上させることができる半導体記憶装置を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、メモリセルアレイ13と、メモリコントローラ11と、リフレッシュ制御回路12と、を備える。メモリコントローラ11は、メモリセルアレイ13の使用領域の最上位ロウアドレス44に応じた回数のリフレッシュを実施するタイミングが所定のリフレッシュ期間内において分散するように、リフレッシュを実施するタイミングに応じたリフレッシュ要求信号を生成する。リフレッシュ制御回路12は、メモリコントローラ11で生成されたリフレッシュ要求信号33が供給されるタイミング毎に、メモリセルアレイ13のリフレッシュを実施するためのリフレッシュアドレス34が最上位ロウアドレス44と一致するまで当該リフレッシュアドレス34を生成する。

(もっと読む)

コンピュータシステム及び揮発性メモリ装置

【課題】DRAMなどの揮発性メモリ装置に係わり、リフレッシュ時に必要な消費電力の低減を実現できる技術を提供する。

【解決手段】本コンピュータシステム1は、DRAM2とCPU4を含んで成り、例えばCPU4側にデータ反転制御回路100を備える。データ反転制御回路100は、DRAM2への書き込み時(a)のデータにおける所定幅の書込データ単位ごとに、値“1”の数が過半数かどうかを判定し、過半数である場合は、値“1”/“0”を反転処理する。またデータ反転制御回路100は、DRAM2からの読み出し時(b)のデータにおける所定幅の読出データ単位ごとに、上記反転状態の値“1”/“0”を反転処理して復元し、読み出しデータとする。上記構成により、DRAM2におけるリフレッシュ動作の対象となる値“1”が記憶されるメモリセルの数を少なくする。

(もっと読む)

1 - 20 / 333

[ Back to top ]