Fターム[5M024CC10]の内容

Fターム[5M024CC10]に分類される特許

1 - 20 / 20

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】多値書き込みを行う半導体装置、及び半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体である酸化物半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ状態での抵抗が極めて高いトランジスタをスイッチング素子としてメモリセルを構成すれば、例えば、10年以上もの長期にわたりデータを保持できる。その一方で、例えば、トランジスタの特性等により1年しかデータを保持できないメモリセルも同時に作製される。そのようなメモリセルは早期に不良メモリセルとして排除する手段が必要とされるが、従来の検査では判別する手段がなかった。

【解決手段】メモリセルのトランジスタのゲートの電位を通常の保持に使用する電位VGLとそのトランジスタのしきい値Vthの間の所定の電位VGMに保持する。この状態で所定の時間保持すれば、電位VGLで10年保持したものと同様の状態となるので、この時点でデータの保持が不十分なメモリセルは、通常の使用でもデータを10年間保持できないと判断できる。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

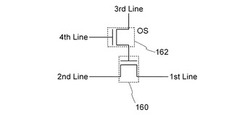

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

記憶装置、半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのスイッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極と、を有する。

(もっと読む)

1−トランジスタ型DRAM駆動方法

【課題】 マルチビットに対応した書込み動作のマージンを改善した1−トランジスタ型DRAMの駆動方法を提供する。

【解決手段】 NMOSトランジスタのワードラインは不活性化し、ソースラインとビットラインはプリチャージさせてデータを保持する第1ホールド区間、ワードラインが活性化され、ソースラインはグラウンド電圧に転移され、ビットラインの電圧はマルチレベルのうち該ビットのレベルの電圧に転移されてNMOSトランジスタ成分とバイポーラトランジスタ成分を共に動作させる複合動作区間、ワードラインの電圧が負の電圧に転移されてバイポーラトランジスタ成分のみを動作させるバイポーラトランジスタ動作区間、およびバイポーラトランジスタ動作区間の後、ソースラインとビットラインがプリチャージされてデータを保持する第2ホールド区間とを含むことによって、ビットラインに印加されたレベルに該当するビットのデータの書込みを行う。

(もっと読む)

2つのゲート用トランジスタを有する多値メモリ記憶装置

本発明は、記憶素子(105)に結合された第1及び第2のノードをそれぞれ有し、互いに並列に配置された第1のゲート用トランジスタ(101)及び第2のゲート用トランジスタ(103)を具える多値メモリセル(111)と、前記第1のゲート用トランジスタ及び第2のゲート用トランジスタのそれぞれの第3のノード及び第4のノードに結合され、前記多値メモリセル(111)の記憶電圧を検出する検出回路(113、115)とを具えるデジタルメモリ装置及びシステム、並びにデジタルメモリ装置の動作方法を提供する。実施例では、第1及び第2のゲート用トランジスタ(101、103)を互いに異なるしきい値電圧レベルで駆動されるように構成する。  (もっと読む)

(もっと読む)

マルチレベル動的メモリ装置

【課題】マルチレベル動的メモリ装置を提供すること。

【解決手段】マルチレベル動的メモリ装置は、メインビットライン対とサブビットライン対とに分割されたビットライン対と、メインビットライン対間に接続された第1センスアンプと、サブビットライン対との間に接続された第2センスアンプと、メインビットライン対とサブビットライン対との間にそれぞれ交差結合された第1及び第2カップリングキャパシタと、第1及び第2カップリングキャパシタとにそれぞれ並列接続され、制御電圧信号によりキャパシタンスが調節される第1及び第2補正キャパシタと、を備える。

(もっと読む)

開放形ビットライン構造を有するマルチレベル動的メモリ装置及びその駆動方法

【課題】開放形ビットライン構造を有するマルチレベル動的メモリ装置を提供する。

【解決手段】マルチレベル動的メモリ装置は、複数のワードライン、開放形の複数のビットライン、複数のメモリセルであって、前記複数のメモリセルの各メモリセルが、各ワードラインと各ビットラインと接続され、少なくとも2ビット以上のデータを保存する複数のメモリセル、及び複数のセンスアンプ部であって、前記複数のセンスアンプ部の各センスアンプ部が、両側に位置した前記ビットライン間の電圧差を増幅する複数のセンスアンプ部を備える。

(もっと読む)

3値メモリ回路

【課題】1Vの電源下で、H,M,Lレベルの3値の信号をメモリセルに記憶させても適正に読み出しを行うことができるセンスアンプ回路を提供する。

【解決手段】メモリセルに接続されたビット線の電位を増幅する増幅部と、ビット線がリセット電位にされた時に増幅部で増幅された電位を第一のサンプリングパルスにより第一のキャパシタに蓄積する第一のサンプリング保持部と、メモリセルによりビット線が読出し電位にされた時に増幅部で増幅された電位を第二のサンプリングパルスにより第二のキャパシタに蓄積する第二のサンプリング保持部と、第一及び第二のキャパシタに保持されている電位差を検出してラッチするラッチ回路とを有するセンスアンプ回路をHレベル検出用とLレベル検出用に備えた3値メモリ回路。

(もっと読む)

集積されたDRAM−NVRAM多値メモリ

【課題】集積されたDRAM−NVRAMメモリセルを提供する。

【解決手段】集積されたDRAM−NVRAM(170、171)すなわち多値メモリセルは、共有される縦型ゲート(120)と浮遊プレート(115、116)を有するデバイスを含む縦型DRAMデバイスで構成される。浮遊プレート(115、116)デバイスは、2つの機能の間の柱状部にある共有された浮遊ボディによって、セルのDRAM部(104、130、101、105、131)の電荷記憶特性を高める。このメモリセルは、柱状部を構成するトレンチを有する基板(100)に形成される。セルのDRAM部(104、130、101、105、131、103)を制御するために、柱状部の一方の側面の縦型ワード線/ゲート(131、130)が用いられる。柱状部の他方の側面の縦型捕獲層(115、116)は、浮遊プレートデバイスの一部として、1以上の電荷を記憶し、またDRAMと浮遊プレートデバイスとの間の浮遊ボディを通じてDRAM機能の特性を高める。縦型NVRAMワード線/制御ゲート(120)は、捕獲層に沿って形成され、近傍の浮遊プレートデバイス(115、116)に共有される。

(もっと読む)

1 - 20 / 20

[ Back to top ]