Fターム[5M024CC39]の内容

Fターム[5M024CC39]に分類される特許

1 - 20 / 48

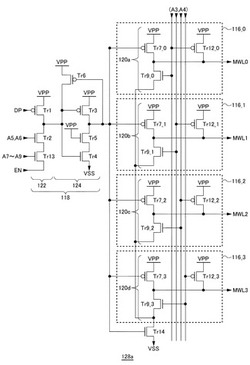

半導体装置

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

ワード線分割回路、及び記憶装置

【課題】回路構成が簡略化され、安定して動作可能なワード線分割回路を提供する。また、回路構成が簡略化され、安定して動作可能な記憶装置を提供する。

【解決手段】ワード線と、サブワード線との間に、リーク電流が極めて低減されたトランジスタを直列に接続し、ワード線分割回路を構成すればよい。当該トランジスタには、チャネルが形成される半導体層に酸化物半導体を含むトランジスタを適用できる。また、このような回路構成が簡略化されたワード線分割回路を、記憶装置に適用すればよい。

(もっと読む)

半導体装置

【課題】ワード線の活性化電位への立ち上がりの遅れを回避しチップサイズの縮小化、動作速度の高速化に対応可能とする。

【解決手段】メモリセル容量(C)と、前記メモリセル容量及びビット線(BLT)との間に設けられたメモリセルトランジスタ(NM)と、前記メモリセルトランジスタの制御電極に接続されるワード線(SWL)と、前記ワード線を駆動するワードドライバ(SWD)と、を備えた半導体装置であって、前記ワードドライバは、前記ワード線を活性化させる第1の期間、及びそれに続く第2の期間において、それぞれ第1の電源電圧、及び、第2の電源電圧により前記ワード線を駆動し、前記第1の電源電圧は前記第2の電源電圧よりも高い電位である。

(もっと読む)

半導体装置

【課題】回路規模が小さい階層型DRAMを提供すること。

【解決手段】それぞれが複数のメモリセルと、前記メモリセルに接続されたビット線と、前記ビット線をプリチャージするプリチャージ回路とを有し、行方向及び列方向にマトリクス状に配置された複数のサブアレイと、前記列方向に沿って延設され、前記サブアレイの列を選択するための列選択信号線と、前記行方向に沿って延設され、前記サブアレイの行を選択するためのメインワード線と、前記プリチャージ回路に対してプリチャージ信号を供給するプリチャージ信号線と、を備え、前記行方向または前記列方向に並べて配置された少なくとも2つの前記サブアレイが前記プリチャージ信号に応じて同一論理で制御される半導体装置。

(もっと読む)

半導体装置

【課題】 隣接する他のワード線と短絡したワード線に接続されているメモリセルについて個々の評価試験を可能にする。

【解決手段】 半導体装置は、入力されるテストモード信号が活性化されたときに、一つのメインワード線に繋がる複数のサブワード線をそれぞれ駆動する複数のプリデコード信号を同時に活性化するプリデコード回路を含んでいる。

(もっと読む)

半導体記憶装置

【課題】ワード選択スピードを向上することができ、また動作電流の低減を図ることが可能な半導体記憶装置を提供することである。

【解決手段】本発明かかる半導体記憶装置は、メインワードデコーダ1と、サブワードドライバ2_1〜2_4と、両端にサブワードドライバ2_1、2_2がそれぞれ設けられると共に、複数のサブワード線を含む第1のメモリセルアレイ3_1と、メインワードデコーダ1から最も離れた位置に配置され、サブワードドライバ2_3、2_4がメインワードデコーダ1に近い側のみに配置された第2のメモリセルアレイ3_2と、を備える。メインワード線4およびプリデコード線5は、メインワードデコーダ1から第2のメモリセルアレイ3_2のサブワードドライバ2_4まで延びるように配置されている。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

半導体記憶装置

【課題】複数のメインワード線を備える半導体記憶装置において、複数のメインワード線を同時に活性化したいという要望が存在する。しかし、1本のメインワード線を駆動可能な能力を持つドライバでは、複数のメインワード線を同時に活性化することができない。そのため、複数のメインワード線を同時に活性化する半導体記憶装置が望まれる。

【解決手段】図1に示す半導体記憶装置は、第1及び第2のメインワード線と、外部から入力されるテストコマンドに応じて、第1のメインワード線を第1のタイミングで活性化させ、かつ、第1のメインワード線の活性状態を維持させたまま第1のタイミングとは異なる第2のタイミングで第2のメインワード線を活性化させる制御回路と、を備える。

(もっと読む)

半導体装置

【課題】センスアンプのイコライズ速度を高めつつ、イコライズ動作とワード線のリセット動作との同期を取る。

【解決手段】ビット線対BLT,BLBをイコライズするイコライズ回路を含むセンスアンプSAと、イコライズ信号EQBの振幅をVDDレベルに変換するイコライズ制御回路64と、タイミング信号に基づいてサブワード線SWLを制御するワードドライバWDとを備える。ワードドライバWDは、VDDレベルに応じてサブワード線SWLの動作タイミングを変化させるためのレベルシフト回路LV1を含んでおり、これによりVDDレベルが変化した場合であっても、イコライズ動作の完了タイミングとサブワード線のリセットタイミングが連動する。

(もっと読む)

半導体メモリ装置及び半導体メモリ・システム

【課題】ビットライン間のカップリング、またはワードライン間のカップリングを低減させることができる半導体メモリ装置を提供する。

【解決手段】第1ビットラインBL12に連結される第1メモリセルを含む第1領域SMCB1、及び第2ビットラインBL22に連結される第2メモリセルを含む第2領域SMCB2を具備する複数のメモリセル・ブロック110_1〜110_8と、対応するメモリセル・ブロックの前記第1メモリセル、または前記第2メモリセルと連結される複数のビットライン・センスアンプ120_1〜120_6と、第1ビットラインを、対応するビットライン・センスアンプに連結したり、グローバル・ビットラインGBL1〜GBL8を介して、前記第2ビットラインを、前記対応するビットライン・センスアンプに連結する複数の連結部130_1〜130_8と、を具備する。

(もっと読む)

バックバイアス電圧のリップル・ノイズを減らす半導体メモリ装置及びその駆動方法

【課題】バックバイアス電圧のリップル・ノイズを減らす半導体メモリ装置及びその駆動方法を提供する。

【解決手段】ワードライン駆動回路と遅延ロジック回路とを含み、該ワードライン駆動回路は、サブ・ワードライン・イネーブル信号、第1ワードライン駆動信号及び第2ワードライン駆動信号に応答し、選択されたメモリセルに連結されるサブ・ワードラインを第1電圧にイネーブルさせ、非選択のメモリセルのサブ・ワードラインを第2電圧及び第3電圧にディセーブルさせ、該遅延ロジック回路は、サブ・ワードラインのディセーブル時、第1ワードライン駆動信号の遷移時点を基準にして、サブ・ワードライン・イネーブル信号の遷移時点を可変させ、第3電圧に流入されるサブ・ワードラインのチャージ量より、第2電圧に流入されるサブ・ワードラインのチャージ量が多いように制御する半導体メモリ装置である。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】ネガティブワードライン方式の適用時において、隣接ゲート効果が深刻になる現象を防止し、かつ、無駄な電流消費の増加を防止することのできる半導体メモリ装置及びその駆動方法を提供すること。

【解決手段】本発明の半導体メモリ装置は、アクティブコマンドが印加されて選択されたいずれか1本のワードラインが活性化されることにより、活性化されたワードラインが高電位電圧で駆動される期間において、活性化されたワードラインに隣接する少なくとも1本の非活性化ワードラインと残りの非活性化ワードラインとに対するワードライン駆動電圧を互いに異なる大きさで印加する。

(もっと読む)

半導体記憶装置

【課題】不良救済効率を改善する。

【解決手段】サブワード線レベルの不良のときとメインワード線レベルの不良のときとで、スペアワード線の選択態様を変更する。スペア判定結果信号SP2が活性化される時同時にスペア判定結果信号SP1が活性化される時には、3本のノーマルサブワード線間においてショート不良が存在する。この場合には、スペア判定結果信号SP1が活性化されるため、ノーマルロウデコーダ264が非活性状態であり、スペアメインワード線のみが選択されてスペアサブワード線対により不良救済が実行される。この場合においても、ツインセルモードにしたがってサブワード線を選択することができる。

(もっと読む)

半導体記憶装置

【課題】メインアンプから見てメモリセルアレイ側における配線長の差を低減する。

【解決手段】X方向に沿って配置されたメイン入出力線MIOXと、X方向に沿って配置された複数の入出力ノードNDと、複数の増幅回路AMPを含む増幅回路領域AMPAと、Y方向に沿って配置され、メイン入出力線MIOXの夫々と対応する入出力ノードNDとを各々接続する複数のメイン入出力線MIOYとを備える。互いに異なる増幅回路AMPに割り当てられたメイン入出力線MIOYのうち、配線長の長いものほど対応するメイン入出力線MIOXのより中央部に接続され、配線長の短いものほど対応するメイン入出力線MIOXのより端部に接続されている。これにより、信号経路ごとの配線長の差が小さくなるとともに、最も長い配線経路の配線長が短縮される。

(もっと読む)

半導体記憶装置

【課題】高集積化と動作の安定化を実現したマルチバンク構成の半導体記憶装置を提供する。

【解決手段】第1方向に沿って配置された複数のメモリアレイ領域と、上記複数のメモリアレイ領域と交互に配置された複数のワード選択領域とを有し、上記複数のメモリアレイ領域には、それぞれ上記第1方向に沿って設けられた複数のワード線と、上記第1方向と直交する第2方向に沿って設けられた複数のビット線と、上記複数のワード線と上記複数のビット線との交差部に対応して設けられた複数のメモリセルとを備え、各ワード線選択領域に隣接する両側のメモリアレイ領域のうちの一方に延びるワード線及び他方に延びるワード線のそれぞれに対応してワード線選択回路が上記各ワード線選択領域内に設けられ、各メモリアレイ領域に対するそれぞれのワード線選択タイミングが独立に制御される。

(もっと読む)

半導体記憶装置

【課題】アクセス対象外の回路領域をアドレス信号に基づいてダイナミックに非活性化させることにより、諸費電力を低減する。

【解決手段】アドレス信号に基づいて選択される複数の回路領域をそれぞれ有し、対応するバンク選択信号(ソーストランジスタ制御信号STC1〜STC4)によって選択される複数のメモリバンク21〜24と、バンク選択信号に基づいて選択されるメモリバンクに含まれる複数の回路領域のうち、アドレス信号PX0〜PX7に基づいていずれかの回路領域を活性化させるとともに、残りの回路領域の少なくとも一つを非活性化させる選択的活性化回路200とを備える。本発明によれば、外部コマンドによる一括制御ではなく、アドレス信号に応じたダイナミックな制御によって、アクティブ時における消費電力を削減することが可能となる。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】アクセス速度の低下を最小限に抑制しつつ、プリデコード信号のリセットによる消費電力の増大を防止する。

【解決手段】ロウアドレスRADTをプリデコードすることによりプリデコード信号RFを生成するプリデコーダ100と、ロウアドレスRADTが不良アドレスであるか否かを判定する救済判定回路300と、救済判定回路300によりロウアドレスRADTが不良アドレスであると判定された場合に、救済アドレスRREDを生成する救済アドレスデコーダ400と、プリチャージコマンドの発行に応答して、プリデコード信号RFをリセットすることなく救済アドレスRREDをリセットする信号制御回路200とを備える。これにより、プリデコード信号RFのリセットによる消費電力の増大が防止される一方、ロウ系アクセスを律速する冗長パスについては高速なアクセスが担保される。

(もっと読む)

1 - 20 / 48

[ Back to top ]