Fターム[5M024CC63]の内容

Fターム[5M024CC63]に分類される特許

1 - 20 / 51

半導体装置

【課題】ダミーマットの占有面積を縮小する。

【解決手段】半導体装置は、ビット線32と、ビット線に接続された複数のメモリセル31と、ダミービット線52と、ダミービット線にソース及びドレインの一方が接続された複数のダミーセルトランジスタ51と、ビット線とダミービット線との間に接続されたセンスアンプ33とを有し、複数のダミーセルトランジスタの各々のソース及びドレインの他方は、フローティング状態にされるか、又はダミービット線に接続されている。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

半導体装置

【課題】回路規模が小さい階層型DRAMを提供すること。

【解決手段】それぞれが複数のメモリセルと、前記メモリセルに接続されたビット線と、前記ビット線をプリチャージするプリチャージ回路とを有し、行方向及び列方向にマトリクス状に配置された複数のサブアレイと、前記列方向に沿って延設され、前記サブアレイの列を選択するための列選択信号線と、前記行方向に沿って延設され、前記サブアレイの行を選択するためのメインワード線と、前記プリチャージ回路に対してプリチャージ信号を供給するプリチャージ信号線と、を備え、前記行方向または前記列方向に並べて配置された少なくとも2つの前記サブアレイが前記プリチャージ信号に応じて同一論理で制御される半導体装置。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

スイッチトランジスタを有しない差動センス増幅器

【課題】回路全体の面積を増やし、製造コストを押し上げるため、センス増幅器に使用される面積を最小限に抑える技術を提供する。

【解決手段】第1のビットライン(BL)に接続された出力と第2のビットライン(/BL)に接続された入力を有する第1のCMOSインバータと、第2のビットライン(/BL)に接続された出力と、第1のビットライン(BL)に接続された入力を有する第2のCMOSインバータと、第1のビットラインおよび第2のビットラインをそれぞれ第1のグローバルビットラインおよび第2のグローバルビットラインに接続するように配列された一対のパスゲートトランジスタを有し、それぞれのCMOSインバータはプルアップトランジスタM21、M22およびプルダウントランジスタM31、M32を備え、パスゲートトランジスタは、プルアップトランジスタ又はプルダウントランジスタによって構成される。

(もっと読む)

低電圧用半導体メモリ装置の駆動方法

【課題】ブリード電流の発生を防止し、プリチャージ動作の電力消費を節減する。

【解決手段】オープンビットライン構造を有する半導体メモリ装置の駆動方法において、第1セルアレイ300aに設置されている第1ビットラインにデータ信号を出力するデータ伝送ステップと、第2セルアレイ300bに設置されている第2ビットラインに基準信号を出力する基準信号伝送ステップと、第1ビットライン及び第2ビットラインのうち、電圧の低い方のビットラインの電圧を接地電圧に増幅して維持する補助センシングステップと、第1センスアンプノード及び第2センスアンプノードの電圧を等価化し、フローティングさせるプリチャージステップとを含み、センシングステップ動作を、接地電圧より低いレベルの低電圧、及び電源電圧よりも高いレベルの高電圧を用いて実行し、低電圧が第1ビットライン及び前記第2ビットラインに伝送されないようにクランピングする。

(もっと読む)

半導体装置及び半導体装置を含む情報処理システム

【課題】センスアンプからデータ線への信号伝送時の振幅の増大に起因する動作電流の増加を防止し得る半導体装置を提供する。

【解決手段】本発明の半導体装置は、センスアンプ回路30、データ線LIO(T/B)、MIO(T/B)、リードアンプ回路31、スイッチ回路Q10、Q11、スイッチ回路Q14、Q15、スイッチ回路Q18、Q19、電荷転送トランジスタQ20、Q21、電位設定回路Q12、Q13、電位設定回路Q16、Q17を備えている。データ線LIOT、MIOTは、リードアンプ回路31の駆動電位である第1の電位より低い第2の電位に制御され、スイッチ回路Q14〜Q16のゲート電位は第1の電位に制御され、電荷転送トランジスタQ20、Q21のゲート電位(VTG)は、その閾値電圧に第2の電位を加えた固定電位に制御され、センスアンプ回路30からリードアンプ回路31に伝送される情報の増幅動作が行われる。

(もっと読む)

半導体装置

【課題】ダミーセルを設けたメモリセルアレイのセンスマージンの向上とビット線ノイズの低減が可能な半導体装置を提供する。

【解決手段】相補対をなすビット線BL、/BL、同じ構造のメモリセルMCL、MCR及びダミーセルDCL、DCR、差動型のセンスアンプSA、ビット線BL、/BLをイコライズするイコライズ回路(Q1)を備え、ビット線イコライズ期間に、メモリセルMCL、MCRをビット線BL、/BLから切り離しダミーセルDCL、DCRをビット線BL、/BLに接続した状態でイコライズ回路でビット線BL、/BLをイコライズし、メモリセルMCLへのアクセス時に、イコライズ回路を非活性にし、ダミーセルDCLをビット線BLから切り離し、メモリセルMCLをビット線BLに接続し、センスアンプSAを活性化する。よって、ビット線BL、/BLの容量バランスを確保し、センスマージンの向上とビット線ノイズの低減を実現できる。

(もっと読む)

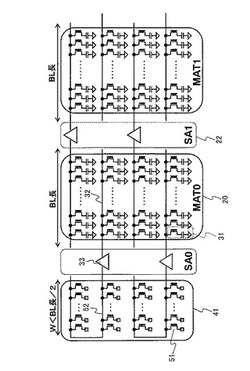

半導体記憶装置

【課題】シェアードセンスアンプ方式でセルフブートを用いた半導体記憶装置において、回路面積を縮小し、消費電流を削減する。

【解決手段】半導体記憶装置は複数のセンスアンプアレイ148と複数のドライバ部112−113、115−116とを具備する。センスアンプアレイ148はビット線対blu、/bluとセンスアンプ部102とメモリアレイ部101とスイッチ部114、117とを備える。センスアンプ部はビット線対に接続される。メモリアレイ部はビット線対に接続され、センスアンプ部の両外側に設けられる。スイッチ部はメモリアレイ部とセンスアンプ部との間に設けられる。メモリアレイ部は複数のワード線WLUとビット線対との交点に設けられた複数のメモリセル128、130を含む。スイッチ部は、メモリセルの選択時に、ドライバ部が生成するスイッチ部を制御する信号に基づいて、セルデータを伝播する。

(もっと読む)

半導体メモリおよびメモリシステム

【課題】 ビット線のフローティング期間が長くなる場合にも、ビット線の電圧レベルをプリチャージ線の電圧レベルに保持することで、アクセス動作時のセンスアンプの誤動作を防止しながら、ワード線とビット線のショートに伴うリーク電流を削減する。

【解決手段】 半導体メモリは、複数のメモリセルと、前記メモリセルに接続されたワード線およびビット線とを有するメモリブロックと、前記ビット線をプリチャージ線に接続するためのプリチャージスイッチと、前記メモリブロックに共有されるセンスアンプと、発振信号を周期的に出力するタイマと、アクセス動作の開始に応答して、前記プリチャージスイッチを一時的にオンし、アクセス動作が実行されない期間に前記発振信号に応答して、前記プリチャージスイッチを一時的にオンするスイッチ制御回路とを有している。

(もっと読む)

半導体装置及び情報処理システム

【課題】半導体装置の微細化により伝送線を高密度に配置する場合であっても、隣接する伝送線間のカップリングノイズの影響を抑制し得る半導体装置を提供する。

【解決手段】本発明の半導体装置は、センスアンプSAe、SAo、グローバルビット線GBLLe、GBLRe(第1、第2の伝送線)、ローカルビット線LBLLe、LBLRe(第3の伝送線)、スイッチS1e、S1o、S3Le、S3Reを備えている。例えばグローバルビット線GBLReの非アクセス時は、スイッチS1eが非導通状態に制御され、かつスイッチS3Reを介してローカルビット線LBLReに固定電位VGBPが供給されるように制御が行われる。よって、ローカルビット線LBLReへのカップリングノイズの影響を抑制してメモリセルMCの電荷のリークを防止し、グローバルビット線GBLReをシールドとして機能させ、動作マージンの向上と充放電電流の削減が可能となる。

(もっと読む)

半導体記憶装置

【課題】ビット線のプリチャージ時間を短縮し、高速動作可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1及び第2の増幅器(SA0、SA1)と、第1の増幅器(SA0)の入力端を一端として互いに逆方向に他端へと延在する第1のビット線対(BLB0、BLT0)と、第2の増幅器(SA1)の入力端を一端として互いに逆方向に他端へと延在する第2のビット線対(BLB5、BLT5)と、第1のビット線対の一端を互いに接続する第1のイコライズ回路(プリチャージ回路PC1)と、第2のビット線対のうちの一方のビット線の他端と第1のビット線対のうちのいずれか一方のビット線の一端とを接続する第2のイコライズ回路(プリチャージ回路PC2)と、を備える。

(もっと読む)

半導体記憶装置

【課題】複数の動作モードに対応しつつ、消費電力の増加を抑制する。

【解決手段】半導体記憶装置(1)の電源回路(10)を、電源電圧(Vcc)と接地電圧(GND)との中間の第1中間電圧(1/2Vcc)を生成する第1中間電圧生成回路(21)と、第2中間電圧(1/2Vcc)を生成する第2中間電圧生成回路(22)と、第1中間電圧(1/2Vcc)を供給する第1出力ノード(27)と、第2中間電圧(1/2Vcc)を供給する第2出力ノード(28)と、接続制御回路(23)とを具備するように構成する。第1中間電圧生成回路(21)は、第1制御信号に応答して第1中間電圧(1/2Vcc)を供給する。第2中間電圧生成回路(22)は、第1制御信号に応答して動作を停止する。接続制御回路(23)は、第2中間電圧生成回路(22)が動作を停止しているときに、第1出力ノード(27)と第2出力ノード(28)とを接続する。

(もっと読む)

半導体メモリ装置及びビットライン感知増幅回路の駆動方法

【課題】本発明は、メモリセルに書込みデータを伝達する時間を改善し、メモリセルのデータ保持時間を向上できる半導体メモリ装置を提供する。

【解決手段】本発明の半導体メモリ装置は、フルアップ電源ライン及びプルダウン電源ラインを介して供給される駆動電源によりビットライン対のデータを感知し増幅して、増幅されたデータをメモリセルに伝達するビットライン感知増幅部;及び、アクティブモード時、フルアップ電源ライン及びプルダウン電源ラインにフルアップ駆動電圧及びプルダウン駆動電圧を供給し、プリチャージモード時、メモリセルの非活性化時点までフルアップ電源ライン及びプルダウン電源ラインにフルアップ駆動電圧よりも高い電圧レベルのオーバードライビング電圧及びプルダウン駆動電圧を供給するビットライン感知増幅電源供給部を備える。

(もっと読む)

半導体記憶装置

【課題】データ保持モード時における消費電力を低減する。

【解決手段】ビット線対に対しても受けられるビット線イコライズ回路(BEQL)は、スタンバイ時に高抵抗状態に設定されて、電流制限されたビット線イコライズ電圧を対応のビット線に伝達する。スタンバイ期間中、ビット線イコライズ指示信号BLEQLの電圧レベルを中間電圧Vaレベルに設定し、MOSトランジスタT1−T3のチャネル抵抗Rを大きくし、ビット線プリチャージ電圧VBLの供給源からビット線BLL(ZBLL)およびマイクロショートを介してサブワード線SWLa、SWLbへ流れる電流を制限する。これにより、マイクロショートMRが数多く存在する場合においても、このMOSトランジスタT2およびT3の電流制限機能により、スタンバイ期間中のリーク電流を低減することができ、スタンバイ電流の増大を抑制することができる。

(もっと読む)

半導体集積回路装置

【課題】雑音特性が優れ、かつサイズが小さいメモリアレイ及びそのメモリアレイを備えた半導体集積回路装置を提供する。

【解決手段】ビット線と定電圧との間に、順番に直列に接続された2つのトランジスタと1つの記憶蓄積素子とを備えたメモリセルは、2つのトランジスタのゲート電極に第1のワード線、第2のワード線がそれぞれ接続され、メモリアレイは、メモリセルがビット線と第1のワード線が交差する全ての交点に配置されたマットと、同一マット内のビット線対を入力とするセンスアンプと、第1及び第2のワード線を出力する第1及び第2のワードドライバと、を備える。

(もっと読む)

半導体集積装置

【課題】プリチャージ回路の高速化に限界があった。

【解決手段】本発明は、半導体記憶回路と、前記半導体記憶回路の周辺回路とを有する半導体集積装置であって、前記周辺回路は、ゲート酸化膜の耐圧が第1の電圧である第1のトランジスタを有し、前記半導体記憶回路は、いずれか一方に、メモリセルのゲートトランジスタが接続されるビット線対と、前記第1のトランジスタと実質的に同じ耐圧のトランジスタで構成され、活性化信号に応じて前記ビット線対を所定の電圧にプリチャージするプリチャージ回路と、を有し、前記プリチャージ回路の活性化信号に前記第1の電圧よりも高い第2の電圧が用いられる半導体集積装置である。

(もっと読む)

半導体記憶装置

【課題】面積増大および消費電力の増大を招来することなく、データ読出しの高速化、安定化を図る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、センスアンプ3がビット線対BL、BLBの電位の読み出しを開始するときのビット線の電位をレベルシフトさせるレベルシフト手段を備える。レベルシフト手段は、一方の電極が各ビット線に接続され、ビット線対ごとに二つで1対となるレベルシフト用キャパシタSFTCと、レベルシフト用キャパシタSFTCの他方の電極に共通に接続され、この他方の電極の共通ノードにシフト容量駆動信号SFTを与えて所定タイミングでレベルシフト用キャパシタSFTCの蓄電量を変化させるタイミングジェネレータ5と、を備える。

(もっと読む)

メモリ回路、およびメモリ回路にアクセスする方法

【課題】半導体回路に関するメモリ回路、システム、およびビット線イコライズ電圧の提供方法を提供する。

【解決手段】メモリ回路であって、データを表す電荷を蓄え、ワード線およびビット線対の第1のビット線に接続される少なくとも1つのメモリセルと、ビット線対の第1のビット線と第2のビット線との間に接続された少なくとも1つのビット線イコライズトランジスタと、ビット線イコライズトランジスタに接続され、メモリセルのアクセスサイクル前の待機期間中、第1のビット線および第2のビット線の電圧を実質的に均等化するためにパルスをビット線イコライズトランジスタに提供するように構成されるビット線イコライズ回路とを含む、メモリ回路。

(もっと読む)

半導体装置

【課題】本発明は、このような事情に鑑みてなされたもので、高精度の閾値電圧制御が必要なMOSトランジスタに対し、従来に比較して閾値電圧の製造バラツキを低減させ、かつチップ面積を従来と同様とする半導体装置を提供する。

【解決手段】本発明の半導体装置は、n型のウェルNW1内に高精度の閾値電圧制御が必要なpMOSトランジスタ1−P1a、1−P1bを形成する際、ウェルNW1の外縁50あるいは51からの距離を大きくし、この空いた領域に、pMOSトランジスタ1−P1a、1−P1bのように高精度の閾値電圧制御が必要のないMOSトランジスタ1−P3a、1−P4a、1−P3b、1−P4bを形成することで、不純物濃度の均一な領域において、高い閾値電圧制御の必要なMOSトランジスタの閾値電圧の制御性を向上させ、かつ外縁50あるいは51近傍の不純物濃度が不均一な領域に高精度の閾値電圧制御の必要がないMOSトランジスタを形成することで、ウェル内を有効に用いている。

(もっと読む)

1 - 20 / 51

[ Back to top ]