Fターム[5M024QQ01]の内容

Fターム[5M024QQ01]に分類される特許

1 - 20 / 21

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体表示装置

【課題】作製工程を複雑化させることなく、高集積化を実現することが可能な、DRAM混載の集積回路の提供。

【解決手段】DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体記憶装置およびメモリ制御システム

【課題】マイコンシステムにおいて制御しやすいロジック内蔵DRAMを提供する。

【解決手段】インタフェース部2は、アドレス信号ADD.で指定される領域が、ロジック制御領域である場合には、DRAM4とデータを授受する代わりに、レジスタ6とデータ授受を行なう。その際のデータ信号DATAは、レジスタ6に保持されるロジック回路8に対する制御コマンドや、処理のための入力データである。レジスタ6の保持内容に応じて、ロジック回路8は、たとえば、暗号処理や、画像処理等の、マイコンでは時間を要してしまう処理を実行する。処理結果はレジスタ6に保存され、DRAMに対する読出と同様のシーケンスで読出される。

(もっと読む)

半導体メモリ装置およびその動作方法

【課題】各種のメモリタイプのメモリとして使用でき、しかも、コントロールデバイスにおける制御負担を軽減できる半導体メモリ装置およびその動作方法を提供する。

【解決手段】メモリアレイが形成されたメモリアレイ部3と、外部装置とメモリアレイ部3との間のインターフェースを行うインターフェース部2と、インターフェースに応じたモードを示す任意のモード信号を設定可能なモード信号保持部25と、を有し、インターフェース部2は、複数のメモリタイプにそれぞれ対応し、モード信号に応じて選択的に上記外部装置と上記メモリアレイ部との間のインターフェース処理に適用される複数のインターフェースモジュールを含み、モード信号保持部25は、各モード信号が記憶される不揮発性メモリと、不揮発性メモリから読み出されたコマンドを一時的に保持しておくモードレジスタと、を含む。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

半導体装置

【課題】製造ばらつきおよび特性変動による影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1のメモリ回路CM1の記憶データに基づく信号が現われる第1の制御線ML1と、第1の制御線ML1に現われた信号に対する読み出し特性を調整する第1の特性調整回路CL1と、第2のメモリ回路CM1Tの記憶データに基づく信号が現われる第2の制御線MLTと、第2の制御線MLTに現われた信号に対する読み出し特性を調整する第2の特性調整回路CLTと、第2の特性調整回路CLTによる調整結果に基づいて制御信号を生成する制御信号生成回路11とを備え、第1の特性調整回路CL1は、第1の制御線ML1に現われた信号に対する読み出し特性を制御信号に基づいて調整し、第2のメモリ回路CM1Tには、第1のメモリ回路CM1と異なる電源電圧が供給される。

(もっと読む)

半導体メモリ装置、半導体メモリ装置の動作方法

【課題】各種のメモリタイプのメモリとして使用できる半導体メモリ装置の実現。

【解決手段】半導体メモリ装置としてのメモリICチップのパッケージ内に、DRAM又はSRAMとしてのメモリアレイ部が設けられていることに加え、例えばSDR、DDR、DDR2・・・DDR(n)、SRAM、DPRAM、FIFO等の各種のメモリタイプに応じた複数のインターフェースモジュールも設けられているようにする。各インターフェースモジュールは、それぞれ外部のメモリ制御回路からのアクセス要求に応じて、対応するメモリタイプに合致するタイミングでデータ書込/読出を行う。モード制御によって機能するインターフェースモジュールが動作状態とされることで、指示するモードに応じて各種のメモリタイプのメモリとして動作できるようにする。

(もっと読む)

半導体メモリ装置、半導体メモリ装置の動作方法

【課題】各種のメモリタイプのメモリとして使用できる半導体メモリ装置の実現。

【解決手段】半導体メモリ装置としてのメモリICチップのパッケージ内に、DRAM又はSRAMとしてのメモリアレイ部が設けられていることに加え、例えばSDR、DDR、DDR2・・・DDR(n)、SRAM、DPRAM、FIFO等の各種のメモリタイプに応じた複数のインターフェースモジュールも設けられているようにする。各インターフェースモジュールは、それぞれ外部のメモリ制御回路からのアクセス要求に応じて、対応するメモリタイプに合致するタイミングでデータ書込/読出を行う。例えばSDR用のインターフェースモジュールは、メモリアレイ部に対する書込/読出を、外部からはSDRメモリアレイと見られるようにする入出力を行う。これにより、各種のメモリタイプのメモリとして動作できるようにする。

(もっと読む)

半導体記憶装置

【課題】待機動作における消費電力を削減すると共に、待機機能の実装に伴う面積オーバヘッドを最小化した半導体記憶装置を提供する。

【解決手段】セルデータを記憶するメモリセルアレイ1と、セルデータの誤り訂正のための冗長データを記憶する冗長メモリセルアレイ2とにより、ビット線BLが共有される。セルデータ及び冗長データは、センスアンプ5により検知・増幅されて巡回冗長符号化器/復号化器7に出力される。巡回冗長符号化器/復号化器7は、セルデータを逐次処理して符号化して冗長データを生成し又はセルデータ及び冗長データを逐次処理して復号化しセルデータの誤り訂正を実行する。ロウデコーダ3,4及びカラムデコーダ9がビット線BL、ワード線WL及び冗長ワード線RWLを選択的に活性化することにより、巡回冗長符号化器/復号化器7が出力したセルデータ及び冗長データがメモリセルアレイ1又は冗長メモリセルアレイ2に書き込まれる。

(もっと読む)

半導体集積回路

【課題】集積回路内では、それぞれの回路の事情により最適なゲート長とゲート酸化膜厚としきい値電圧があることになる。これらの回路を同一基板上に集積する半導体集積回路では、それぞれの回路の最適な値にするために製造工程が複雑化し、結果として歩留まりの低下、製造日数の増加に伴い製造コストの上昇をもたらす。

【解決手段】論理回路には高低2種類のしきい値のトランジスタを用い、メモリセルには高しきい値電圧と同じしきい値電圧のトランジスタにより構成し、入出力回路は上記の高しきい値電圧と同じチャネルの不純物濃度でゲート酸化膜厚を厚くしたトランジスタを用いて構成する。

(もっと読む)

半導体記憶装置

【課題】本発明は、メモリコア回路がアクティブ状態でデータ書き込み動作の開始を待っている期間において、電源回路における電流の消費を削減することが可能な半導体記憶装置を提供することを目的とする。

【解決手段】半導体記憶装置は、ワード線を含むDRAMメモリコア回路と、第1の状態と第2の状態との何れか選択された一方において動作することにより所定の電源電圧を生成してDRAMメモリコア回路に供給し、第2の状態においてよりも第1の状態においての方がより大きな電流を消費する電源回路と、DRAMメモリコア回路のワード線が活性化されてから非活性化されるまでの期間に電源回路を第1の状態から第2の状態に移行させ更に第1の状態に戻すように電源回路を制御する制御回路を含むことを特徴とする。

(もっと読む)

書込みデータに基づいて選択的に行付勢するためのシステム及び方法

【課題】

選択的行付勢システムを用いて書込みデータに基づいた選択的な行付勢を行うシステムおよび方法を提供する。

【解決手段】

システムは、M個の行104およびN個の列106を有するストレージ・アレイ102と、Nビットのデータ・ワード・レジスタ108と、データ・ワードに応答して、データ・ワードが均一であるとき、第1の値を有する均一ワード・データ・ビットを生成する均一検出回路110と、各々がM個の行104の1つと関連付けられ、関連する行に記憶されたデータ・ワードに対する均一ワード・データ・ビットを記憶するM個の均一検出ラッチ114を含む、Mビットの均一検出レジスタ112と、M個の行104の各々に対する均一ワード・データ・ビットに応答して、第1の値を有する均一ワード・データ・ビットに対するM個の行104の付勢を禁止するMビットの行ドライバ装置116とを含む。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の静的消費電流テストを、一枚のウェーハ上で、複数の半導体集積回路装置で同時に行っても、半導体集積回路装置個々の静的消費電流特性を、高い精度で測定できる半導体集積回路装置を提供すること。

【解決手段】 少なくとも2つ以上の第2導電型の第1の半導体領域22と、半導体基板と絶縁され、第1の半導体領域22に形成された第1導電型の第2の半導体領域25と、少なくとも2つ以上の第1の半導体領域22を分離、かつ隣接して形成し、第1の半導体領域22と第2の半導体領域25とに形成される半導体素子により構成された半導体集積回路部と、半導体集積回路部に動作電圧を与えるために、第1の半導体領域22と第2の半導体領域25に少なくとも1つの高電位及び低電位電源端子と、少なくとも2つ以上の第1の半導体領域22を分離、かつ隣接して形成された領域以外に、基板にバイアス電位を印加する端子503を具備する。

(もっと読む)

半導体メモリ装置及びこれを具備するメモリシステム、並びにそのスイング幅制御方法

【課題】半導体メモリ装置及びこれを具備するメモリシステム、並びにそのスイング幅制御方法を提供する。

【解決手段】半導体メモリ装置は、校正コードに応答してデータスイング幅をそれぞれ可変する複数の出力ドライバと、対応する出力ドライバのデータスイング幅によって校正コードを可変してデータスイング幅を校正スイング幅に校正した後、対応する出力ドライバのデータが正常に伝送される範囲内で校正コードを再び可変してデータスイング幅を減少させる複数のデータスイング幅制御部とを具備することを特徴とする。これによって、半導体メモリ装置は、データが正常に伝送される範囲内でデータのスイング幅を最小化し半導体メモリ装置の電力消費を最小化すると共に、メモリシステムの動作性能を向上させる。

(もっと読む)

半導体装置

【課題】半導体記憶装置においてデータの破壊や誤読み出しを防止する。

【解決手段】半導体記憶装置は、ビット線BLと接続された差動増幅型センスアンプ11と、ビット線BLとデータ線DLとの接続・非接続を切替制御するカラム選択スイッチ12を含むデータ伝送回路とを備えている。ビット線BLには、容量制御スイッチQn7を介して付加容量C1が設けられている。読み出し動作状態において差動増幅型センスアンプ11が起動された後であってカラム選択スイッチ12によってデータ線DLとビット線BLとが接続される前に、容量制御スイッチQn7によって付加容量C1とビット線BLとが接続される。

(もっと読む)

低電圧センス増幅器および方法

第1センス増幅器(110)は、一対の相補センス線(S、S*)間に接続された相補入力および出力を有する。各センス線(150、152)は、結合トランジスタを介して、各相補ディジット線(D、D*)に接続される。結合トランジスタは、初期センス期間に起動され、ディジット線からの差動電圧をセンス線に接続する。その後センス線は、ディジット線から分離され、ディジット線の容量からの負荷を受けることなく、第1センス増幅器を差動電圧に対応させる。また、センス線は、ディジット線に接続された相補出力を有する第2センス増幅器の相補入力に接続される。第2センス増幅器(120)をディジット線ではなくセンス線に接続することにより、第2センス線に印加された差動電圧は、ディジット線間の差動電圧よりも早く増加する。  (もっと読む)

(もっと読む)

半導体集積回路装置及びそのテスト方法

【課題】

メモリマクロに対して冗長置き換え情報を記憶する不揮発性記憶回路の数を削減できるとともに、冗長置き換え情報の転送のための入出力回路を簡素化できる半導体集積回路装置を提供すること。

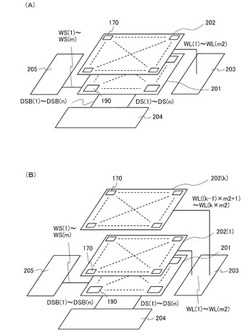

【解決手段】

本発明にかかる半導体集積回路装置では、不良セルを置き換える冗長回路を有する複数のメモリマクロ3と、複数のメモリマクロ3から選択される第1のメモリマクロ3の不良セルを冗長回路に置き換えるための冗長置き換え情報を記憶する複数のヒューズボックス2とを備え、冗長置き換え情報は、ヒューズボックス2からメモリマクロ3へ並列に転送される。

(もっと読む)

1 - 20 / 21

[ Back to top ]