国際特許分類[C23C16/24]の内容

化学;冶金 (1,075,549) | 金属質材料への被覆;金属質材料による材料への被覆;化学的表面処理;金属質材料の拡散処理;真空蒸着,スパッタリング,イオン注入法,または化学蒸着による被覆一般;金属質材料の防食または鉱皮の抑制一般 (47,648) | 金属質への被覆;金属材料による材料への被覆;表面への拡散,化学的変換または置換による,金属材料の表面処理;真空蒸着,スパッタリング,イオン注入法,または化学蒸着による被覆一般 (43,865) | ガス状化合物の分解による化学的被覆であって,表面材料の反応生成物を被覆層中に残さないもの,すなわち化学蒸着 (14,497) | 金属質材料以外の無機質材料の析出に特徴のあるもの (4,650) | けい素のみの析出 (411)

国際特許分類[C23C16/24]に分類される特許

1 - 10 / 411

シリコンエピタキシャルウェーハの製造方法

【課題】エピタキシャル成長の際の裏面クモリやピンハローを抑制して、高品質なシリコンエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】気相成長装置を用いて、サセプタのウェーハ載置面上にシリコン単結晶基板を載置して、該シリコン単結晶基板上にエピタキシャル成長させることによりシリコンエピタキシャルウェーハを製造する方法であって、サセプタとして、SiCにより表面をコートされた黒鉛製サセプタをチャンバー内に配設し、黒鉛製サセプタのウェーハ載置面上にポリシリコンのコートは行わずに、ウェーハ載置面上にリフトピンによりシリコン単結晶基板を載置して、シリコン単結晶基板上にエピタキシャル成長させることで、エピタキシャル成長においてシリコン単結晶基板の裏面のリフトピンの先端部に対向する領域に発生する面荒れを防止するシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

気相成長装置の清浄度評価方法

【課題】 気相成長装置の清浄度を高感度で評価することができる清浄度評価方法を提供する。

【解決手段】 気相成長装置の清浄度を評価する方法であって、厚み1000μm以上2000μm以下のシリコンウェーハを準備し、前記気相成長装置を用いて、前記シリコンウェーハ上にシリコンエピタキシャル層を成長させたモニタウェーハを作製し、前記モニタウェーハのライフタイム値を測定し、前記測定したモニタウェーハのライフタイム値から前記気相成長装置の清浄度を評価することを特徴とする気相成長装置の清浄度評価方法。

(もっと読む)

シリコン酸化物膜の成膜方法

【課題】 表面ラフネスが良好なシリコン酸化物膜を得ることが可能なシリコン酸化物膜の成膜方法を提供すること。

【解決手段】 下地1上にシード層2を形成する工程と、シード層2上にシリコン膜3を形成する工程と、シリコン膜3及びシード層2を酸化し、下地1上にシリコン酸化物膜4を形成する工程と、を具備する。

(もっと読む)

気相成長装置の清浄度評価方法

【課題】 気相成長装置の清浄度を高感度で評価することができる清浄度評価方法を提供する。

【解決手段】 気相成長装置の清浄度を評価する方法であって、前記気相成長装置を用いて、シリコンウェーハ上に、該シリコンウェーハの厚みに対する割合が20%以上100%以下である厚みを有するシリコンエピタキシャル層を成長させたモニタウェーハを作製し、前記モニタウェーハのライフタイム値を測定し、前記測定したモニタウェーハのライフタイム値から前記気相成長装置の清浄度を評価することを特徴とする気相成長装置の清浄度評価方法。

(もっと読む)

電子写真感光体の製造方法

【課題】堆積膜の均一性と特性の向上及び画像欠陥の抑制を同時に達成可能な電子写真感光体の製造方法を提供する。

【解決手段】減圧可能な反応容器の内部への円筒状基体設置工程と、反応容器の内部への堆積膜形成用原料ガス導入工程と、反応容器の内部にあって円筒状基体とは離間して配置された電極、および円筒状基体の、一方の電位に対する他方の電位が交互に正と負になるように、正弦波の交番電圧を電極と円筒状基体の間に印加して、原料ガスを分解し、円筒状基体の表面に堆積膜を形成する堆積膜形成工程と、を有するプラズマCVD法によって電子写真感光体を製造する方法において、交番電圧の周波数が10kHz以上300kHz以下で、電極と円筒状基体の一方の電位に対する他方の電位が、正であるときの電位差の絶対値の最大値、および負であるときの電位差の絶対値の最大値は、一方が放電維持電圧未満の値であって、他方が放電開始電圧以上の値である。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】エピタキシャル成長の際の裏面クモリ及びピンハローを抑制して、高品質なシリコンエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】チャンバー内に配設されたサセプタのウェーハ載置面上にシリコン単結晶基板を載置して、該シリコン単結晶基板上にエピタキシャル成長させることによりシリコンエピタキシャルウェーハを製造する方法であって、前記シリコン単結晶基板を載置する前に、前記チャンバー内にシリコン原料ガスを流入させながら、50秒を超えて300秒以下の時間で、前記サセプタのウェーハ載置面上にポリシリコン膜を被覆し、その後前記サセプタのウェーハ載置面上に前記シリコン単結晶基板を載置してエピタキシャル成長させるシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

シード層の形成方法及びシリコン含有薄膜の成膜方法

【課題】 薄膜の面内均一性の更なる向上を可能とする、薄膜を形成するためのシード層の形成方法を提供すること。

【解決手段】 下地上に、薄膜のシードとなるシード層を形成するシード層の形成方法であって、アミノシラン系ガスを用いて、下地上に、アミノシラン系ガスに含まれた少なくともシリコンを吸着させる工程(ステップ11)と、ジシラン以上の高次シラン系ガスを用いて、アミノシラン系ガスに含まれた少なくともシリコンが吸着された下地上に、ジシラン以上の高次シラン系ガスに含まれた少なくともシリコンを堆積する工程(ステップ12)と、を具備する。

(もっと読む)

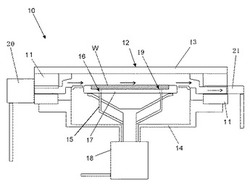

薄膜の形成方法及び成膜装置

【課題】比較的低温でも埋め込み特性が良好で且つ表面ラフネスの精度も向上するアモルファス状態の不純物含有のシリコン膜のような薄膜を形成することが可能な薄膜の形成方法を提供する。

【解決手段】真空排気が可能になされた処理容器内で被処理体Wの表面にシード膜88と不純物含有のシリコン膜90を形成する薄膜の形成方法において、処理容器内へアミノシラン系ガスと高次シランの内の少なくともいずれか一方のガスよりなるシード膜用原料ガスを供給してシード膜を形成する第1ステップと、処理容器内へシラン系ガスと不純物含有ガスとを供給してアモルファス状態の前記不純物含有のシリコン膜を形成する第2ステップとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

1 - 10 / 411

[ Back to top ]