国際特許分類[G06F11/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 故障の発生への応答,例.耐故障性 (1,764) | データの表現形態に冗長性をもたせることによるエラー検出またはエラー訂正,例.チェック・コードを用いることによるもの (355)

国際特許分類[G06F11/08]の下位に属する分類

国際特許分類[G06F11/08]に分類される特許

51 - 58 / 58

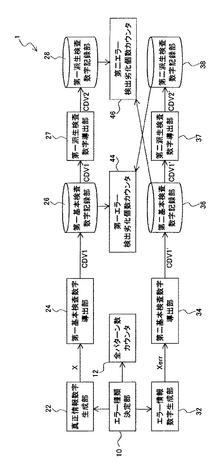

番号生成装置および番号検査装置、方法、プログラム、記録媒体

【課題】 チェックデジットにより情報数字の入力エラーをどれだけ発見できるかの程度を客観的に求める。

【解決手段】 真正な情報数字Xに基づき第一基本検査数字CDV1を導出する第一基本検査数字導出部24と、第一基本検査数字CDV1とは異なる第一派生検査数字CDV2(=CDV1+α)を導出する第一派生検査数字導出部27と、真正な情報数字Xに所定のエラーを発生させたエラー情報数字Xerrに基づき、第一基本検査数字導出部24と同一の方法により、第二基本検査数字CDV1’を導出する第二基本検査数字導出部34と、第一派生検査数字導出部27と同一の方法により、第二基本検査数字CDV1’とは異なる第二派生検査数字CDV2’(=CDV1’+α)を導出する第二派生検査数字導出部37と、第一基本検査数字CDV1と第二派生検査数字CDV2’とが等しくなる回数を数える第一エラー検出劣化個数カウンタ44とを備える。

(もっと読む)

情報記録再生方法と情報記録再生装置とデータ処理回路

【目的】 複数個のセクタデータに誤り訂正用データを付加したブロックデータ内のセクタデータの書き換え時間を短縮する。

【構成】 光ディスクから複数個のセクタデータにPIデータ、POデータを付加したブロックデータを再生し、その再生したデータをメモリ30に記憶し、その記憶したブロックデータの書き換え対象のセクタデータを書き換え、その書き換えたセクタデータに関係する誤り訂正用データであるPIデータ、POデータをパリティ生成回路31で生成し、その生成したPIデータ、POデータを上記読み出したブロックデータに付加して光ディスクに記録する。

(もっと読む)

記憶装置

【課題】

異常動作に至る前にメモリの信頼性が低下していることを検知して外部に通知する記憶装置を提供する。

【解決手段】

誤り訂正回路12は、フラッシュメモリ11からデータの読出し時に誤りの訂正を行い、誤り訂正が発生した場合にトグル出力回路15に出力信号を出力する。トグル出力回路15は、フラッシュメモリ11の読み出しアドレスを指定するアドレスレジスタ13の内容をラッチするラッチ信号をアドレスラッチ回路14aとアドレスラッチ回路14bとに交互に出力する。アドレスラッチ回路14a、14bは、アドレスレジスタ13の内容を保持する。比較回路16は、アドレスラッチ回路14aとアドレスラッチ回路14bとの内容を比較し、不一致となったことを検知した場合にカウントパルスをカウンタ17に出力する。カウンタ17が計数する値が所定の値になった場合に、割込信号20を出力して、外部に通知する。

(もっと読む)

リード・ソロモン復号方法及び装置

【課題】簡易な回路構成で誤り値を算出する。

【解決手段】本発明のリード・ソロモン復号回路は、シンドローム生成回路と、誤り位置多項式生成回路と、誤り値算出回路とを備えている。誤り値算出回路では、誤り位置多項式の係数の順番が逆転した多項式P(x)を算出し(ステップS11)、多項式P(x)を(x−α^pi),(i=0,1,…,k−1)で乗算したときの商として得られる多項式Pi(x)の係数μij(i,j|i,j=0,1,…,k−1)を求め(ステップS12)、係数μijを順次シンドロームsに乗じて累加算し、累加算して得られた値をPi(xi)で除算して、乗算して得られた値を誤り位置p(j|j=0,1,…,k−1)における誤り値e(i|i=0,1,…,k−1)を算出する(ステップS13)。

(もっと読む)

データ検査方式

【課題】 メモリ等に記憶されたデータとチェックサムとの総和値が所定値となるか否かで前記記憶されたデータを検査するデータ検査方式であっても,前記チェックサムの記憶されたアドレスが既知であるか否かにかかわらず前記記憶されたデータを識別することを可能としたデータ検査方式を提供する。

【解決手段】 ステップS4では,画像処理プログラムのデータ,チェックサム,及び識別情報の総和値が算出され,識別情報が抽出される。

そして,前記抽出された前記識別情報に基づいて,前記画像処理プログラムのバージョン等が識別される(ステップS5,データ識別手段に相当)。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】 エラーチェックに用いられるデータを記憶するメモリの容量を比較的小さくすることができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】 データ記憶部14には、所定のデータが記憶され、記憶された所定のデータがグループ分けされて、複数のデータブロック20が生成される。コード記憶部15には、データ記憶部14に記憶すべきデータブロック20毎に予め定める符合化処理を施すことによって得られる判定用CRC符合データが記憶される。したがって、データ記憶部14に記憶されるデータに対応する判定用CRC符合データをコード記憶部15に記憶する従来の技術に比べて、コード記憶部15に記憶する判定用CRC符合データのデータ量を少なくすることができる。これによって、従来の技術に比べて、判定用CRC符合データを記憶するコード記憶部15の容量を小さくすることができる。

(もっと読む)

情報処理装置におけるエラー訂正、検出装置

【課題】従来、ASICに接続されるDIMMの個数が多くなればなるほどPIN数が増えるので、ASICのLSIのサイズが大きくなりLSIのコストが高くなっていた。

【解決手段】第1のASIC群の各ASIC5、6は第1のASIC群内でECCの塊を作成しライトデータに対するECCコードの発生及びECCコードのライトデータへの付加機能とECCコード付きライトデータを第2のASIC群の各ASIC7、8へ振り分ける機能とDIMMからのリードデータに対するECCチェック及びECC訂正機能とを有し、第2のASIC群の各ASIC7、8はDIMMの制御を行う機能と、第1のASIC群で発生させたECCの塊がDIMMの中の同じ素子にアクセスしないようにライトデータの並替を行う機能と、DIMMからのリードデータに対しライト時に並替たデータを元に戻す機能を有し、各機能で1バイト誤り訂正又は2バイト誤り検出可能にした。

(もっと読む)

誤り率表示装置

【課題】 間違った誤り率の表示を防止できる誤り率表示装置を提供する。

【解決手段】 ビタビ復号器1は送信号をビタビ復号して出力する。ビタビ復号器1はビタビ復号を行なう際にエラーフラグをビタビ誤り率計算回路4に入力する。リード・ソロモン復号器3は、バイトデインタリーブ回路2によってデインタリーブされた伝送信号に対してリード・ソロモン復号を行う。リード・ソロモン復号器3はエラーフラグを誤り率表示回路7に入力する。ビタビ誤り率計算回路4は、ビタビ復号器1から出力されるエラーフラグを入力して第1誤り率を算出する。リード・ソロモン誤り率計算回路6は、リード・ソロモン復号器3から入力されるエラーフラグを入力して第2誤り率を算出する。誤り率表示回路7は、ビタビ復号制御信号、47h検出信号、第1誤り率、第2誤り率、訂正不能フラグを入力して表示を行なう。

(もっと読む)

51 - 58 / 58

[ Back to top ]