国際特許分類[G06F9/52]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | プログラム制御のための装置,例.制御装置 (15,360) | プログラム記憶方式を用いるもの,すなわちプログラムを受取りそして保持するために処理装置の内部記憶装置を用いるもの (15,354) | マルチプログラミング装置 (6,551) | プログラム同期;相互排除,例.セマフォによるもの (395)

国際特許分類[G06F9/52]に分類される特許

71 - 80 / 395

並列コンピュータシステム、プロセッサ、同期装置、通信方法および通信支援方法

【課題】集団通信の高速化を図れる並列コンピュータシステムを提供する。

【解決手段】各プロセッサは、通信フェーズごとに予測された通信フェーズでの自機の通信時間のうち少なくとも最長時間を示す通信時間情報と同期要求を同期装置に送信する処理手段と、同期装置から各通信フェーズの実行時間を特定するための実行時間情報と同期完了指示を受信する受信手段を含み、処理手段は、実行時間情報と同期完了指示が受信されると、集団通信を開始しかつ各通信フェーズで通信フェーズでの自機の通信時間が実行時間情報にて特定される実行時間以下であると、通信フェーズの期間を該実行時間とし、同期装置は、各プロセッサから通信時間情報と同期要求を受信すると通信時間情報に基づき実行時間情報を作成する作成手段と、実行時間情報と同期完了指示を複数のプロセッサに配信する配信手段と、を含む。

(もっと読む)

SIMDベクトルの同期

プロセッシングデバイス内のデコーダによって、第1記憶ロケーション、第2記憶ロケーション及び第3記憶ロケーションの間の複数のデータ要素に対するベクトル比較/交換オペレーションを規定する単一命令をデコードする段階と、プロセッシングデバイス内の実行ユニットによって実行するために、単一命令を発行する段階と、単一命令の実行に応答して、第1記憶ロケーションからのデータ要素と、第2記憶ロケーションにおける対応するデータ要素とを比較する段階と、一致が存在するかに応じて、第1記憶ロケーションからのデータ要素を、第3記憶ロケーションからの対応するデータ要素で置き換える段階とを実行することによって、ベクトル比較/交換オペレーションが実行される。 (もっと読む)

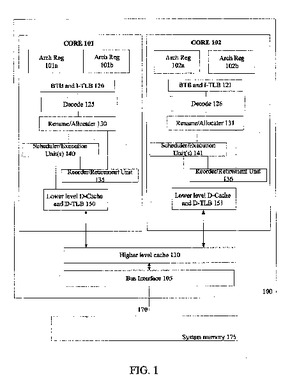

複数のコアおよびスレッドについてのタイムスタンプカウンタ(TSC)のオフセットの制御

【解決手段】 一実施形態によると、本発明は、システム一時停止の前にプロセッサの第1のTSCカウンタのタイムスタンプカウンタ(TSC)値を記録する段階と、システム一時停止の後に、格納されているTSC値にアクセスする段階と、プロセッサの複数のコアの間で同期を実行することなく、格納されているTSC値を用いてプロセッサの第1のコアで実行されている第1のスレッドに対応付けられているスレッドオフセット値を直接更新する段階とを備える方法を含む。他の実施形態も記載すると共に請求する。 (もっと読む)

バッファリングストアを利用してトランザクションを高速化するための機構

一実施例では、本発明は、第1スレッドにおいてトランザクショナルメモリ(TM)トランザクションを実行し、プロセッサのキャッシュメモリの第1バッファにデータのブロックをバッファリングし、第1バッファのブロックの位置におけるデータが更新されるエンカウンタタイムにブロックのオーナシップを取得するため、ブロックに対してライトモニタを取得する方法を含む。他の実施例が、開示及び請求される。  (もっと読む)

(もっと読む)

マルチスレッド処理方法及びマルチスレッド処理装置

【課題】複数の並列化モデルについて高速な同期を取ることができるマルチスレッド処理方法を提供する。

【解決手段】プログラムを分割した複数のスレッド11が並列して実行される。プログラムに複数のスレッド間の同期からのジャンプにより実行される第1の命令コードが存在する場合に、第1の命令コードの存在を示すtaskフラグが設定される。また、第1の命令コードが存在する場合に、複数のスレッド11の中で第1の命令コードが検出されたスレッド11を表すidフラグが設定される。idフラグが設定された場合に、idフラグにより表されるスレッド11において、taskフラグがリセットされるまで同期処理の実行を待つ。

(もっと読む)

適応的最適化された比較/交換オペレーション

【課題】適応型の最適化されたコンペア‐エクスチェンジオペレーションを実装する。

【解決手段】処理論理は、実行パイプラインにおいてFASTCMPXCHGオペレーションを受信する(200)。次いで、FASTCMPXCHG命令に関連付けられたマイクロアーキテクチャヒントビットを含むキャッシュラインタグを探す(202)。ハードウェアがFASTCMPXCHGを処理する能力を有する場合には、先行するCLMARKが利用可能なタグが、各キャッシュラインについて提示される。ハードウェアがタグを持っていない場合は、CLMARK及びFASTCMPXCHGは、サポートされない。その場合には、コードのリストに載っているFASTCMPXCHG命令の代わりに、[mem]、testval、及びnewvalパラメータを使用して標準的なCMPXCHG命令を実行する(212)。

(もっと読む)

システム、方法、プログラムおよびコード生成装置

【課題】処理負荷が軽いタスク間の排他制御方法を提供する。

【解決手段】何れかのタスクが排他ロックを取得および解放したことに応じて値が更新される更新情報と、排他ロックを取得しているタスクを識別するタスク識別情報とを記憶するロック状態記憶部26と、排他ロックを取得して第1タスクに含まれるクリティカルセクションの処理を実行させ、第1タスクに含まれるクリティカルセクションの処理の後に排他ロックを解放するとともに更新情報を更新する排他実行部28と、排他ロックを取得せずに第2タスクに含まれるクリティカルセクションの処理を実行させ、第2タスクに含まれるクリティカルセクションの処理の前後において更新情報が変化していないことを条件として当該クリティカルセクションの処理が成功したと判定する非排他実行部30とを備える。

(もっと読む)

データ処理システム及びデータ処理方法

【課題】スピンロックを取得しに行った順番に公平にスピンロックを取得できるデータ処理装置を提供する。

【解決手段】スピンロック変数の予約域をFIFO構成とし、スピンロックを取得しにいった順番をそこに記憶することにより、プロセッシングユニットがスピンロックを取得しに行った順番にスピンロックが渡るようにしたものである。予め決められたプロセッシングユニットの番号に基づいてラウンドロビン順にプロセッシングユニットにスピンロックが行き渡る構成とは異なる。

(もっと読む)

データ処理システム及びデータ処理方法

【課題】真にスピンロックを必要とするプロセッシングコアが効率的にスピンロックを取得することができるデータ処理方法を提供する。

【解決手段】スピンロックの要求はロック許可ビット(Pi)が許可を示すプロセッシングユニット(CPU0〜CPU3)の範囲で可能にされ、スピンロックの取得に失敗して取得を待つプロセッシングユニットは要求ビット(Rj)が要求にされている範囲で新たなスピンロックの取得を試みることができ、一旦スピンロックを取得したプロセッシングユニットは自らの許可ビットが非許可にされ、全ての要求ビットが非要求になったところでロック許可ビットを再度初期化するから、初期化によってスピンロックの取得が許可されたプロセッシングユニットは第1領域の初期化毎に重複することなくスピンロックの取得が可能になる。

(もっと読む)

排他制御装置

【課題】排他制御中であっても待ち時間を低減することが可能な排他制御装置を提供する。

【解決手段】一実施形態の排他制御装置10は、プロセス31が共有リソース20における複数のデータブロックからなるデータブロック群単位でロックを獲得しているときに、プロセス31による上記データブロック群に属するデータブロックへのアクセス内容を記録するアクセス内容記録手段12と、アクセス内容記録手段12によって記録されたアクセス内容とプロセス32による上記データブロック群に属するデータブロックへのアクセス内容との対比を行い、プロセス32によるこのアクセスがプロセス31による上記データブロックへのアクセスと抵触するか否かを判定するアクセス抵触判定手段13と、この判定結果に基づいてプロセス32によるこのアクセスを許可するか否かを通知するアクセス可否通知手段14とを備える。

(もっと読む)

71 - 80 / 395

[ Back to top ]