国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

181 - 190 / 951

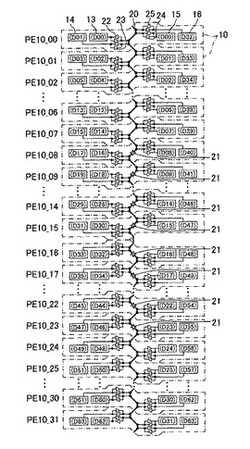

SIMD型マイクロプロセッサおよびSIMD型マイクロプロセッサのデータ転送方法

【課題】複数の画素データフォーマット変換を効率よく、かつ、回路規模の増大を抑えるように構成したSIMD型マイクロプロセッサおよびSIMD型マイクロプロセッサのデータ転送方法を提供する。

【解決手段】SIMD型マイクロプロセッサ1に、一列に並べられた複数のPE10を接続する転送バス20と、その転送バス20を分割するスイッチ21と、を備え、各PE10には、A1変換レジスタ13、A2変換レジスタ14と、B1変換レジスタ15、B2変換レジスタ16と、A1変換レジスタ13、A2変換レジスタ14の格納内容を転送バス20に出力する入出力回路22、23と、転送バス20上のデータをB1変換レジスタ15、B2変換レジスタ16に格納する入出力回路24、25と、入出力回路22、23、24、25及びスイッチ21をPEコントロール部30からのデータにより制御するデコーダ26と、を備える。

(もっと読む)

画像処理装置及びその制御方法

【課題】連携処理フローを実行する装置の機能に変更が生じた場合に、ユーザに煩雑な作業を求めることなく、当該連携処理フローの定義を変更して実行する画像処理装置及びその制御方法を提供する。

【解決手段】本発明の画像処理装置は、複数の外部装置との連携処理の手順が予め定義された連携処理フローに従った処理の実行開始前に、当該フローに含まれる複数の機能を、予め定義されている複数の外部装置のそれぞれが実行可能か否かを確認する。さらに、実行することを予め定義された外部装置が実行不可能であると確認された機能について、実行可能であると確認された他の外部装置が代わりに当該機能を実行するように、連携処理フローの定義を変更した後に、当該フローの実行を開始する。

(もっと読む)

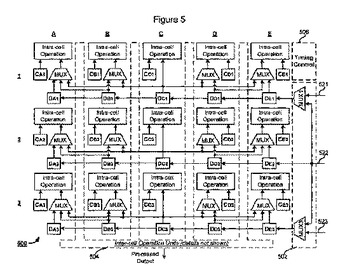

画素速度での画像処理のための方法および装置

本発明の実施形態は、処理演算が、画素の新しいラインまたはフレームに移行するときでも、メモリフェッチおよび画素出力の一定速度を維持するために、2−D画像処理において、改良されたタイミング制御を提供する。本発明に従って改良されたタイミング制御は、現在のライン上のエッジ画素ブロックの新しい列が、複製される、またはゼロに設定される間に、次のラインまたはフレームの第1の画素ブロック内の画素データの新しい列をプリフェッチすることによって、アイドルメモリ帯域幅を利用するため、着信画素速度と発信画素速度との間の1対1関係は、付加的なクロックサイクルまたはメモリ帯域幅を伴うことなく維持される。現在のライン上のエッジ画素ブロックが、処理されることに伴って、次のラインまたはフレームの第1の画素ブロック内のデータは、余剰クロックサイクルまたは余剰メモリ帯域幅を伴わずに、計算のための準備ができる。  (もっと読む)

(もっと読む)

イメージプロセッサ及びそれを含む電子装置及びイメージプロセッシング方法

【課題】多様な解像度のマルチメディアソースに対するイメージプロセッシング能力を向上させることができるイメージプロセッサを提供する。

【解決手段】イメージプロセッサ100は、ローテーションブロック120と、ラインバッファブロック130と、スケーリングブロック140と、を含む。前記ローテーションブロックは、ローテーション情報に基づいて生成されるアドレスに基づいて、再配列されたソースイメージのピクセルデータをメモリから受信して出力することができる。前記ラインバッファブロックは、前記ローテーションブロックから出力される再配列されたピクセルデータを臨時に保存することができる。前記スケーリングブロックは、前記ラインバッファブロックから出力される再配列されたピクセルデータを水平及び垂直方向にスケーリングすることができる。

(もっと読む)

イメージのハーフトーン化の方法

イメージのハーフトーン化の方法に関し、第1の数のビットで付与された少なくとも1つの入力明度が各ピクセルに割り当てられる、第1のピクセル配列の形でイメージを表現するソースファイル(18)が、電子的に処理され、第2の数のビットで付与された少なくとも1つの出力明度が第2のピクセル配列の各ピクセルに割り当てられる第2のピクセル配列の形で出力ファイル(20)を計算し、前記第2の数は第1の数未満であり、処理はグラフィックスプロセッシングユニット(GPU)(16)で行われる。  (もっと読む)

(もっと読む)

画像処理用半導体装置および画像処理装置

【課題】汎用的に用いることのできる画像処理ハードウェアで、CPUの介在なしに映像入力に同期して画像処理を行うことができる画像処理装置を提供する。

【解決手段】画像処理装置において、映像を取得する映像入力手段101で取得された画像データを記憶する記憶媒体102と、汎用的な処理を行うCPU106と、記憶媒体102に記憶された画像データを処理する画像処理手段103と、画像処理手段103の処理内容を決定する設定手段104と、画像処理手段103に対して設定および起動を行う順序を示す命令リスト105と、命令リスト105に基づいて、映像入力手段101からの画像データの入力に同期して、CPU106の介在なしに画像処理手段103に対して設定および起動を行う命令書き込み手段107とを備えた。

(もっと読む)

画像処理装置

【課題】 処理系を一様に並列化させた構成を用いた場合に、画像処理部の増加によるハードウエアの複雑化、メモリ管理情報の複数化によるソフト開発の複雑化という問題が生じてしまう。

【解決手段】 1ページの画像データを分割して、各画像処理部を並列動作させて、各分割された画像データからパケットデータを作成する画像形成装置において、各画像処理部のIDに応じてパケットIDにオフセットをつけ、並列動作させる画像処理部の数に応じてパケットIDを割振るパケットID作成手段とを持ち、並列処理させた場合においてもページ内でパケットIDが重複することなく、正常に割振る。

(もっと読む)

画像データ生成装置、画像形成装置およびプログラム

【課題】ページ独立でないページ記述言語で記述されたデータからラスタ画像を作成する処理を高速化する。

【解決手段】ページ記述言語で記述されたデータをページ単位に分割するページ分割部と、分割されたデータからラスタデータを作成するとともに、ラスタデータを作成する過程で印刷リソースを変更した場合にこれを印刷リソースの変更に関する情報として出力する複数のRIP40と、個々のRIP40にラスタデータを作成するページを割り当て、所定のRIP40から印刷リソースの変更に関する情報を受け取った場合に、所定のRIP40のメモリにおける印刷リソースの展開領域の内容を他のRIP40のメモリにおける印刷リソースの展開領域にコピーし、かつ印刷リソースの変更が行われたページ以降のページに関して、各RIP40に改めてラスタデータの作成を指示するRIP制御部50とを備える。

(もっと読む)

画像処理装置および画像処理方法

【課題】デバイスのスループットを低下させずに入力画像データを処理可能な画像処理装置および画像処理方法を提供すること。

【解決手段】入力画像データに対する画像処理の依存関係が所定方向に存在する当該画像処理を、複数のスレッドを起動させて並列的に処理可能な画像処理装置20であって、複数のスレッドを起動させて処理を並列的に実行可能なデバイス30と、デバイス30で画像処理された結果を記憶可能な中間バッファー32と、デバイス30に画像処理させる入力画像データのデータ量を制御するホストHと、を具備し、ホストHは、入力画像データを、画像処理の依存関係が存在する方向とは直交する方向に分割の境界部分Bが表れるように分割した分割画像データDを作成し、デバイス30には分割画像データDが供給され、さらにデバイス30で画像処理された処理結果のうち分割の境界部分Bに対応する処理結果を中間バッファー32に記憶させる。

(もっと読む)

信号処理装置

【課題】専用ハードウェアや高性能なSIMD型処理装置を用いることなく、処理の高速化を実現することができる信号処理装置を得ることを目的とする。

【解決手段】処理命令を発行する全体制御部1に対して、部分制御部21〜2N、データ転送部31〜3N及びデータパス部41〜4Nが並列に接続されており、全体制御部1が相互に異なる処理命令を部分制御部21〜2Nに発行し、あるいは、同一の処理命令を少なくとも1個以上の部分制御部2に発行することで、処理の並列化を実現する。

(もっと読む)

181 - 190 / 951

[ Back to top ]