国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

161 - 170 / 951

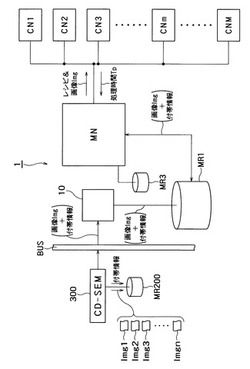

パターン評価システム、パターン評価方法および半導体装置の製造方法

【課題】評価対象パターンの画像を高速で処理するとともに、コンピュータ資源の効率を向上させる。

【解決手段】CD−SEM300により撮像された評価対象パターンの一連の画像Img1〜Imgnを一枚当たりTiの時間で取り込む画像取込装置10と、一連の画像Img1〜Imgnを一枚当たりTpの時間で処理して評価対象パターンの評価結果を出力するクラスタノードCN1〜CNMと、クラスタノードCN1〜CNMが接続されてこれらを制御するメインノードMNを備える分散コンピューティングシステム1において、時間TiおよびTpを測定して一連の画像Img1〜Imgnの取得時間とその処理時間とが一致するように、クラスタノードCN1〜CNm(m≦M)を推定して一連の画像処理に割り当てる。

(もっと読む)

情報処理装置、情報処理方法及びプログラム

【課題】描画処理能力の異なる2つのグラフィックスチップを、ユーザの利用目的に応じて安全かつより容易に切り替えること。

【解決手段】PC100は、描画処理能力とバッテリ持続時間のいずれを重視するかに応じて、内蔵グラフィックスチップ15と外部グラフィックスチップ20とを手動で切り替えるSPEEDモード及びSTAMINAモードのほか、HDMIまたはDVIの接続状況及びACアダプタ5の接続状況により両者を自動的に切り替えるAUTOモードを実行する。またPC100は、グラフィックスチップの切り替えにより支障が生じるアプリケーションが起動中である場合には、当該アプリケーション名を表示する。

(もっと読む)

多次元映像データを処理するためのシステム、データ構造、および方法

【課題】多次元映像データを処理するためのシステム、データ構造、および方法を提供する。

【解決手段】多次元データを処理するためのシステム、プロセッサ、データ構造、および方法が提供される。第1の多次元データ配列の部分配列内において異なる次元に格納されている複数のデータ要素が互いに相関していると特定または判断される。異なる次元に存在する複数の相関データ要素は、第2のデータ配列の単一次元内にて順序付けられた位置にマッピングされる。単一次元に順番に格納された複数のデータ要素は、少なくともすべての相関データ要素が取得されるまで、各演算サイクルでデータ配列から反復的に取得される。その後、これらの相関データ要素が処理される。

(もっと読む)

画像形成装置、印刷データ生成装置、プログラム、及び印刷データ生成方法

【課題】複数の演算部を用いてPDLデータから印刷データを生成する際の処理速度を向上させる。

【解決手段】本発明に係る画像形成装置は、PDLデータを受信する受信部と、複数の演算部を有し、前記複数の演算部のそれぞれがページ単位で処理を行うタスク又はバンド単位で処理を行うタスクを実行することにより、前記PDLデータに基づいて印刷データを生成する画像処理部と、前記PDLデータを解析して印刷ページ数を取得し、当該取得された印刷ページ数に応じて、前記ページ単位で処理を行うタスクと前記バンド単位で処理を行うタスクのそれぞれに割り当てる前記演算部の数を動的に設定する制御部と、前記生成された印刷データに基づき印刷媒体に画像を形成する印刷部と、を備える。

(もっと読む)

グラフィック処理装置の間のポリシーベースの切り換え

本開示の実施形態は、コンピュータシステムを設定して各グラフィック処理装置(GPU)の間で切り換えを行うようになっているシステムを提供する。1つの実施形態において、システムは、コンピュータシステムの第1のグラフィック処理装置(GPU)を使用してディスプレイを駆動する。次に、システムは、コンピュータシステムの1つ又はそれ以上の第2のGPUへの依存関係に関連する1つ又はそれ以上のイベントを検出する。最後に、このイベントに応答して、システムは、ディスプレイを駆動する信号源として、第1のGPUから第2のGPUへの切り換えを準備する。 (もっと読む)

データ処理装置、およびパラメータ設定方法

【課題】データ信号に対して順次に信号処理を行う信号処理回路が信号処理に用いるパラメータの設定に係るソフトウェアおよびハードウェアの設計、実装を容易とすることが可能なデータ処理装置、およびパラメータ設定方法を提供する。

【解決手段】識別情報を記憶しパラメータを記憶可能なレジスタを備え、モード制御信号に基づいてパラメータの記憶処理または信号処理を順次行う複数の信号処理部と、記憶部と、記憶部からパラメータ情報または処理データを選択的に読み出すデータ読み出し部と、信号処理部から出力されるデータ信号に対応するデータを記憶部に選択的に記録するデータ書き込み部と、モード制御信号を信号処理部へ出力する制御部とを備え、信号処理部は、パラメータの記憶処理を行う場合データ信号が識別情報と対応するときに、データ信号に含まれるパラメータをレジスタに記録するデータ処理装置が提供される。

(もっと読む)

画像処理装置、及び画像処理プログラム

【課題】要求倍率と実倍率との倍率誤差に応じてプロセッサ並列数を任意に選択し、少ない倍率誤差での画像の拡大・縮小処理を実現する。

【解決手段】画像処理装置10において、並列数選択部162は、処理対象の画像データと要求倍率を含む画像拡大指示を受付けると、SIMDプロセッサ50のプロセッサを異なる並列数にして処理対象画像データを並列演算処理させる場合の該並列数別の要求倍率と実倍率との倍率誤差を算出し、該倍率誤差が最も小さい並列数を選択する。SIMD制御部163は、処理対象の画像データを並列数選択部162により選択された並列数の数に分割して該並列数の数のプロセッサに上記要求倍率での拡大命令とともに与え、該拡大命令に基づく各プロセッサによる画像データ拡大処理結果を合成して拡大画像データを生成させる。

(もっと読む)

画像処理装置

【課題】複数のプロセッサ要素を1次元に結合してなる分散メモリ型プロセッサアレイを備えた画像処理装置により、1行の画素数がプロセッサ要素数より多い画像を処理する場合の効率向上を図る。

【解決手段】画像処理プロセッサ100は、複数個のプロセッサ要素をリング状に1次元に結合してなる分散メモリ型プロセッサアレイ120を備え、処理対象の画像の1行の画素数がプロセッサ要素数より大きいときに、該画像を折り畳んでプロセッサ要素のローカルメモリに格納する。各プロセッサ要素のメモリアクセス制御部は、ローカルメモリアクセスにより画像の所定の行に含まれる画素に対する読出要求があった際に、ローカルメモリに格納された、上記所定の行の全ての画素をローカルメモリから読み出すことが可能である。なお、ローカルメモリアクセスは、プロセッサアレイ120内部に生じるメモリアクセスである。

(もっと読む)

パターン認識プロセッサのための多重階層ルーティングマトリクス

パターン認識プロセッサのための多重階層ルーティングマトリクスが提供される。一つのこのようなルーティングマトリクスは、マトリクスのレベルにおけるまたはレベル間における一つ以上のプログラマブル及び/または非プログラマブル接続を含んでもよい。接続は、フィーチャセル、グループ、行、ブロック、または、パターン認識プロセッサのコンポーネントの任意の他の配列にルーティングラインを結合してもよい。 (もっと読む)

データ転送制御装置、データ転送システム、及びデータ処理システム

【課題】記憶資源を効率的に使用する。

【解決手段】各々が転送されたデータを転送された順に処理する画像処理部(第1〜第4画像処理部11〜14)の各々に対応させて設けられデータを一時的に記憶するための複数の中間バッファ32と、各々が画像処理部の各々に対応するように定められた互いに重複しない複数の記憶領域を備えた単一の記憶装置50の記憶領域から予め定められた順にデータを読み出し上記対応させて設けられた中間バッファ32に書き込む複数のDMA制御部33と、各々が画像処理部の各々に対応させて設けられ対応する画像処理部からの要求に応じて該画像処理部に対応する中間バッファ32に書き込まれたデータを書き込まれた順に読み出して対応する画像処理部に転送する複数の画像処理部I/F31と、複数のDMA制御部33の各々に対して排他的に記憶装置50からデータを読み出す権利を付与して排他制御を行う排他制御部40とを設ける。

(もっと読む)

161 - 170 / 951

[ Back to top ]