国際特許分類[G06T1/60]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | メモリ管理 (517)

国際特許分類[G06T1/60]に分類される特許

201 - 210 / 517

画像処理装置

【課題】 従来よりも装置の低コスト化及び小型化を可能とする画像処理装置を提供する。

【解決手段】 撮像範囲が一部重複する複数のカメラ1,2,3により得られた画像データを記憶する合成メモリ19と、画像データを合成メモリ19に記憶させる処理を実行する記憶処理実行部と、を備える。前記記憶処理実行部は、カメラ1,2,3により得られた画像データのうち、重複する画像データについては、何れか1つのカメラにより得られた画像データのみを合成メモリ19に記憶させる。これにより、複数のカメラ1,2,3により得られた画像データを、撮像対象物21の画像を表す一連の画像データとして合成メモリ19に記憶させる。

(もっと読む)

メモリ制御装置、メモリ制御装置の制御方法、プログラム及び記憶媒体

【課題】メモリアクセス効率に優れたメモリ制御技術を提供すること。

【解決手段】メモリ制御装置は、バスマスタから入力された読出しの対象となるデータのアドレス情報と、予め設定されているメモリのデータ領域のアドレスを定義する複数のディスクリプタ情報との比較を行う比較部と、比較に基づき、読出しの対象となるデータの格納領域にアクセスするためのディスクリプタ情報を取得する取得部と、取得されたディスクリプタ情報に基づき、メモリにアクセスし、メモリの格納領域からデータを読出す第1の読出し部と、取得されたディスクリプタ情報に基づき、次のアクセスに対応したデータを事前にメモリからデータを読出すための次ディスクリプタ情報を生成する生成部と、生成された次ディスクリプタ情報に基づき、メモリにアクセスし、メモリの格納領域からデータを読出す第2の読出し部と、第2の読出し部により読出されたデータを格納する格納部とを備える。

(もっと読む)

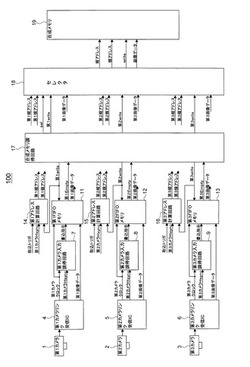

画像処理装置、印刷装置、制御プログラム、記録媒体

【課題】コストアップを招くことなくメモリに対する初期化処理を高速で行える画像処理装置を提供する。

【解決手段】複合機10の統括制御装置12は、データ変換装置21とDMAC22と第1圧縮伸張装置23と第2圧縮伸張装置24と回転装置25と制御部15とメモリユニット16とを有している。DMAC22はメモリユニット16に画像データを転送する装置である。データ変換装置21、第1圧縮伸張装置23、第2圧縮伸張装置24、回転装置25は、画像データに画像処理を施し、この画像処理の施した画像データをメモリユニット16に書き込むものである。制御部15は、データ変換装置21とDMAC22と第1圧縮伸張装置23と第2圧縮伸張装置24と回転装置25とのなかから2以上の装置を選択し、メモリユニット16に対する初期化処理を前記選択した各装置に行わせる。

(もっと読む)

画像処理装置

【課題】 矩形分割した頁の画像データを変倍処理して外部へ転送する場合の画質の劣化を低コストで防止できるようにする。

【解決手段】 スキャナ画像処理部115aは、矩形分割した頁の画像データを変倍処理部207および画像I/F部117を経由して外部のコントローラ120へ転送する際に、変倍処理部207からの画像データの主走査方向のサイズが画像I/F部117用のバウンダリサイズに合わないとき、そのバウンダリサイズに合う画素までを転送し、残りの画素については切り捨てるように制御を行う。

(もっと読む)

情報処理方法及び装置、プログラム、記憶媒体

【課題】 計算負荷は増加させずに、回路規模やメモリ等の必要なリソースを低減する。

【解決手段】 複数次元配列の入力情報を入力し、前記入力情報の各要素位置に対応する累積情報値を計算し、前記累積情報値を所定ビットのサイズを持つバッファに保持する。その際に、計算された累積情報値が前記所定ビットのサイズに対してオーバーフローを生じた場合、当該計算された累積情報値の前記ビットサイズ以下の部分を、前記累積情報値として保持する。

(もっと読む)

メモリ制御装置

【課題】 DRAM等を利用して動画の圧縮符号化データの復号化処理を行う場合に、プリチャージサイクルの発生頻度を抑える。

【解決手段】 ライトアクセス制御部52およびリードアクセス制御部54は、アドレス変換処理を行う機能を有する。アドレス変換処理では、アクセス要求により指定された画像データの論理アドレスを画像メモリ11における当該画像データの記憶エリアを特定するメモリアドレスに変換する際、画面を所定の画素サイズの複数のブロックに分割した各ブロックについて、同一ブロック内の各画素の画像データの各論理アドレスを、ロウアドレスが同一であり、かつ、カラムアドレスが異なった複数のメモリアドレスに各々変換する変換ルールに従い、論理アドレスのメモリアドレスへの変換を行う。

(もっと読む)

データ処理装置

【課題】搭載した複数のメモリを複数のデータ処理部で効率よく利用することができ、メモリの搭載数を削減することができるデータ処理装置を提供する。

【解決手段】選択部11は内部に複数のセレクタを有しており、複数のSRAM41〜47から1つを選択してズーム処理部6、出力γ処理部7、中間階調処理部8及びSDRAM制御部9等のデータ処理部からの書き込み要求又は読み出し要求を与えると共に、SRAM41〜47を複数のデータ処理部の1つに与える。CPU10は、選択部11によるSRAM41〜47の選択を制御し、複数のデータ処理部に対して一又は複数のSRAM41〜47の割り当てを行う。

(もっと読む)

読取装置

【課題】原稿の読み取りが可能な読取装置を接続することによって原稿の両面の読み取りが可能となる読取装置を提供する。

【解決手段】ピックアップローラ21によってスキャナ1の内部に取り込まれた原稿は搬送経路Sに沿ってプラテンガラス30まで搬送され、原稿読取部によって下面画像が読み取られる。排出ローラ25a,25bによってスキャナ1の外部へ排出された原稿は第2の読取装置5の内部に取り込まれ、搬送ローラ52a,52bによってプラテンガラス60まで搬送され、上面読取部によって上面画像が読み取られる。制御部は、原稿読取部が取得した画像データ又は上面読取部が取得した画像データをページメモリに蓄積する際にページメモリの残容量を検出し、所定量以上無い場合、原稿読取部による原稿の読み取り又は下面読取部による原稿の読み取りを一時停止させる。

(もっと読む)

画像形成装置

【課題】必要なメモリ容量の増大を抑制するとともに、比較的簡単且つ効率よく、印刷データを高速にビットマップ展開してプリントエンジンコントローラへ供給する。

【解決手段】圧縮1チャンネル伸長2チャンネルのハードウェア圧縮伸長プロセッサ14を用いるとともに、圧縮・伸長プロセッサ14に対する伸長及び圧縮の開始制御をスレッドTh0〜Th2及びThPで実行する。ビットマップデータ領域を3バンド分確保し、並列実行されるスレッドTh0〜Th2で共通の関数を用い、3バンド分について圧縮及び伸長のそれぞれをほぼ連続的に行うことにより、印刷データを高速にビットマップ展開する。スレッドTh0では、中間コードブロックLijの作成及びラスタライズRijの処理をバンド順次ブロック順次に行う。スレッドThPでは、このページデータをバンド順次に、伸長部143を介し、伸長させエンジンコントローラ17へ転送させる。

(もっと読む)

情報再生装置および情報再生方法

【課題】パフォーマンスの高い情報再生装置および情報再生方法を提供する。

【解決手段】メモリB120と、デコーダB150と、メモリB120とデコーダB150との間に配置され、メモリB120から供給されたデータを、連続に一旦保存してからデコーダB150に出力する中間メモリB140と、メモリB120の出力をデコーダB150と中間メモリB140とのいずれかに切替える切替手段B130と、メモリS120に保存されたデータの配置情報を管理するメモリ管理手段B180と、メモリS120に保存されたデータが物理的に分割された記憶領域に配置されているか否かを判断する判断手段B181と、判断手段B181によってデータが物理的に分割された記憶領域に配置されていると判断された場合に、メモリS120からの出力データが中間メモリB140を経由してデコーダB150に入力されるように切替手段B130を切替える切替制御手段B191と、を備える。

(もっと読む)

201 - 210 / 517

[ Back to top ]