国際特許分類[G11C11/412]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 電気的素子を用いるもの (5,515) | 半導体装置を用いるもの (5,114) | トランジスタを用いるもの (5,110) | 正帰還によるセル,すなわちリフレッシングまたは電荷再生を必要としないセルを形成するもの,例.双安定マルチバイブレータまたはシュミットトリガ (1,516) | 電界効果トランジスタのみを用いるもの (157)

国際特許分類[G11C11/412]に分類される特許

1 - 10 / 157

半導体記憶装置

【課題】1つの実施形態は、例えば、電源オフ時における消費電力を低減することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルは、第1の駆動トランジスタと第1の負荷トランジスタと第1の読み出し転送トランジスタと第1の書き込み転送トランジスタと第2の駆動トランジスタと第2の負荷トランジスタと第2の読み出し転送トランジスタと第2の書き込み転送トランジスタと1以上の抵抗変化素子とを有する。1以上の抵抗変化素子は、両端に印加されるバイアスの方向に依存して抵抗が変化する。1以上の抵抗変化素子は、第1の記憶ノード及び第1の書き込み転送トランジスタの間と第2の記憶ノード及び第2の書き込み転送トランジスタの間との少なくとも一方に配される。

(もっと読む)

メモリにおけるピーク電力管理のためのメカニズム

【課題】メモリにおけるピーク消費電力管理のためのメカニズムを提供する。

【解決手段】サブ・アレイ・ブロックを含むメモリ・ストレージ・アレイにおけるピーク電力を管理するためのメカニズムが、サブ・アレイ・ブロックの各々に対するワードライン信号の起動を互い違いにすることにより、読み出し動作及び書き込み動作と関連したピーク電流を削減することができる。具体的には、1つのサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの書き込みワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、各々のサブ・アレイ・ブロックに対してワードライン信号を生成することができる。さらに、ワードライン・ユニットは、所与のサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの読み出しワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、ワードライン信号を生成することができる。

(もっと読む)

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

メモリ装置

【課題】高速にデータを書き込むことができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、第1及び第2のpチャネルトランジスタと、第1のpチャネルトランジスタ及び第2のpチャネルトランジスタのバックゲートに第2のバックゲート信号を出力するバックゲート信号生成回路(501)とを有し、バックゲート信号生成回路は、第1の遅延回路(DL1)と第2の遅延回路(DL2)とを有し、第1の遅延回路は、第3のpチャネルトランジスタ及び第3のnチャネルトランジスタを含む第1のインバータ(504)を有し、第3のpチャネルトランジスタは、第3のnチャネルトランジスタよりゲート幅が広く、第2の遅延回路は、第4のpチャネルトランジスタ及び第4のnチャネルトランジスタを含む第2のインバータ(505)を有し、第4のpチャネルトランジスタは、第4のnチャネルトランジスタよりゲート幅が狭い。

(もっと読む)

不発揮性SRAM及びその操作方法

【課題】SRAMの読み書き機能と不揮発性メモリの不揮発記憶特性をあわせ持つ不発揮性SRAMセルを提供する。

【解決手段】二つの出力ノードを設けるラッチと、前記二つの出力ノードのうちの一つとビットラインペアのうちの一つとの間に接続されるアクセストランジスタからなるSRAMセルにおいて、前記二つの出力ノードのうちの一つと電圧ラインとの間に不揮発性メモリ素子を接続することにより、不揮発性SRAMセルを構成する。

(もっと読む)

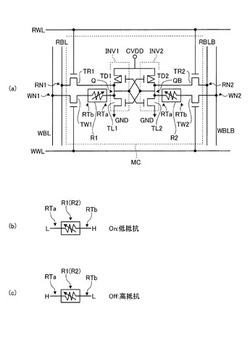

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

1 - 10 / 157

[ Back to top ]