国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

971 - 980 / 2,471

半導体装置及び半導体装置の製造方法

【課題】酸素ガスを主に含有したガスでエッチングを行う必要がある金属材料を用いてピラー型電極を形成する際に、ピラー型電極のアスペクト比が高くなると製造が困難になるという課題があった。

【解決手段】層間絶縁膜上に第1〜第6の絶縁膜を積層した後、第1のフォトレジスト膜を形成する工程と、前記第1のフォトレジスト膜をマスクとして第1の溝部を形成する工程と、前記第1の溝部を充填するように電極材料を堆積する工程と、前記第4の絶縁膜上に第7〜第9の絶縁膜を形成した後、第2のフォトレジスト膜を形成する工程と、前記第2のフォトレジスト膜をマスクとして第2の溝部を形成すると共に、前記電極材料をピラー型に残存させる工程と、前記第8、前記第7、前記第4および前記第2の絶縁膜を除去して、前記電極材料からなるピラー型電極を露出する工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

マルチプレクサー及びこれの製造方法

【課題】スイッチング素子を具備するマルチプレクサー及びこれの製造方法をを提供すること。

【解決手段】基板上に配置されて第1方向に沿って延伸され、互いに電気的に絶縁され、少なくとも1つの凹みを具備して少なくとも2つ以上のデータ配線ピースに分離される複数のデータ配線を具備する信号ライン、信号ラインの上部から第2方向に沿って延伸され、データ配線と電気的に絶縁される複数の印加配線を具備するアドレスライン及び凹みに位置し、印加配線と電気的に接続されて印加配線に印加されたコーディング信号に従ってデータ配線を経由するデータ信号を選択的に伝送する複数のスイッチング素子を含む。コーディング信号が印加される印加配線の組合せであるアドレスラインの2進コードによってデータ配線のうちの1つを選択する。よって、マルチプレクサーの動作安定性及び工程効率を改善させる。

(もっと読む)

半導体装置

【課題】デザインルールに従いつつ、セル面積の縮小を図ることができる、半導体装置を提供する。

【解決手段】FeRAM1では、N型のドレイン領域6およびソース領域7が互いに間隔を空けて形成されている。ワードラインWL1,WL2,・・・は、ドレイン領域6とソース領域7との間の領域に対向している。ドレイン領域6の上方には、強誘電体キャパシタ12が形成されている。ドレイン領域6と強誘電体キャパシタ12の下部電極13とは、容量コンタクトプラグ18を介して接続されている。容量コンタクトプラグ18は、平面視で下部電極13の中心に対してワードラインWL1,WL2,・・・側と反対側にずれた位置に設けられている。これにより、ワードラインWL1,WL2,・・・と容量コンタクトプラグ18との間の距離は、平面視におけるゲート電極9と下部電極13の中心との間の距離よりも大きくなっている。

(もっと読む)

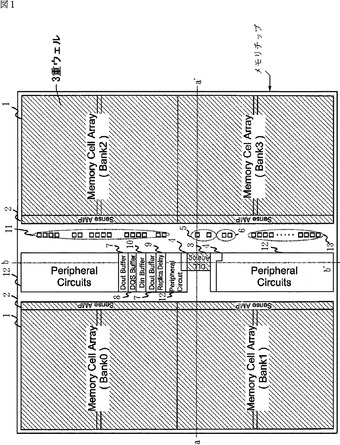

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】オフ状態でのリーク電流を抑制したMOSトランジスタを有する回路領域と、オン状態でのドレイン電流を大きいMOSトランジスタを有する回路領域と、を備えた半導体装置を提供する。

【解決手段】第1のMOSトランジスタは、第1の不純物領域として、半導体基板内に設けられた第1の領域及び第1の領域の上方に突出するように設けられた第2の領域からなる第1のソース/ドレイン領域を有する。第2のMOSトランジスタは、半導体基板内に設けられた第2の不純物領域と、第2の不純物領域に接触して半導体基板の上方に突出する第3の不純物領域と、第3の不純物領域上に第4の不純物領域とを有する第2のソース/ドレイン領域を有する。第3の不純物領域は、第4の不純物領域よりも不純物濃度を低くし、第1の不純物領域は、第2の不純物領域よりも不純物濃度を低くする。

(もっと読む)

半導体装置及びその製造方法

【課題】十分な保持強度を備えることでキャパシタ下部電極の倒壊を防止し、製造が容易なサポート膜を備えた半導体装置を提供する。

【解決手段】設計ルールFの数値によってサイズが規定される6F2型のメモリセルを備えた半導体装置であって、前記メモリセルに含まれるキャパシタの下部電極がサポート膜で保持されており、該サポート膜は第1の方向に直線状に延在する第1のサポートパターン(14x)と、前記第1の方向と直交する第2の方向に直線状に延在する第2のサポートパターン(14y)との組合せのパターンで形成され、前記第1及び第2のサポートパターンの間隔は共に1.5F以上であり、前記第1又は第2のサポートパターンのいずれか一方の間隔は、前記第1又は第2のサポートパターンの他方の間隔よりも大きくなるように配置する。

(もっと読む)

半導体素子及びそのセルブロック配置方法

【課題】長さの制限がなく、メモリセルブロックを密集配列させて高いパッキング密度を具現することができる半導体素子及びそのセルブロック配置方法を提供する。

【解決手段】セルアレイと、前記セルアレイの横及び縦方向に配置されたデコーダとを有する複数個の「L」字形状のセルブロックを有し、前記複数個の「L」字形状のセルブロックは、前記横及び縦方向と交差する斜線方向に指向配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接する活性領域間が狭くなった場合においても、コンタクトプラグと拡散層とのコンタクト抵抗を低く抑えることが可能な半導体装置及びその製造方法を提供する。

【解決手段】X方向に延在する活性領域102内に設けられたゲートトレンチ103gt1、103gt2及びダミーゲートトレンチ103dgtと、活性領域102を横切るY方向に延在し、各トレンチ103gt1、103gt2、103dgt内にそれぞれ少なくとも一部が埋め込まれたゲート電極104g1、104g2及びダミーゲート電極104dgとを有し、ゲート電極104g1とその両側に設けられた拡散層105a1,105a2とからなるトランジスタ109と、ゲート電極104g2とその両側に設けられた拡散層105b1,105b2とからなるトランジスタ110は、拡散層105a2と拡散層105b1との間に配置されたダミーゲート電極104dgにより絶縁分離される。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を開示する。

【解決手段】本発明は、コア/周辺回路領域でトランジスタの接合領域とメタルラインを、ビットラインを利用して連結せずメタルプラグを利用して連結することにより、コア/周辺回路領域に形成されるビットライン等もセル領域と同様に均一な形態のパターンを有することができるようにする。これを介し、本発明ではコア/周辺回路領域におけるビットラインパターニングの不良を防止し、ビットライン形成時にSPT(Spacer Pattern Technology)を適用することができる。

(もっと読む)

971 - 980 / 2,471

[ Back to top ]