国際特許分類[H01L21/8249]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | バイポーラ技術と電界効果技術の組み合わせ (497) | バイポーラ技術とMOS技術 (254)

国際特許分類[H01L21/8249]に分類される特許

1 - 10 / 254

半導体装置の製造方法

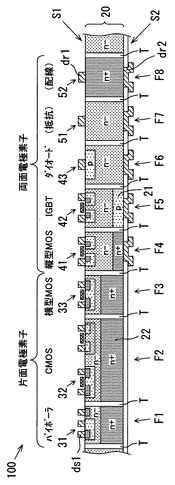

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体デバイス

【課題】高い電流増幅率と高いアーリー電圧を両立することができ、CMOSトランジスタとともに製造する場合でもより少ない製造工程により製造することができる半導体デバイスを提供する。

【解決手段】基板P11の表面に形成された第1導電型のベースP14と、ベースの表面に形成された第2導電型のエミッタN23と、ベースの表面においてエミッタと離間して配置され、エミッタから第1の種類のキャリアを受け取るとともに、その第1の種類のキャリアをベースへ注入する、第2導電型のドープ領域N24と、ベースを挟んで、エミッタおよびドープ領域の反対側に形成された、第2導電型のコレクタN15とを備える。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

1 - 10 / 254

[ Back to top ]