国際特許分類[H01L23/32]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の完全装置を支持する支持体,すなわち分離できる定着物 (458)

国際特許分類[H01L23/32]に分類される特許

101 - 110 / 458

ソケット、該ソケットと電子装置との接続構造、および半導体装置

【課題】構造が簡単で、薄型化・軽量化、および端子間の狭ピッチ化を可能とする半導体装置を提供する。

【解決手段】この半導体装置1は、半導体チップ5が搭載されると共に、外部接続用のパッド31が一面側に形成された半導体パッケージ3と、半導体パッケージ3のパッド形成面30aに対向する面に、パッド31と電気的な接続を行うためのコンタクト21が設けられたソケット2と、を備え、ソケット2を介して半導体パッケージ3と実装基板4とが接続されて形成される半導体装置であって、半導体パッケージ3をパッド形成面30aに平行な方向に押動する押動手段6を備え、押動手段6によって、半導体パッケージ3が、ソケット2に対して所定の一方向に押動されて、パッド31とコンタクト21とが当接して、半導体パッケージ3とソケッ2トとが電気的に接続される。

(もっと読む)

キャパシタ内蔵インターポーザモジュール

【課題】 キャパシタ内蔵インターポーザモジュールに関し、接続信頼性を高めるとともに、内蔵するキャパシタを大容量化し、さらに、低コスト化する。

【解決手段】 第1の電極と第2の電極とを備え、モールド被覆固定されている半導体集積回路素子を有し、弁金属材料と、前記弁金属材料の一部の表面に形成された陽極酸化皮膜と、前記陽極酸化皮膜の上に形成された陰極と、前記陰極に電気的に接触する導電性材料と、前記導電性材料に電気的に接続する下部電極パッドとを有し、前記弁金属材料が前記第1の電極と電気的に接続され、前記陰極が前記導電性材料を介して前記第2の電極と電気的に接続され、前記弁金属材料と前記陰極との間に前記陽極酸化皮膜を挟んで構成されるキャパシタを少なくとも1組有し、前記パッケージ基板を前記下部電極パッドと電気的に接続する。

(もっと読む)

半導体装置、半導体パッケージ、インタポーザ、半導体装置の製造方法、及びインタポーザの製造方法

【課題】配線基板の外部接続端子間におけるインタポーザの表面を被膜するソルダーレジスト層におけるクラックの発生、及びこれに伴う配線の断線を抑制する。

【解決手段】半導体パッケージ200は、配線基板10に実装されている。アンダーフィル樹脂層100は、半導体パッケージ200と配線基板10の間を封止している。半導体パッケージ200を構成するインタポーザ210の、半導体チップ250を搭載しない面には外部接続端子240、配線230、及びソルダーレジスト層220が形成されている。隣り合う2つの外部接続端子240の間を通る配線230と隣り合う2つの外部接続端子240の中心を結ぶ直線が交差する部分において、配線230はソルダーレジスト層220によって被覆されていない。

(もっと読む)

導電接続シート、端子間の接続方法、接続端子の形成方法、半導体装置および電子機器

【課題】溶融状態の金属材料を選択的に端子上に凝集させることができないことに起因する、隣接する端子間におけるリーク電流の発生が低減された導電接続シート、かかる導電接続シートを用いた端子間の接続方法、接続端子の形成方法、信頼性の高い半導体装置、および、電子機器を提供すること。

【解決手段】本発明の導電接続シート1は、樹脂組成物層11、13と金属層12とを備える積層体により構成されるものであり、樹脂組成物層11、13中において、フラックス機能を有する化合物は、金属層12側に遍在していることを特徴とする。

(もっと読む)

導電接続シート、端子間の接続方法、接続端子の形成方法、半導体装置および電子機器

【課題】溶融状態の金属材料を選択的に端子上に凝集させることができないことに起因する、隣接する端子間におけるリーク電流の発生が低減された導電接続シート、かかる導電接続シートを用いた端子間の接続方法、接続端子の形成方法、信頼性の高い半導体装置、および、電子機器を提供すること。

【解決手段】本発明の導電接続シート1は、樹脂組成物層11、13と、この樹脂組成物層1、13に接合される金属層12とを備える積層体により構成されるものであり、第1の樹脂組成物層11は、その平均厚さが、第2の樹脂組成物層13の平均厚さより薄いことを特徴とする。

(もっと読む)

電子部品の実装接続構造

【課題】複数の半導体素子を有する半導体装置と樹脂基板をバンプ接続する際、半導体素子のバンプに対する熱応力の作用によって接続部にクラックが生じて、機器の長期信頼性が低くなること。

【解決手段】複数の半導体素子を搭載されるインターポーザー配線基板の裏面に複数のランドとバンプを備える半導体装置と、複数のランドが配列された樹脂基板とを接続する電子部品の実装構造であって、前記インターポーザー配線基板の前記半導体素子と重なる位置にあるバンプの中で、半導体装置の中心から最も離れた位置に配列された位置及びその周辺にあるバンプと、前記バンプと隣接するバンプとが並列接続されていることを特徴とすることにより、応力集中が最も発生する位置のバンプが、冗長接続となり、一つのバンプが破断しても他方のバンプの接続が保たれ、故障を起こす期間を延伸することができる。

(もっと読む)

被測定デバイス搭載ボード、及びデバイスインタフェース部

【課題】複数種類のパフォーマンスボードと接続できる接続ユニットを提供する。

【解決手段】ICソケットが載置されたパフォーマンスボードと、ICソケットに保持される電子デバイスを試験する試験装置とを電気的に接続する接続ユニットであって、パフォーマンスボードと対向して設けられる保持基板と、保持基板上における位置が変更可能に保持基板上に設けられ、パフォーマンスボードが備えるパフォーマンスボード側コネクタと接続されるべき接続ユニット側コネクタとを備えることを特徴とする接続ユニットを提供する。

(もっと読む)

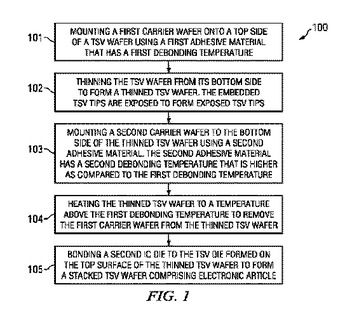

ICダイ又はウエハをTSVウエハに接合するためのデュアルキャリア

シリコン貫通ビア(TSV)ウエハを用いてスタックされた電子的部品を形成する方法が、第1ディボンデング温度を有する第1接着性材料(206)を用いてTSVウエハ(202)の上側に第1キャリアウエハ(205)を搭載することを含む。TSVウエハは、その下側から薄くされて薄くされたTSVウエハ(202’)を形成する。第1ディボンデング温度より高い第2ディボンデング温度を有する第2接着性材料(207)を用いて、TSVウエハ(202’)の下側に第2キャリアウエハ(215)が搭載される。薄くされたTSVウエハ(202’)はそれから第1キャリアウエハ(205)を取り除くため、前記第1ディボンデング温度を超える温度まで加熱される。スタックされた電子的部品を形成するため、少なくとも1つの個片化されたICダイが、薄くされたTSVウエハの上面上に形成されたTSVダイに結合される。

(もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積を小さくしたMEMS素子などの電子デバイスを組み込んだ半導体装置およびその製造方法を提供する。

【解決手段】MEMS素子本体11の両面に機能部材が露出するようにして面積を小さくしたMEMS素子10をフリップチップ実装するに際し、MEMS素子本体11に第1実装用基板13を接合し、その第1実装用基板13ごとボンディングツールで吸着して、回路基板20へフリップチップ実装する。また、MEMS素子本体11の上下面に位置する金ボール12、27によって第1空間部S1、第2空間部S2を形成するとともに、金ボール12、27を対向して配置することで、接合時におけるMEMS素子本体11の破損を防止する。

(もっと読む)

電子装置及びその製造方法

【課題】配線基板の変形を抑制し、信頼性の高い電子装置を提供する。

【解決手段】パッケージ基板11の上に配置されるスティフナ12に、その開口部12aを囲むように、パッケージ基板11側と反対側に突出する突部12bを設ける。このようなスティフナ12を配置したパッケージ基板11の上に、半導体チップ13を配置する。電子装置内に、突部12bを設けたスティフナ12を用いることにより、パッケージ基板11の変形を抑制する。

(もっと読む)

101 - 110 / 458

[ Back to top ]