国際特許分類[H01L29/47]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | 構成材料に特徴のあるもの (3,446) | ショットキー障壁電極 (987)

国際特許分類[H01L29/47]に分類される特許

101 - 110 / 987

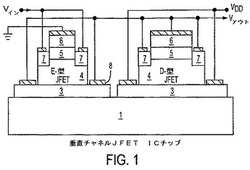

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置

【課題】リーク電流を抑制した半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、第1導電型の半導体層、複数のトレンチ、絶縁層、導電層、第1半導体拡散層、及びアノード電極を有する。半導体層は、半導体基板上に形成され第1の不純物濃度よりも小さい第2の不純物濃度を有する。複数のトレンチは、半導体層の上面から下方に延びるように半導体層中に形成されている。導電層は、絶縁層を介してトレンチを埋めるように形成され且つ半導体層の上面から第1の位置まで下方に延びる。第1半導体拡散層は、複数のトレンチの間に位置する半導体層の上面から第2の位置に達し且つ第2の不純物濃度より小さい第3の不純物濃度を有する。アノード電極は、第1半導体拡散層とショットキー接合されている。半導体層の上面から第2の位置までの長さは、半導体層の上面から第1の位置までの長さの1/2以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗が低く、高いアバランシェ耐量を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、第1半導体層と、複数のベース領域と、ソース領域と、トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、トレンチ内において、ゲート電極の下にフィールドプレート絶縁膜を介して設けられたフィールドプレート電極と、第1主電極と、第2主電極と、を備える。フィールドプレート絶縁膜の一部の厚さは、ゲート絶縁膜の厚さよりも厚く、一対のトレンチ内に設けられたフィールドプレート絶縁膜の一部どうしの間の第1半導体層の幅は、一対のトレンチ内に設けられたゲート絶縁膜どうしの間のベース領域の幅よりも狭く、第1半導体層と、フィールドプレート絶縁膜の一部と、の界面の直上には、ソース領域が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】素子周辺部での耐圧を高くしながら周辺領域の面積を小さくすることが可能な構造を有する半導体装置を製造可能であり、かつ、CMP工程に起因して素子周辺部での耐圧が低下してしまうことのない半導体装置を提供する。

【解決手段】n−型ドリフト層114と、n−型ドリフト層114における活性領域R1に形成したp型半導体材料からなる複数の柱状埋込層118と、周辺耐圧領域R2に形成したリング状の第2トレンチ122、第2トレンチ122の内面に形成した絶縁膜124及び第2トレンチ122の内部に絶縁膜124を介して形成した導電性材料層126を有し、逆バイアス時には導電性材料層126及び柱状埋込層118に挟まれた部分のn−型ドリフト層114を空乏化させる周辺耐圧構造120と、周辺領域R3に形成したp型半導体材料からなる1又は2以上の第2柱状埋込層130とを備える半導体装置100。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の実施形態は、トレンチ構造におけるゲート・ソース間容量を低減できる半導体装置およびその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面側に設けられた第1主電極と、前記半導体層の第2の主面側に設けられた第2主電極と、前記半導体層の前記第1の主面側から前記第2の主面の方向に形成されたトレンチの内部に設けられ、前記第1主電極と前記第2主電極との間に流れる電流を制御する2つの第1制御電極と、前記トレンチの内部において、前記2つの第1制御電極と、前記第2の主面側の底面と、の間に設けられた第2制御電極と、を備える。前記2つの第1制御電極は、前記第1の主面に平行な方向に離間して設けられ、それぞれ第1の絶縁膜を介して前記トレンチの内面に対向し、前記第2制御電極は、第2の絶縁膜を介して前記トレンチの内面と対向する。

(もっと読む)

半導体装置

【課題】順方向電圧の低減及びリーク電流の低減を図る半導体装置を提供する。

【解決手段】本実施形態に係る半導体装置は、第1導電形の第1半導体層と、第2導電形の領域であって、前記第1半導体層の第1主面の側に離間して設けられた複数の第2半導体領域と、第2導電形の領域であって、前記第1半導体層の前記第1主面の側に前記複数の第2半導体領域を囲むように設けられた第3半導体領域と、前記第1半導体層及び前記複数の第2半導体領域の上に設けられた第1電極と、を備える。前記第1半導体層は、第1部分と、前記第1部分よりも比抵抗が低く、前記第1部分と前記第1主面とのあいだであって、前記複数の第2半導体領域のあいだ、及び前記第3半導体領域の外側に設けられた第2部分と、を有する。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、サージ耐量が高く、順方向の電流密度を向上させることが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、第1導電形の半導体層と、前記半導体層の第1の主面に選択的に設けられた第2導電形の第1の領域と、前記第1の領域に接続して前記第1の主面に選択的に設けられた第2導電形の第2の領域と、を備える。そして、前記半導体層と前記第1の領域とに接して設けられた第1の電極と、前記第2の領域に接して設けられた第2の電極と、前記半導体層の前記第1の主面とは反対の第2の主面側に電気的に接続された第3の電極とを備える。

(もっと読む)

ショットキーバリアダイオード

【課題】ジャンクションバリアショットキー構造をもつダイオードにおいて、ショットキー接合部の逆サージ耐量を改善することが可能なショットキーバリアダイオードを提供する。

【解決手段】ガードリング層15に隣接した第二半導体層161と、この第二半導体層161に隣接する第二半導体層162との間に跨るように、基板11の中心領域Acにおいて第三絶縁層23が形成されている。即ち、第二半導体層161と第二半導体層162との間で、基板11の一面(一方の主面)11aに露呈された第一半導体層13を覆うように第三絶縁層23が形成される。これによって、第三絶縁層23は、第二半導体層161と第二半導体層162との間で基板11の一面11aに露呈された第一半導体層13と、金属層14との間を電気的に絶縁する。

(もっと読む)

101 - 110 / 987

[ Back to top ]