国際特許分類[H01P1/36]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 導波管;導波管型の共振器,線路または他の装置 (6,167) | 補助装置 (2,869) | 非可逆性伝送装置 (330) | アイソレータ (192)

国際特許分類[H01P1/36]の下位に属する分類

共鳴吸収形アイソレータ (10)

電界偏位形アイソレータ (1)

ファラデー回転子を用いるもの (1)

国際特許分類[H01P1/36]に分類される特許

1 - 10 / 180

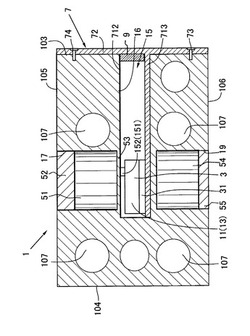

非可逆回路素子及び通信装置

【課題】電磁波漏洩を極小化するとともに、組み立てを容易化した薄型の非可逆回路素子及びこれを用いた通信装置を提供すること。

【解決手段】 第1金属部材1と、第2金属部材7とを含む。第1金属部材1は、連続する金属体でなり、第1導波路11と、第2導波路13と、部材挿入孔16とを含んでいる。第1導波路11及び第2導波路13は、入出力導波路である。部材挿入孔16は、第1金属部材の内部において第1導波路11及び第2導波路13と交差している。第2金属部材7は、部材挿入孔16内に挿入され、第1導波路11及び第2導波路13と交差する第3導波路15を構成する、

(もっと読む)

送信モジュール

【課題】 コアアイソレータ素子の挿入損失の増加を抑制した、送信モジュールを提供する。

【解決手段】 回路基板2は、グランドパターン3A〜3Dを備えた多層基板である。回路基板2には、電力増幅器10およびコアアイソレータ素子14が実装される。電力増幅器10およびコアアイソレータ素子14は、樹脂層12によって覆われる。樹脂層12の表面にはシールド層13が設けられる。コアアイソレータ素子14の天面14Aと、天面14Aと対向するシールド層13の天面シールド層13Aとの間隔、コアアイソレータ素子14の側面と、この側面と対向するシールド層13の側面シールド層との間隔を、所定の距離だけ離間して、コアアイソレータ素子14による挿入損失の増加を抑制する。

(もっと読む)

電子素子、その製造方法、フェライト・磁石素子及びその製造方法

【課題】フープ材から形成したヨークなどの枠状体を有する電子素子において、リードフレームのカット残りを極力小さくして、素子の小型化を図ること。

【解決手段】対向した一対の主面を有するフェライト32と、フェライト32の少なくとも一の主面に配置された中心電極と、フェライト32の一対の主面にそれぞれ固着された永久磁石41と、永久磁石41及びフェライト32の外周面を囲むように配置された平面視で略四角形状をなす枠状のヨーク50と、を備えた非可逆回路素子。ヨーク50は、フープ材から枠状に形成したものであり、かつ、フープ材の基部と連結するリードフレームが、ヨーク50の略対角線上に延在されており、該リードフレームはカットされた後はカット残り53’として残される。

(もっと読む)

表面実装型非可逆回路素子用配線基板及びこれを備える移動体通信機器

【課題】設計変更に柔軟に対応可能な表面実装型非可逆回路素子用配線基板を提供すること。

【解決手段】表面実装型非可逆回路素子用配線基板1は、表面実装型非可逆回路素子が有する入力用外部端子及び出力用外部端子に相対して形成された第1入力用ランド12及び出力用ランド13と、第1入力用ランド12と導通する第2入力用ランド16と、第1出力用ランド13と導通する第2出力用ランド17とを備え、表面実装型非可逆回路素子2の不使用時、第2入力用ランド16及び該第2出力用ランド17間を導通する表面実装型電子部品が実装される。

(もっと読む)

電子部品モジュール

【課題】 永久磁石を備えたチップ素子と、チップ素子の周囲に高密度に近接して配置した電子部品との配置状態のみだれを低減する。

【解決手段】 アイソレータ1は、フェライト3および永久磁石10A,10Bからなるチップ素子2と、チップ素子2が実装される回路基板12とを備える。フェライト3の下面3Dには、接続端子となる導体接続部9A,9B,9Fが形成されている。回路基板12の表面12Aには、導体接続部9A,9B,9Fと接合されるパッド13A,13B,13Cが形成されている。また、回路基板12の表面12Aには、永久磁石10A,10Bと対向する部位に位置して複数個の位置固定部16が形成されている。チップ素子2の実装時には、永久磁石10A,10Bと位置固定部16との間に磁力による引力が作用する。

(もっと読む)

送信回路

【課題】方向性結合器を必要とすることなくアンテナからの反射信号をアイソレータによって検出でき、好ましい送信状態に自動的に調整できる送信回路を得る。

【解決手段】終端抵抗Rを有するアイソレータ20と、終端抵抗Rの発熱量を検出する熱量検出手段(サーミスタS1)と、アンテナ特性を切り替える調整手段(スイッチング素子Sw)と、サーミスタSによる検出値に基づいて制御信号を出力することによってスイッチング素子Swを変化させる制御手段30と、を備えた送信回路。

(もっと読む)

非可逆回路素子

【課題】 小型化しても実装用の端子部分の強度に優れ、面実装性や電気的接続を損なわず、優れた挿入損失特性等の電気的特性を有する非可逆回路素子を提供することである。

【解決手段】

永久磁石を保持する第1ヨークと、フェライト部材に中心導体を備えた中心導体部と、前記中心導体部を実装しキャパシタンス素子を構成する電極パターンを備える多層基板と、前記多層基板を実装するプリント基板により構成され、前記プリント基板の前記多層基板を実装する第1主面の周縁には、前記第1ヨークを実装する第1電極パターンを備えた。

(もっと読む)

非可逆回路素子及びフェライト・磁石素子

【課題】一つの組立体として複数の周波数帯で動作可能なフェライト・磁石素子及び非可逆回路素子を得る。

【解決手段】単一のフェライト32と、フェライト32の長辺方向の少なくとも二つの領域にそれぞれ形成されて複数の周波数帯(例えば、836MHz帯、1.95GHz帯)にそれぞれ対応する複数種類の中心電極と、フェライト32の主面に固着された永久磁石41とを備えたフェライト・磁石素子。永久磁石41はフェライト32及び複数種類の中心電極に直流磁界を印加する。

(もっと読む)

非可逆回路素子及びフェライト・磁石素子

【課題】回路基板に設けられる端子電極の長大化を解消するとともに、リフローはんだ処理での実装時におけるフェライト・磁石素子の位置ずれを効果的に防止する。

【解決手段】対向した一対の主面を有するフェライト10の少なくとも一の主面に中心電極を配置し、該フェライト10の一対の主面にそれぞれ永久磁石20A,20Bを固着してなるフェライト・磁石素子9を、回路基板上に、フェライト10の主面が垂直に位置するように実装した非可逆回路素子。フェライト10の下面には中心電極と電気的に接続された接続用電極15a,15b,17aが設けられ、永久磁石20A,20Bの下面には接続用電極15a,15b,17aと接続された接続用補助電極18a,18b,18cが設けられ、接続用補助電極18a,18bは永久磁石20Aの下面には延在しておらず、接続用補助電極18cは永久磁石20Bの下面には延在しておらず、かつ、接続用補助電極18a,18b,18cはフェライト10の長辺方向に沿って千鳥状に配置されている。

(もっと読む)

フェライト・磁石素子及びその製造方法

【課題】ヨークを個別品としてではなく、フェライトや永久磁石と一体的に取り扱うことができ、かつ、製造上の歩留まりが向上するフェライト・磁石素子及びその製造方法を得る。

【解決手段】対向した一対の主面を有するフェライト32の少なくとも一の主面に中心電極を配置し、該フェライト32の一対の主面にそれぞれ永久磁石41を固着してなるフェライト・磁石素子30。永久磁石41のフェライト32と反対側の主面には緩衝材45が固着されており、緩衝材45の表面からフェライト32と永久磁石41の側面にわたって磁性体からなる板状のヨーク50が巻回した状態でかしめられている。

(もっと読む)

1 - 10 / 180

[ Back to top ]