国際特許分類[H03F1/08]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみ,半導体装置のみまたは汎用素子のみを用いた増幅器の細部 (3,631) | 増幅素子の内部インピーダンスの有害な影響を低減するための増幅器の変形 (134)

国際特許分類[H03F1/08]の下位に属する分類

多重電極接続をもつ増幅素子の使用によるもの

減衰手段の使用によるもの (3)

中和手段の使用によるもの (5)

分布結合の使用によるもの

カスコード結合,すなわちカソードまたはエミッタ接地段の次にそれぞれグリッドまたはベース接地段が続くもの,の使用によるもの (82)

国際特許分類[H03F1/08]に分類される特許

1 - 10 / 44

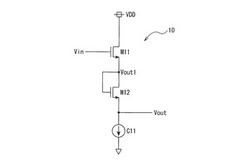

ソースフォロア回路

【課題】消費電力の増加を抑制しつつ、負荷回路からのキックバックを抑制する。

【解決手段】MOSトランジスタM11と、ゲートおよびドレイン間がダイオード接続されたMOSトランジスタM12と、電流源C11とを直列接続してソースフォロア回路10を構成する。MOSトランジスタM11のゲートに入力された、ソースフォロア回路10への入力信号Vinは、MOSトランジスタM11によりほぼ1倍の利得で出力され、さらに、ダイオード接続されたMOSトランジスタM12でほぼ1倍の利得で出力され、これがソースフォロア回路10の出力信号Voutとして出力されるため、結果的に、1段構成のソースフォロア回路と同様の動作をするが、その消費電力は少なくてすむ。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

可変利得増幅回路

【課題】反射特性が劣化するのと、利得の可変量が小さくなるのとを同時に回避する。

【解決手段】反転増幅回路と、反転増幅回路と並列に接続された負帰還回路と、反転増幅回路の入力側に設けられたバッファ増幅回路とを有する可変利得増幅回路において、インピーダンスを変化させることが可能なインピーダンス調整部を有し、反転増幅回路とバッファ増幅回路とは、インピーダンス調整部を介して接続される。

(もっと読む)

インピーダンス整合回路、電力増幅器、低雑音増幅器及び無線通信機器

【課題】面積の増加を抑制しつつ、複数の周波数帯域の信号を対象としたインピーダンス整合が可能なインピーダンス整合回路を提供する。

【解決手段】本発明のインピーダンス整合回路1は、入出力端である一端2と他端3との間に直列に接続されるように構成された整合素子ブロック51及びスイッチ54と、一端2と他端3との間で、整合素子ブロック51及びスイッチ54に並列に接続されるように構成されたスイッチ55と、整合素子ブロック51とスイッチ54とを互いに接続するノードとグランドとの間に設けられるように構成されたスイッチ56と、を備える。

(もっと読む)

負荷効果低減回路

【課題】 増幅器の出力に負荷が接続された場合、その増幅器の出力段が持つ出力インピーダンスと接続した負荷によって、出力が理想値からずれる。本発明はこの負荷効果による出力のずれを自動的に補正する負荷効果低減回路を提供することを課題とする。

【解決手段】 増幅器の出力部と負荷との節点に設けられ、増幅器の入力電圧と出力電圧の差電圧に応じた電流を自動的に負荷に供給することを特徴とする負荷効果低減回路により解決される。上記回路は、増幅器の入力電圧及び上記節点の電圧を入力とする差動アンプと、該差動アンプの出力電圧と該節点の電圧とを加算する加算器と、該加算器の出力を入力とし該節点に電流として出力する電圧−電流変換回路とを含む。

(もっと読む)

増幅器

【課題】動作周波数における特性劣化を抑えつつ、特定周波数における不要発振を抑制して安定した動作を行う増幅器を提供する。

【解決手段】ソース接地アンプを構成する第1のFETと、ゲート接地アンプを構成する第2のFETがカスコード接続し、第1のFETのゲート端子から入力した信号を第2のFETのソース端子から出力する増幅器で、第1のFETのドレイン端子と第2のFETのソース端子との間に、発振を防止する周波数における第1のFETのドレイン端子の負荷インピーダンスが、出力インピーダンスよりショートに近づくように設計された発振防止回路を備える。

(もっと読む)

電子回路および電子装置

【課題】小容量のキャパシタンス素子を介して信号検出可能な高入力インピーダンスでかつひずみの少ない緩衝増幅回路を、極端に高抵抗値、高容量値の抵抗器やコンデンサーを用いずに実現する。

【解決手段】非反転増幅回路と、前記非反転増幅回路に入力信号を接続するキャパシタンス素子と、前記非反転増幅回路の出力信号を分圧する分圧回路と、該分圧回路信号を前記非反転増幅回路の入力端子に帰還するインピーダンス素子を含んで構成する。

(もっと読む)

電子回路および電子装置

【課題】小容量のキャパシタンス素子を介して信号検出可能な高入力インピーダンスの緩衝増幅回路を、極端に高抵抗値、高容量値の抵抗器やコンデンサーコンデンサーを用いずに実現する。また、誘導ノイズや帯電物の接近等による電位変動等の妨害に強い電子装置を提供する。

【解決手段】第一の非反転増幅回路と、前記第一の非反転増幅回路に入力信号を接続するキャパシタンス素子と、第二の非反転増幅回路と、前記第一の非反転増幅回路の出力信号を前記第二の非反転増幅回路に入力するコンデンサーと、前記第二の非反転増幅回路の出力信号を前記第一の非反転増幅回路に入力する抵抗器と、前記非反転増幅回路の入力と所定の電位間に接続されたスイッチ回路を含んで構成することによって電子回路を構成する。

(もっと読む)

高周波増幅回路

【課題】高周波増幅回路において、LC共振を用いずにピーキングをかけること。

【解決手段】高周波増幅回路は、1段目にトランジスタTr1を用いたエミッタ接地増幅回路、2段目にダーリントン接続のトランジスタTr2、Tr3を用いたエミッタ接地回路の2段増幅の構成となっている。トランジスタTr1のエミッタとトランジスタTr2のコレクタとの間には容量素子が挿入されている。容量素子は、ダイオード接続のトランジスタTr4であり、トランジスタTr4のエミッタはトランジスタTr2のコレクタに、トランジスタTr4のベースおよびコレクタはトランジスタTr1のエミッタに接続されている。ダイオード接続のトランジスタTr4によって位相をずらしてフィードバックすることにより、高域での利得を向上させることができる。

(もっと読む)

1 - 10 / 44

[ Back to top ]