国際特許分類[H03F1/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみ,半導体装置のみまたは汎用素子のみを用いた増幅器の細部 (3,631) | 増幅素子によって発生する雑音の影響を低減するための増幅器の変形 (251)

国際特許分類[H03F1/26]の下位に属する分類

電子管増幅器におけるもの (2)

国際特許分類[H03F1/26]に分類される特許

1 - 10 / 249

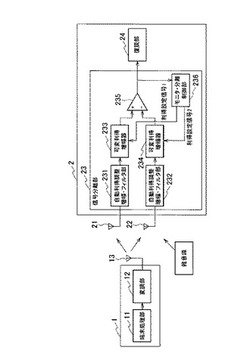

無線通信装置

【課題】雑音の大きな環境下でも安定した通信を可能とする。

【解決手段】アンテナ21,22で受信した信号を利得設定信号1,2で設定される利得で増幅する可変利得増幅器233,234と、可変利得増幅器233,234それぞれの出力信号の差を出力する差動増幅器235と、差動増幅器出力の振幅を検出する振幅モニタ部31と、差動増幅器出力の振幅の変動が最小となる利得設定信号1,2を求める分離制御部32を備える。これにより、アンテナ21,22で受信した信号から雑音を分離し、雑音の大きな環境下でも安定した通信を可能とする通信システムを提供することができる。

(もっと読む)

増幅回路

【課題】ノイズフィギュアの劣化を抑制しつつ、過入力信号を調整可能な上限電圧および下限電圧の範囲内に制限する。

【解決手段】入力トランジスタと、第1端が前記入力トランジスタのゲートに接続され、第2端がバイアス電圧に接続される抵抗素子と、前記入力トランジスタのゲートに接続され、前記入力トランジスタのゲートへの入力を、前記バイアス電圧を基準とする(調整可能な)上限電圧および下限電圧の範囲内に制限する保護回路と、を備える、増幅回路。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

送信増幅器

【課題】低ひずみ、低雑音、且つ小形な送信増幅器を得る。

【解決手段】多段接続した増幅器のうちの少なくとも1段以上に、バイポーラトランジスタ3のコレクタ電極とベース電極との間に接続された抵抗9を備え、出力電源10からインダクタ8および抵抗9を介してバイポーラトランジスタ3のベース電極に入力バイアスを供給する増幅器を備える。

バイポーラトランジスタ3の動作条件を決める入力バイアスを、抵抗9と出力電源10とにより決定するので、バイアス回路によるひずみがバイポーラトランジスタ3に重畳されないため、低雑音な送信増幅器を実現することができる。

また、入力バイアスを供給するためだけにインダクタを設ける必要がないため、小形な送信増幅器を実現することができる。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高利得、及び低電流消費と共に、非常に高い三次入力インターセプトポイント(IIP3)を有するLNAを提供する。

【解決手段】LNA222は、メイン電界効果トランジスタ(FET)302、キャンセルFET304、第1ソース・ディジェネレーション・インダクタ306、第2ソース・ディジェネレーション・インダクタ308、カスコード・トランジスタ310、及びLNA負荷312を含む。LNA負荷312は、並列に結合されたインダクタ314及びキャパシタ316を含むLCタンク回路である。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高線形性と低歪みの増幅器を提供する。

【解決手段】修正された微分重ね合わせ低ノイズ増幅器は、メイン電流経路とキャンセル電流経路を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタが、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第2の新規な側面では、LNA負荷を通過しないデブースト電流経路が設けられる。デブースト電流は、ヘッドルームの問題を生じさせることなく、ネガティブ・フィードバックを増加させる。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

イメージセンサー及びこれを備えるX線イメージセンシングモジュール

【課題】高品質のイメージが得られるイメージセンサーを提供する。

【解決手段】検出部で検出された電荷を増幅させ、入力端子、増幅端子、及び出力端子を含む電荷検出増幅部を備え、電荷検出増幅部は、入力端子と前記増幅端子との間に接続された第1キャパシタと、入力端子と前記増幅端子との間に接続された第1スイッチングユニットと、増幅端子と出力端子との間に接続された第2キャパシタと、出力端子と基準電圧端子との間に接続された第2スイッチングユニットと、を備えることを特徴とするイメージセンサー。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

増幅装置

【課題】 入力される高周波信号のレベルが小さい時はNF特性を十分に向上すると共に、高周波信号のレベルが大きい時は歪特性を十分に向上する。

【解決手段】 TR1のコレクタに接続されているコイルL2(負荷手段)とVccとの間に接続された抵抗R9と、該抵抗R9に並列接続された制御電圧Vgcに応じてオン/オフするTR3と抵抗R8との直列回路とからなるバイアスコントロール部11を備えている。入力信号のレベルが小さい時は、制御電圧VgcによりTR2,TR3がオフすることにより、TR1のバイアスが浅くなってNF特性が向上され、入力信号のレベルが大きい時は、制御電圧VgcによりTR2,TR3がオンすることにより、TR1のバイアスが深くなって歪特性が向上される。

(もっと読む)

増幅器

【課題】増幅器の出力雑音電圧を抑制する。

【解決手段】正転入力電圧と反転入力電圧の差分を増幅する差動入力回路1と、差動入力回路1の出力信号を増幅して出力端子に出力する出力回路2と、差動入力回路1の電流源MP3と出力回路2の電流源MP4にバイアス電圧を出力するバイアス回路5を備えた増幅器である。差動入力回路1の正転入力電圧と反転入力電圧が共に接地電圧のときに出力端子に現れる出力雑音電圧を検出し、該雑音電圧のレベルが高いほど、バイアス回路5が、電流源MP3,MP4の電流を増大させるバイアス電圧を出力するようにした。

(もっと読む)

1 - 10 / 249

[ Back to top ]