国際特許分類[H03K19/0185]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 結合装置;インターフェイス装置 (1,927) | 電界効果トランジスタのみを用いるもの (456)

国際特許分類[H03K19/0185]に分類される特許

1 - 10 / 456

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

半導体装置

【課題】低電圧動作を実現可能なレベルシフト回路を提供する。

【解決手段】入力電位は、GNDとVDDとの間で切り替わる。電源端子には、VDDよりも高いVDDOが印加される。レベルシフト回路は、クランプ回路と接続制御回路を備える。クランプ回路は、ソースが第1ノードに接続され、ドレインがP側出力端子に接続され、ゲートが電源端子に接続された第1NMOSトランジスタと、ソースが第1ノードに接続され、ドレインがN側出力端子に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタと、を備える。入力電位がGNDとVDDの一方の場合、接続制御回路は、P側出力端子にVDDOを印加し、且つ、N側出力端子とグランド端子との間の電気的接続を遮断する。入力電位がGNDとVDDの他方の場合、接続制御回路は、N側出力端子にGNDを印加し、且つ、P側出力端子と電源端子との間の電気的接続を遮断する。

(もっと読む)

レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

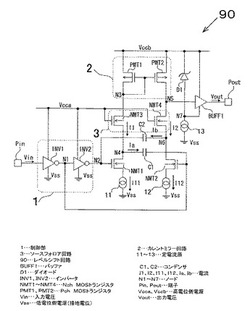

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、高電源電位が入力される入力端子とグランド端子との間に接続された抵抗と、抵抗中の第1ノードに接続された第2ノードと、第2ノードと第3ノードとの間に接続されたインバータと、抵抗を通した入力端子とグランド端子との間の電気的接続をON/OFF制御するスイッチと、を備える。ターゲット反転電位は、インバータの反転電位よりも高い。入力端子の電位がターゲット反転電位の場合、第2ノードの電位がその反転電位となる。第2ノードの電位が反転電位より低い場合、インバータは低電源電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をONする。一方、第2ノードの電位が反転電位より高い場合、インバータはグランド電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をOFFする。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

1 - 10 / 456

[ Back to top ]