国際特許分類[H03K3/64]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電気的パルスの発生回路;単安定回路,双安定回路,多安定回路 (1,702) | パルス列,すなわち有限の続発パルスを発生する発生器 (17)

国際特許分類[H03K3/64]の下位に属する分類

発生器出力の断続によるもの (5)

パルス列繰返数を変化させるための手段をもつもの (3)

国際特許分類[H03K3/64]に分類される特許

1 - 9 / 9

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

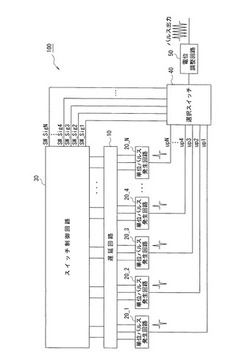

【解決手段】パルス発生装置100を、起動開始信号D0の入力に応じて単位パルス信号を発生する、各々の信号出力部が独立した単位パルス発生回路20_1〜20_Nと、単位パルス発生回路20_1〜20_Nのうち単位パルス信号を出力する予定の一部の回路の信号出力端子を順次選択して、該選択した信号出力端子を共通の信号出力線Pu_Coutに電気的に接続し、残りの単位パルス発生回路の信号出力端子を共通の信号出力線Pu_Coutから電気的に切断するスイッチ制御回路30及び選択スイッチ40とを含む構成とした。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を

提供する。

【解決手段】パルス発生装置100を、CLK信号の入力に応じて起動開始信号D0と、

D0を反転したXD0とを出力する起動開始信号生成回路20と、起動開始信号の入力に

応じてパルス信号を発生する、各々の信号出力部が独立した第1〜第Nのパルス発生回路

21_1〜21_Nと、第1〜第Nのパルス発生回路21_1〜21_Nのうちパルス信

号を出力する予定の一部の回路の信号出力部を順次選択して、該選択した信号出力部を共

通の信号出力線に接続し、残りのパルス発生回路の信号出力部を共通の信号出力線から電

気的に切断する選択回路22とを含む構成とした。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路でかつ低消費電力で帯域制限された正確な短パルスの発生回路を具現し、フィルタを使用せずに目的のパルスを得る。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点から所定量の時間差で位相が順次変化するn+1個の信号(nは2以上の整数)を発生するタイミング発生回路と、所定の電位を供給する第1の電源及び第2の電源と、n個のインピーダンス素子と、n+1個の信号に基づく論理関数値によって所定順序で出力端子と第1の電源または第2の電源とをインピーダンス素子を介して交互に切り替えて接続するスイッチ回路と、を含むパルス発生回路。

(もっと読む)

パルス生成器、およびそれを備えた送信機

【課題】低消費電力で、複数の周波数帯域に対応するパルスを生成するパルス生成器を提供する。

【解決手段】本発明に係るパルス生成器10は、遅延部3から出力された遅延信号DL0〜DL15に基づいて基準パルスSQA1〜SQA7と基準パルスSQB1〜SQB5とをそれぞれ生成し、基準パルスSQA1〜SQA7を列とした送信パルスAと基準パルスSQB1〜SQB5を列とした送信パルスBをそれぞれ生成する。基準パルスSQA,SQBは、パルス幅がそれぞれ異なるため、送信パルスA,Bの時間幅もそれぞれ異なり、複数の周波数帯域に対応するパルスを生成することができる。

(もっと読む)

パルス波形生成器及び送信機

【課題】複数の周波数帯域に対応する複数のパルス波形を低消費電力で生成可能とする。

【解決手段】PLL回路102内のVCOの発振周波数を所定の値にすることにより、所定の遅延時間に調整が可能な遅延器を複数個直列に接続し、初段の遅延器に入力するデジタル信号TQをパルス波形生成を開始したいタイミングで反転させることにより、各遅延器が出力するデジタル信号TQを所定の遅延時間で順次遅延させた複数の遅延信号DLnを出力する遅延回路103と、前記遅延器から出力される所定の時間間隔となる2つの遅延信号を順次合成することにより、所定の時間間隔の幅を持つ方形波を発生させる方形波発生回路104と、前記方形波によって出力電圧を選択する出力電圧選択回路105とを備え、前記遅延器における所定の遅延時間と出力電圧選択回路105における出力電圧の選択内容とを変更することにより、複数の特定波形を出力する。

(もっと読む)

周期制御パルス発生回路

【課題】 従来の周期制御パルス発生回路では、タイミングパルスの出力制御が比較一致検出によって行われており、特に分周数が大きな値の場合においては比較一致回路の回路規模が極めて大きくなってしまう。

【解決手段】 分周数カウント値を記憶し出力するカウント値ラッチ回路103と、分周数カウント値が所定の閾値以下の場合にタイミングパルスを出力する検出回路106と、タイミングパルスの目標平均周期に対応する入力周期値と分周数カウント値とを加算する加算回路104と、分周数カウント値を所定の値で減算する減算回路105と、タイミングパルスを入力切り替え信号とし、加算回路104、及び減算回路105の出力値のいずれか一方を新たな分周数カウント値としてカウント値ラッチ回路に出力するセレクタ107とで構成され、所望の目標平均周期のタイミングパルスを出力する。

(もっと読む)

パルス発生器及びそれを用いた送信機

【課題】 UWB伝送用パルス発生器における構成の簡易化、低消費電力化と、LO信号を使わないことによるLOリークの抑制。

【解決手段】 所定の周期のクロックを与えるクロック発生装置(CLK)と、遅延時間制御機能を持ち前記クロックを遅延させる遅延回路(DLY)と、前記遅延回路から出力される遅延時間の異なる信号同士を比較することで遅延回路一段分の遅延時間差に相当するパルス幅を持つ方形波パルスを、拡散符号により拡散された情報を受け取ることで位相を変調して出力する方形波パルス発生回路(SWPG)と、前記方形波パルス発生回路から異なるタイミングで出力される方形波パルス列を受け取ることにより、前記方形波のパルス幅を持ち所定の振幅でインパルス列を出力し、重ね合わせる振幅制御ユニット(AMPC)を有し、所定の包絡線形状を有するパルスを生成する。

(もっと読む)

ドライブパルス列を供給するドライブ回路およびドライブパルス列の供給方法

【課題】ライブパルス列をフレキシブルに形成するドライブ回路を提供する。

【解決手段】マトリクス素子を備えたスイッチングマトリクスが設けられており、マトリクス素子は期間のうちの少なくとも1つと、少なくとも1つの制御パラメータからなるただ1つの組にその都度割り当てられており、n個のパルス発生器のうちの1つの丁度1つのスイッチング素子に対する制御信号を出力する。

(もっと読む)

パルス駆動型ジョセフソン波形発生方法及び発生回路

【課題】 ジョセフソン接合素子をパルス駆動し、大出力と精度を同時に実現して任意波形を発生させるパルス駆動型ジョセフソン波形発生方法および装置を提供するものである。

【解決手段】 入力バルスとして、従来の波形を時間軸でみて主として一つの大きな尖頭値を有する波から構成され、かつ波の最大値と最小値の比が大きく、周波数軸でみて出力波形の周波数と重畳しない領域の二つの周波数f1およびf2で規定される幅を持つ波形で置き換えることにより、任意信号出力においても波形精度を高める。換言すると、入力信号(最終的に出力させたい信号)が波形発生回路に残っていると、この入力信号が途中の回路素子に作用して変化した信号が最終的に出力に現れ、欲しい信号のみが出力されなくなる場合が発生する。これをなくすために、周波数スペクトル上で入力信号成分を除いた信号を使って最終出力を得る。

(もっと読む)

1 - 9 / 9

[ Back to top ]