国際特許分類[H03K5/153]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号が予定された特性にきたとき瞬時にまたはある時間間隔をもって1つのパルスを与える配置 (165)

国際特許分類[H03K5/153]の下位に属する分類

国際特許分類[H03K5/153]に分類される特許

1 - 10 / 36

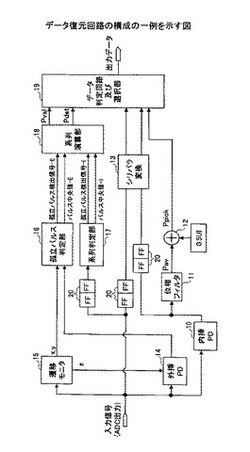

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

パルス生成回路およびミュート装置

【課題】 矩形波信号の立ち上がりエッジおよび立ち下がりエッジを検出し、一方のレベルのパルス信号を生成するパルス生成回路において、トランジスタの数を削減すること。

【解決手段】 立ち下がりエッジ検出部2は、矩形波信号の立ち下がりエッジを検出し、所定時間だけ、トランジスタQ1をオン状態に制御する。立ち上がりエッジ検出部は、矩形波信号の立ち上がりエッジを検出し、所定時間だけ、トランジスタQ2をオン状態に制御する。トランジスタQ1は、立ち下がりエッジ検出部2が矩形波信号の立ち下がりエッジを検出した時から所定時間、および、トランジスタQ2がオン状態である期間に、オン状態になり、ハイレベルのパルスを出力する。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

パラレル−シリアル変換器及びパラレルデータ出力器

【課題】パラレル−シリアル変換器において、データ信号をラッチするフリップフリップ(FF)に供給されるクロック信号の位相ずれを調整する。

【解決手段】FF1−1〜1−5によるデータ信号D0,D1を選択回路2で選択出力したデータ信号D[0+1]をFF4によりラッチ出力するパラレル−シリアル変換器において、レプリカのデータ信号repIN0,repIN1を選択回路10で選択出力したデータ信号repDをラッチしたFF11によるデータ信号repOUTに基づき位相ずれ検出回路12,13が生成する位相調整指示値信号に従い、分周回路3による分周クロック信号の位相を調整してクロック信号divCLKを発生する任意位相生成回路15を備えると共に、クロック信号ffCLKとrepCLKとを位相比較し、クロック信号repCLKを移相させる位相設定回路16,17を備える。

(もっと読む)

クロックスキュー自動調整回路及びその調整方法

【課題】従来のクロックスキュー調整回路では、精度の高いクロックスキュー調整を行うことができないという問題があった。

【解決手段】本発明にかかるクロックスキュー自動調整回路は、クロックのドライブ能力を調整するクロックドライバ101と、クロックの信号変化開始から信号変化終了までに要する時間を計測する計測回路102と、前記計測時間と予め設定された基準時間とに基づいて制御信号を生成し、前記クロックドライバに対して出力する制御回路103と、を備える。このような回路構成により、精度の高いクロックスキュー調整を行うことができる。

(もっと読む)

トリガ回路及びトリガ信号発生方法

【課題】高帯域幅且つ低ジッタで、差動信号からトリガ信号を発生する。

【解決手段】差動信号源201からの差動信号が抵抗減衰器219、220を介して比較器211の非反転入力端及び反転入力端に供給される。電圧源203、204からの差動しきい値電圧レベルが終端抵抗器207、208を介して比較器211の非反転入力端及び反転入力端に供給される。比較器211は、非反転入力端及び反転入力端の電圧が交差したときに、トリガ出力端214からトリガ信号を発生する。

(もっと読む)

ジッタ測定回路

【課題】周期信号の周期を測定することなくジッタ量をディジタル出力すること。

【解決手段】本発明に係るジッタ測定回路10は、入力される被測定信号5を当該被測定信号のエッジから所定の時間単位である第1の時間で遅延させることによりエッジ間パルス信号6を生成するエッジ間パルス生成部1と、エッジ間パルス信号6を、所定の時間単位である第2の時間を整数倍した値により除算し、該除算演算による剰余結果を剰余結果信号Mとして出力するパルス幅剰余分割部2と、剰余結果信号Mの値が最小となる場合の整数の値を、エッジ間パルス信号6のサイクルジッタ値信号Dとして出力するワンホットステート部4と、を有する。

(もっと読む)

パルス検出装置及びパルス検出方法

【課題】パルス信号を高精度に検出すること。

【解決手段】パルス検出装置1は、所定期間に中間電位を含むパルス信号を検出する。また、パルス検出装置1は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定手段を備えている。さらに、信号固定手段は、パルス信号が入力される入力信号線に接続されたプルダウン抵抗9又はプルアップ抵抗であるのが好ましい。なお、パルス検出方法は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定工程を含んでいる。

(もっと読む)

単一電圧源CMOSのための自動検出入力回路

【課題】入力パッドに印加される比較的高電圧を維持し、回路内の供給電圧範囲の対応する信号レベルを生成する。

【解決手段】入力回路は、フローティングウェルと、対応するバイアスセレクタと、入力バイアストランジスタとを有し、予め定められた値より大きい電圧を維持する外部電圧にゲート酸化膜がさらされないようにする。バイアスセレクタは、利用可能な最高電圧を選択してフローティングウェルに対応するバイアスを逆にし、トランジスタに過度な電気的ストレスがかからないようにする。入力に関連する端子が関連する電圧を切り換えられると、バイアスセレクタは、別の端子を選択し、引き続き利用可能な最高電圧を選択して正しい逆バイアス条件を提供する。抵抗器およびクランプは、回路内の供給電圧範囲に制限された、変換された出力電圧レベルを生成する。ラッチ出力により、プルダウントランジスタは、正確なロウレベル出力信号を提供できる。

(もっと読む)

1 - 10 / 36

[ Back to top ]