国際特許分類[H03K5/19]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルス列のパターンの監視 (177)

国際特許分類[H03K5/19]に分類される特許

1 - 10 / 177

半導体集積回路装置

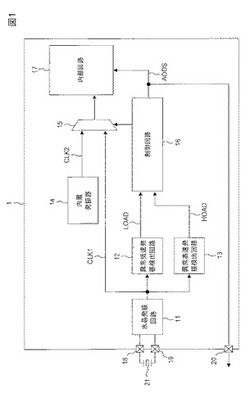

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

信号測定装置及び信号測定方法

【課題】スペクトラム拡散に係る拡散率を容易に推定する。

【解決手段】三角波によってスペクトル拡散されたクロック信号を入力する入力部(11に相当)と、クロック信号から三角波の周期を抽出する周期成分抽出部(13に相当)と、クロック信号における周期変動の変動幅を抽出する周期変動抽出部(14に相当)と、三角波の周期と周期変動の変動幅とに基づいてスペクトル拡散における拡散率を求める演算処理部(16に相当)と、を備える。

(もっと読む)

クロック診断回路

【課題】単一のクロックから、クロック周期、及びクロックパルス幅の変動の異常を確実に検出することができるクロック診断回路を提供することを目的とする。

【解決手段】クロックs10を予め設定されるクロックパルス幅以下の所定時間、遅延させる遅延回路2と、遅延回路2から出力された遅延クロックを所定の周期数倍遅延させる整数倍遅延回路3と、クロックを、遅延クロックを用いて符号化する第1の排他的論理和回路4と、第1の排他的論理和回路4の出力を、整数倍遅延回路3の出力を用いて復号化する第2の排他的論理和回路5と、クロックs10と第2の排他的論理和回路5の出力とを比較して、クロックの異常を検出する比較回路6と、を備え、クロックパルス幅、及びクロック周期の変動を、自身の単一のクロックに基づいて検出するようにしたことを特徴とするクロック診断回路1。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

非同期データ転送装置

【課題】電流量の監視による遅延仮定なしで配線故障検出ができ、遅延故障耐性と配線故障耐性を同時に有した非同期データ転送装置を提供する。

【解決手段】IPコア間に配設するLSIの非同期データ転送装置1において、第1のIPコアに接続する第1の配線3aと、第2のIPコアに接続する第2の配線3bと、第1の配線3aに接続する送信器2と、第2の配線3bに接続する受信器4と、送信器2と受信器4とを接続する第3の配線3cと、を含み、送信器2は、符号器5と入力制御部6とを有する入力部2Aと、出力部2Bと、を含み、受信器4は、入力部4Bと、復号器7と出力制御部8とを有する出力部4Aと、を含み、送信器2の符号器5は、第3の配線3cのオープン故障を検出する電流ドライバ回路11a,11b,11c,11dを備える。

(もっと読む)

クロック逓倍回路及び半導体装置

【課題】逓倍されたクロック信号のパルス数が逓倍数の値からずれる状態を原理的に阻止することができるクロック逓倍技術を提供する。

【解決手段】第2クロック信号(CLK2)のサイクル単位で、第1クロック信号(CLK1)の計数値を逓倍数で除した商の値に対応するサンプリングクロックサイクル数を単位として第3クロック信号(CLK3)を順次生成すると共に、生成された一つの逓倍クロックサイクルにおいて前記商の余りに対応する当該サンプリングクロックのサイクル期間に対応して逓倍クロック信号の変化を抑止する制御(106)を行う。

(もっと読む)

発振停止検出回路、半導体装置、時計および電子機器

【課題】 難しいプロセス条件のコントロールを必要とせず、所期の性能を持ったものを安価に製造することができる発振停止検出回路を提供する。

【解決手段】 Pチャネルトランジスター11および12は、発振回路の出力信号から生成される制御信号SA、SBに従ってスイッチング動作して電荷を転送し、キャパシター20を充電する。インバーター30は、キャパシター20の充電電圧VCを2値化し、発振状態判別信号を出力する。Nチャネルトランジスター26は、キャパシター20を放電させるトランジスターである。基準電圧発生回路21は、ゲートおよびソースが互いに接続されたデプレッション型Pチャネルトランジスター22と、ゲートおよびドレインが互いに接続されたNチャネルトランジスター23とを直列接続してなるものであり、Nチャネルトランジスター23とNチャネルトランジスター26はカレントミラーを構成する。

(もっと読む)

周波数判定回路および半導体装置

【課題】長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供する。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

(もっと読む)

信号発生装置および試験装置

【課題】エッジの位相を固定して、信号のデューティ比を変更する。

【解決手段】指定されたデューティ比の出力信号を出力する信号発生装置であって、入力信号と出力信号との位相差を検出する位相検出器と、位相検出器により検出された位相差をフィルタリングして、発振器に供給するループフィルタと、位相差に応じた周波数の発振信号を出力する発振器と、指定値に応じて発振信号のデューティ比を変更して出力信号として出力するとともに位相検出器に供給するデューティ変更部と、を備える信号発生装置を提供する。

(もっと読む)

1 - 10 / 177

[ Back to top ]