国際特許分類[H03M1/18]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 符号化,復号化または符号変換一般 (10,763) | アナログ/デジタル変換;デジタル/アナログ変換 (2,647) | アナログ/デジタル変換器 (1,364) | 変換器が処理できる信号の範囲を修正するための自動制御,例.利得を変動するもの (82)

国際特許分類[H03M1/18]に分類される特許

1 - 10 / 82

レベル調整装置、およびレベル調整のためのプログラム

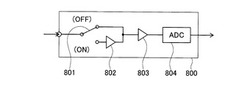

【課題】ユーザに負担をかけることなく、容易にアナログ音響信号の音質劣化を抑制することが可能なレベル調整装置を提供すること。

【解決手段】入力ポートはアナログ入力ブロック800を有し、アナログ入力ブロック800は、迂回スイッチ801、固定ゲインにて信号レベルの減衰を行うパッド802、可変ゲインにて信号レベルを増幅又は減衰して調整するアンプ803を備える。迂回スイッチ801はパッド802とアンプ803により信号レベルが調整されるパッドオン状態とアンプ803のみで信号レベルが調整されるパッドオフ状態を切り替えられる。信号レベルの調整の後に、パッドオン状態で、かつパッドのオン・オフの何れの状態でもゲインの調整が可能な重複範囲ROVの範囲内である入力ポートを抽出し、該当する入力ポートのアナログ入力ブロック800に対して、パッドオフ状態への切り替え調整処理を行う。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

無線受信装置、無線受信装置のキャリブレーション方法、無線受信装置の時系列変化分補正方法及び無線基地局装置

【課題】無線受信装置の受信ダイナミックレンジを拡大する。

【解決手段】アナログ受信回路2で受信された無線周波数信号を周波数変換して得られる中間周波信号を振幅に関し複数の信号部分に分割して出力する信号分割部3と、信号分割部で分割された複数の信号部分のそれぞれについてアナログ/ディジタル変換してディジタル受信回路6側へ出力する複数のアナログ/ディジタル変換器4,5とをそなえる。

(もっと読む)

超音波診断装置および超音波画像生成方法

【課題】画像生成処理の高速化と省電力化を図ることができる超音波診断装置を提供する。

【解決手段】アレイトランスデューサから出力される受信信号の振幅に応じて、受信信号処理部による受信信号のA/D変換可能範囲のうち実際にA/D変換が実行されるA/D変換実行範囲を限定し、受信信号のA/D変換を行う。A/D変換実行範囲は、測定深度に関わらずに所定のビット幅を有し、A/D開始ビットおよびA/D終了ビットで特定され、測定深度が増すほど、A/D変換実行範囲のA/D開始ビットおよびA/D終了ビットが漸減される。

(もっと読む)

AD変換器およびAD変換方法

【課題】先行する先行入力信号に対する現在の入力信号の差分信号の大きさや符号に関わらずAD変換を可能とするAD変換器およびAD変化何方法を提供すること。

【解決手段】サンプリング容量で先行入力信号に対する入力信号の差分信号をサンプリングする。オフセット回路でサンプリングされた差分信号にオフセットを付与する。検出回路でオフセットの付与された差分信号が規定の信号範囲にあるか否かを検出する。検出回路により規定の信号範囲にあると判断される場合には規定ビット分解能から規定の信号範囲に対応するビット数を縮小した縮小ビット分解能で差分信号のAD変換を行なう。規定の信号範囲にないと判断される場合には、規定ビット分解能で入力信号のAD変換を行なう。

(もっと読む)

アナログデジタル変換器

【課題】広い範囲のアナログ信号を高精度でデジタル信号に変換するためには前段に可変ゲインアンプが必要であるが、このため高価なアナログ部品が必要であった。本発明は簡単な構成でゲインを可変できるアナログデジタル変換器を提供することを目的にする。

【解決手段】アナログ信号とフィードバック信号の差分信号を積分し、この積分信号をそのレベルに対応するデューティ比を有する信号に変換して、この信号のデューティ比をゲイン設定器で(1/ゲイン)に変換した信号をデューティ/レベル変換してフィードバック信号を生成するようにした。高価なアナログ部品を使用しなくてもよい。

(もっと読む)

電流検出回路

【課題】離散的範囲で高精度の電流検出が必要な場合に、アナログディジタル変換器のビット数を抑制することである。

【解決手段】電流検出回路10は、大電流範囲の電流検出用に小抵抗値を有する第1抵抗素子12と、小電流範囲の電流検出のための小電流検出部20と、大電流範囲と小電流範囲とで電流パスを切り替える切替部14と、バッファアンプ部30,32と、アナログディジタル変換回路部40、42と、切替部14に切替信号を出力する切替制御回路34とを含んで構成される。小電流検出部20は、小電流範囲の電流検出用に大抵抗値を有する第2抵抗素子28と、バイパストランジスタ26と、第2抵抗素子28の両端子間電圧を閾値電圧である基準電圧22となるように制御する作動増幅器24を含んで構成される。

(もっと読む)

A/D変換装置

【課題】積分器の前段に増幅回路を追加することなく、ダイナミックレンジの広範囲化および高精度化が可能なA/D変換装置を提供する。

【解決手段】積分器1の出力電圧Voutを基準電圧Vrefと比較するコンパレータ2と、コンパレータ2の後段に設けられクロックパルスをカウントするカウンタ3と、カウンタ3のカウント値を積分器1の出力電圧Voutの振幅に応じたディジタル値に変換して出力する変換回路4と、積分器1の出力電圧Voutの振幅に応じたディジタル値を出力する比較型A/D変換器5と、選択回路6と、タイミング制御回路7とを備える。タイミング制御回路7は、積分器1を積分動作させる積分期間の終了直前の所定時までにコンパレータ2の出力Vcpが反転しない場合には、比較型A/D変換器5にA/D変換を行わせてディジタル値を選択回路6から出力させ、反転した場合には、変換回路4から出力されるディジタル値を選択回路6から出力させる。

(もっと読む)

A/Dコンバータ

【課題】アナログ入力信号の信号レベルに応じてFSR電圧を変化させることにより、D/Aコンバータの基準電圧を切り替える基準電圧発生回路の有無に関係なく、電圧変動の小さなアナログ入力信号に対する分解能を充分に向上させることができるA/Dコンバータを提供すること。

【解決手段】A/Dコンバータは、複数のアナログ入力信号のうちのいずれか1つを選択して出力する選択部の出力を第1比較基準電圧と比較する比較部と、前記複数のアナログ入力信号のうちのいずれか1つのアナログ入力信号の電圧変動範囲に応じた第2比較基準電圧を出力するD/Aコンバータと、前記選択部で選択されたアナログ入力信号の電圧変動範囲に応じて、前記D/Aコンバータが出力する第2比較基準電圧を前記第1比較基準電圧に切り替えて前記比較部に出力する切替部とを含む。

(もっと読む)

AD変換システム

【課題】ダイナミックレンジと分解能を両立させつつ高速なAD変換ができるAD変換システムを提供することを課題とする。

【解決手段】アナログ信号をデジタル信号に変換するAD変換システム1であって、アナログ入力信号をAD変換器15の複数のチャネル(Ch1,Ch2,Ch3)別に複数の電圧範囲に分割する分割手段13,14と、分割手段13,14で分割された異なる電圧範囲毎のアナログ入力信号をAD変換器15の各チャネルでそれぞれAD変換する分割AD変換手段15(Ch1,Ch2,Ch3)と、分割AD変換手段15でAD変換された異なる電圧範囲毎のデジタル信号を合成する合成手段16とを備えることを特徴とする。

(もっと読む)

1 - 10 / 82

[ Back to top ]