国際特許分類[H04L25/08]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | ベースバンド方式 (1,966) | 細部 (1,421) | 混信を低減するための変形;線路障害による影響を低減するための変形 (56)

国際特許分類[H04L25/08]に分類される特許

1 - 10 / 56

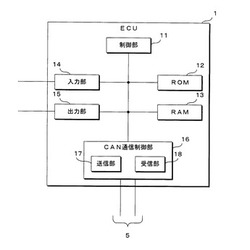

通信システム、通信装置、通信方法及び通信パラメータ決定方法

【課題】リンギングの影響を低減し、通信の高速化を実現可能な通信システム、通信装置、通信方法及び通信パラメータ決定方法を提供する。

【解決手段】ECU1の送信部17が、送信データがドミナントの場合に、1ビット分の送信時間より短いパルス幅Tpに亘る所定信号レベルの信号を通信線5へ出力し、その後は通信線5へ信号出力を停止してハイインピーダンス状態とすると共に、送信データがレセシブの場合に、通信線5へ信号出力をせずハイインピーダンス状態とする。またECU1の受信部18が、サンプリング期間Tdに亘って信号線5の信号レベルをサンプリングし、サンプリングした信号レベルの平均値を算出し、算出した平均値が閾値を超えるか否かに応じてドミナント/レセシブの判定を行う。

(もっと読む)

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

集積回路チップ及びこれを含む送受信システム

【課題】 伝送チップ上でのデータピン配列と、伝送チップと受信チップとの間のライン配列とが互いに異なってもクロストークを防止できる技術を提供すること。

【解決手段】伝送チップと、受信チップと、前記伝送チップから前記受信チップにデータを伝送するための複数のラインとを備え、前記伝送チップは、前記複数のラインに伝送されるデータパターンと前記複数のラインの配列情報とに応じて、前記複数のライン上で発生するクロストーク防止動作を行うことを特徴とする。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

伝送装置、伝送方法、画像形成装置、送信装置及び受信装置

【課題】併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とする。

【解決手段】送信側の通信装置1と受信側の通信装置4との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置である。送信側の通信装置1は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置4送信する。受信側の通信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信する。

(もっと読む)

受信機、通信システム及び受信方法

【課題】CPUの負担を軽減し、情報を正確に受信する。

【解決手段】第1のレートで変調されたデジタル信号S0が出力されると、このデジタル信号S0と等価なデジタル信号S3について、第1のレートよりも高い第2のレートでのサンプリングを実行する。そして、サンプリングした結果に基づいて、デジタル信号S0に含まれていたデジタル情報を抽出する。これにより、デジタル信号を受信する受信レジスタ22のサンプリングレートを設定した後は、例えばCPU等によるデジタル信号S0のビット数の変換処理等が不要になる。このため、受信されたデジタルデータを取り扱うCPUや制御機器の負担が軽減され、情報の受信を効率よく行うことが可能となる。

(もっと読む)

誘導雷が原因の過電圧の抑制

直流電圧フリーかつ差動の、EIA−485/EIA−422準拠の、TTPプロトコルに従った信号伝送を備えたフィールドバスのバスライン(102)へのバス接続ユニット(101)のための結合回路であって、バス接続ユニット(101)の送信/受信コンポーネント(104)の両方の入力部/出力部(108、109)が信号発信装置(103)の第一のコイルと、およびバスライン(102)の両方の極が信号発信装置第二のコイルと、接続されており、第一のコイルが中心タップ(107)を備え、この中心タップ(107)がバス接続ユニット(101)のローカル規準ポテンシャルとコンデンサー(105)とを接続しており、このコンデンサーの容量が少なくとも発信装置(103)の寄生容量(110)の100倍である結合回路。 (もっと読む)

受信装置及び通信システム

【課題】伝送路上のノイズによるメイン処理の実行効率低下が発生することなく、且つ、CPUなどに通信処理のための外部割込ポートを必要としない受信装置及び通信システムを提供する。

【解決手段】CPU11が第1サンプリング部21及び第2サンプリング部22を備え、第1サンプリング部21及び第2サンプリング部22が、プリアンブルの各ビットのビット幅と同じサンプリング周期で、且つ、ビット幅の1/2の時間ずらしたタイミングで、入力ポート11aに入力される2値信号のサンプリングを行う。第1サンプリング部21又は第2サンプリング部22の少なくとも一方でプリアンブルを検出した場合に、CPU11がデータの受信を開始することができる。リモコン3及びUHF受信IC12等は、プリアンブルに係る誤差が許容範囲内となるようにCPU11へ信号を送信する。

(もっと読む)

信号受信装置及び信号処理方法

【課題】簡易な構成で、PPM信号を確実に再生するために正確にPPM信号をサンプリングできる信号受信装置を提供する。

【解決手段】パルス位置変調信号のうち検出対象区間から任意のHパルスの立ち上がりまたは立ち下がりエッジを開始点として設定する第1の設定手段と、前記検出対象区間における複数のHパルスの間隔に基づいてサンプリング周期を算出する算出手段と、前記検出対象区間について、前記開始点から前記サンプリング周期の倍数を基準点とし、前記基準点からの前記複数のHパルスの発生位置を検出する検出手段と、前記複数のHパルスの発生位置についてヒストグラムを生成する生成手段と、前記基準点に前記ヒストグラムでピークとなる値を加えた位置を前記パルス位置変調信号における再生対象信号区間のサンプリング点と決定する決定手段と、前記サンプリング点に基づいて前記再生対象信号区間を再生する再生手段とを有する。

(もっと読む)

1 - 10 / 56

[ Back to top ]