国際特許分類[H04L7/033]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | 受信機を送信機と同期させるための配置 (2,772) | 特殊な同期情報を含まない受信符号信号による速度または位相の制御 (674) | 受信信号の遷移を利用して同期信号発生手段の位相を制御するもの,例.位相ロックループを用いるもの (316)

国際特許分類[H04L7/033]に分類される特許

1 - 10 / 316

クロックデータ再生回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

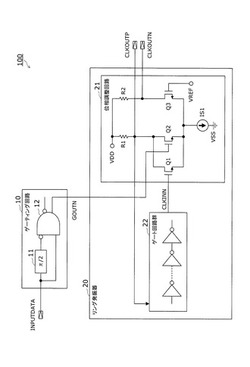

ゲーティッドVCO回路

【課題】ジッタやクロックデューティ比のずれが抑えられた良好なクロック成分を抽出する。

【解決手段】リング発振器20の位相調整回路21において、ゲート回路群22から出力された自走クロック信号CLKINNを入力とするMOSトランジスタQ1、およびゲーティング回路10からのゲーティング信号GOUTNを入力とするMOSトランジスタQ2の並列接続回路と、基準となるレファレンス電圧VREFを入力とするMOSトランジスタQ3とが差動対をなすCML回路を構成し、当該CML回路で得られた自走クロック信号CLKINNとゲーティング信号GOUTNとの論理和またはその反転論理をクロック出力信号CLKOUTとして出力する。

(もっと読む)

受信器PLL管理を伴う機敏なクロッキング

【課題】干渉を回避するためにクロック信号の周波数を変更する方法及び装置を提供する。

【解決手段】一実施形態において、第1のインターフェイスに搬送されるデータは、第1の周波数のクロック信号に同期される。信号は、別の周波数で第2のインターフェイスに搬送される。第2のインターフェイスに信号が搬送される周波数の変更に応答して、第1のインターフェイスに関連したクロックコントロールユニットが、第2の周波数へのクロック信号の変更を開始する。第2の周波数は、第2のインターフェイスに信号が搬送される周波数との干渉を生じないように選択される。クロック周波数の変更は、インターフェイスのクロックラインにおける擬似的アクティビティを防止するように遂行される。

(もっと読む)

半導体装置、受信機、送信機、送受信機及び通信システム

【課題】周波数誤差に基づく送信クロックを生成し、送信データに対して任意にSSCの適用が選択可能な半導体装置が、望まれる。

【解決手段】半導体装置は、受信信号を入力し、動作クロック信号に基づいて受信信号からクロック信号とデータ信号を取り出すクロックアンドデータリカバリ部と、受信信号から取り出したクロック信号と動作クロック信号との周波数誤差信号を求める周波数誤差調整部と、周波数誤差信号を記憶する周波数誤差信号記憶部と、周波数誤差信号に基づいて動作クロック信号の周波数を制御する動作クロック生成部と、周波数誤差信号記憶部が記憶する周波数誤差信号の値に基づいて、動作クロック生成部が生成する動作クロック信号をスペクトラム拡散させて変動させるSSCG部と、を備えている。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】ゲーティング回路と、再生クロックを出力する第1の発振回路と、第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に周波数制御信号Aと回路間ばらつき調整信号C1の加算信号を入力し、ゲーティング回路の制御端子に周波数制御信号Aと回路間ばらつき調整信号C2の加算信号を入力する構成である。

(もっと読む)

PONシステムの宅側装置、信号処理回路及び同期維持方法

【課題】 光トランシーバのスリープ時間の経過後に即座に通信を開始できる信号処理回路を提供する。

【解決手段】 本発明の信号処理回路は、光トランシーバ21から入力された受信信号からクロックと受信データを再生し、再生された受信データを上位層側に出力する受信側処理部33,34と、上位層側から入力された送信データを再生されたクロックと同期する送信信号として光トランシーバ21に出力する送信側処理部31,32とを備える。また、本発明の信号処理回路は、光トランシーバ21の機能を低下させるスリープ動作を行う場合に、既に再生されたクロックをスリープ時間中において保持し、かつ、スリープ時間の終了とともにクロックの保持を解除する同期維持モードを実行する制御部27を備える。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

1 - 10 / 316

[ Back to top ]