株式会社東芝により出願された特許

191 - 200 / 54,554

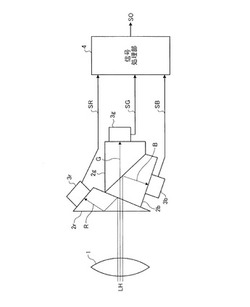

固体撮像装置

【課題】固体撮像装置の感度の低下を抑制しつつ、混色を低減させる。

【解決手段】赤色用イメージセンサ3rの光電変換部12rは、青色用イメージセンサ3bの光電変換部12bおよび緑色用イメージセンサ3gの光電変換部12gに対して光入射面から深い位置に配置する。

(もっと読む)

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

配線及び半導体装置

【課題】実施形態は、多層グラフェンの配線及び多層グラフェン配線を有する半導体装置を提供することを目的とする。

【解決手段】実施形態にかかる配線は、基板と、基板上に設けられた金属膜と、記金属膜上に設けられた金属部と、金属部に形成されたグラフェン配線とを有し、前記グラフェン配線は、前記金属膜と電気的に接続し、金属膜と金属部は、異なる金属または合金であることを特徴とする。

(もっと読む)

テンプレートの表面処理方法及び装置

【課題】テンプレート表面に充填性と離型性を両立した離型層を形成する。

【解決手段】本実施形態では、インプリント処理時に光硬化性樹脂に接触させる凹凸を有するパターン面を備えたテンプレートの表面処理を行う。この表面処理方法は、テンプレート1のパターン面に第1シランカップリング剤を供給する工程と、テンプレート1のパターン面に第2シランカップリング剤を供給する工程と、を備えている。第1シランカップリング剤を使用してテンプレート表面に形成する離型層は、第2シランカップリング剤を使用してテンプレート表面に形成する離型層と比較して、前記光硬化性樹脂に対する接触角及び水に対する接触角が低い。

(もっと読む)

パターン形成方法

【課題】塗布された反転材の段差を小さくし、反転マスクプロセスにより所望のパターンを形成する。

【解決手段】本実施形態によれば、パターン形成方法は、被加工膜上の第1領域に第1パターンを形成する工程と、前記第1パターンを覆うように前記被加工膜上に感光性化合物を有する反転材膜を形成する工程と、前記反転材膜を露光及び現像し、前記被加工膜上の前記第1領域とは異なる第2領域において、前記反転材膜を第2パターンに加工する工程と、前記反転材膜を露光及び現像した後、前記第1パターンの上面が露出するように前記反転材膜をエッチバックし、前記第1領域において前記反転材膜を第3パターンに加工する工程と、前記第2パターン及び前記第3パターンをマスクとして前記被加工膜をエッチングする工程と、を備える。

(もっと読む)

電力用半導体装置およびその製造方法

【課題】フィールドプレート電極を有するトレンチゲート構造を備えた電力用半導体装置においてゲート−ソース間容量を低減する。

【解決手段】電力用半導体装置は、第1導電形の第1の半導体層2、フィールド絶縁膜6、フィールドプレート電極7、第1の絶縁膜8、導電体9、第2の絶縁膜11、ゲート絶縁膜10、及びゲート電極12を備える。フィールドプレート電極7は、フィールド絶縁膜6を介して第1の半導体層2のトレンチ5内に設けられる。第1の絶縁膜8は、フィールドプレート電極7上に設けられ、フィールド絶縁膜6とともにフィールドプレート電極7を取り囲む。導電体9は、第1の絶縁膜8上に設けられ、フィールドプレート電極7とは絶縁される。ゲート電極12は、フィールド絶縁膜6の上端上に設けられ第2の絶縁膜11を介して導電体に隣接し、ゲート絶縁膜10を介してトレンチ5内に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

分子メモリ装置の製造方法

【課題】メモリ素子の状態が良好なクロスポイント構造の分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む配線層を形成する工程と、前記配線層上に犠牲膜を形成する工程と、前記犠牲膜上に第2方向に延びる複数本の第1絶縁部材を形成する工程と、前記第1絶縁部材の側面上に前記第1配線とは異なる導電材料からなる第2配線を形成すると共に、前記犠牲膜における隣り合う前記第1絶縁部材間であって前記第2配線間の直下域に相当する部分を除去する工程と、隣り合う前記第1絶縁部材間であって前記第2配線間に複数本の第2絶縁部材を前記配線層に接するように形成する工程と、前記犠牲膜を除去することによりギャップを形成する工程と、前記ギャップ内に、前記第1配線及び前記第2配線のうちの一方に結合し他方には結合しない分子材料を形成する工程と、を備える。

(もっと読む)

191 - 200 / 54,554

[ Back to top ]