NECマイクロシステム株式会社により出願された特許

41 - 50 / 72

乗算剰余演算器及び情報処理装置

【課題】 回路規模を増大させることなく、演算時間を短縮できる乗算剰余演算器及び情報処理装置を提供する。

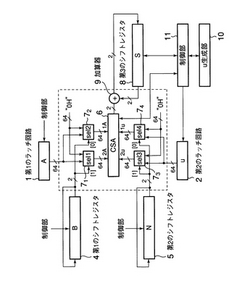

【解決手段】 S=S+A×B+u×Nを算出するための乗算剰余演算器であって、複数のビット数q単位で供給される乗数Bの値に応じて被乗数Aまたは0の値を切換えて出力し、ビット数q単位で供給される乗数Nの値に応じて被乗数uまたは0の値を切換えて出力するセレクタと、セレクタから順次出力される値を用いてA×B+u×Nの演算を実行する桁上げ保存加算器と、桁上げ保存加算器からビット数q単位で出力されるA×B+u×Nの演算結果とビット数q単位で供給される過去の該演算結果とを加算し、該加算結果を乗算剰余演算結果Sとして出力する加算器とを有する構成とする。

(もっと読む)

乗算剰余演算器及び情報処理装置

【課題】 回路規模を増大させることなく、演算時間を短縮できる乗算剰余演算器及び情報処理装置を提供する。

【解決手段】 S=S+A×B+u×Nを算出するための乗算剰余演算器であって、複数のビット数q単位で供給される乗数B、Nの値をBooth法に基づいて変換し、該変換後のBに対応する被乗数Aの整数倍の値を選択して出力し、該変換後のNに対応する被乗数uの整数倍の値を選択して出力する論理回路と、論理回路から順次出力される値を用いてA×B+u×Nの演算を実行する桁上げ保存加算器と、桁上げ保存加算器からビット数q単位で出力されるA×B+u×Nの演算結果とビット数q単位で供給される過去の該演算結果とを加算し、該加算結果を乗算剰余演算結果Sとして出力する加算器とを有する構成とする。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

映像再生制御システム

【課題】

情報の欠落を防ぎユーザの快適な視聴を妨げない映像再生制御システムを提供すること。

【解決手段】

本発明にかかる文字情報の表示方法は、映像情報に多重化されている文字情報のデコード開始を決定するステップと、文字情報のデコードを開始するステップと、デコードされた文字情報の表示開始を決定するステップと、デコードされた文字情報を表示するステップと、映像情報の音声出力の消音を決定するステップと、映像情報の音声出力を消音するステップと、映像情報とは異なる第2の情報の音声を出力するステップとを有するものである。

(もっと読む)

パルス幅変調回路

【課題】

高速、高精度の動作を実現できるパルス幅変調回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路では多相クロック生成回路2によって基準クロックに基づき多相クロック信号を生成する。そして、入力データと、多相クロック生成回路2によって生成された多相クロック信号とに基づいてパルス幅変調信号を生成する。ここで、多相クロック生成回路2は、位相ロックループ回路を有し、位相ロックループ回路によって生成された中間クロック信号をさらに位相補間することにより多相クロック信号を生成する。

(もっと読む)

半導体記憶装置テスト回路

【課題】

ヒューズ切断の良否を容易に判断することができ、ペレットの増大を招かない半導体記憶回路およびその半導体記憶装置のテスト回路を提供することを目的とする。

【解決手段】

本発明にかかる半導体記憶装置テスト回路は、メモリセルの各信号線に対して切断信号Enを保持するヒューズ制御回路300と、切断結果信号Fnを出力するヒューズラッチ回路6と、複数のメモリセルの信号線に渡って切断信号Enと当該切断信号Enに対する切断結果信号Fnとを比較演算して各アドレス信号線の切断判定信号を生成し、複数に渡る切断判定信号の値が実質的に同一であれば、複数のメモリセルに設けられた各ヒューズが期待通りに処理されたことを表す期待値信号FOUTを出力し、切断判定信号の値が少なくとも一つでも異なる場合は期待値信号の反転信号を出力する判定回路403とを有するものである。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】 機能マクロの電源接続構造に関わらず、機能マクロを回転配置してもマクロ内電源接続端とチップレベル電源配線との接続を可能としたLSIのレイアウト設計方法を提供する。

【解決手段】 回路接続情報に基づいて、機能マクロを含む所定の素子パターンをチップ領域上の所定位置に配置する第1工程P1と、第1電源配線レイアウト情報を生成する第2工程P2と、同電位電源接続端及び同電位電源配線の有無を調べる第3工程P3と、同電位電源接続端及び同電位電源配線のレイアウト情報を抽出する第4工程P4と、第1接続孔レイアウト情報を生成する第5工程P5と、電源開放端の有無を調べる第6工程P6と、全ての電源開放端のレイアウト情報を抽出する第7工程P7と、電源開放端を所望のチップレベル電源配線に接続するための修正レイアウト情報を生成する第8工程P8とを含む。

(もっと読む)

レイアウト方法

【課題】半導体集積回路上に配置される複数の配線のクロストークノイズの影響を極力無くすレイアウト方法提供する。

【解決手段】配線毎にクロストークノイズを発生する時刻および期間を計算する第1の計算工程と、配線毎に前記クロストークノイズが禁止される時刻および期間を計算する第2の計算工程と、配線毎にクロストークノイズを発生する時刻および期間とクロストークノイズが禁止される時刻および期間とを比較する時刻・期間比較工程と、比較工程で、クロストークノイズを発生する時刻および期間とクロストークノイズが禁止される時刻および期間に重なりがない場合は、配線を隣接配線として配置する配線配置工程とを備えるレイアウト方法。

(もっと読む)

同期式回路のレイアウト設計方法

【課題】タイミング制約ある素子を最適に配置し、配線長を短くでき、かつ後工程の配線工程でCADツールの負担を軽くし、迂回配線の可能性の低減をし、配線によるクロストークノイズの影響を低減し、配線の信頼性悪化を防ぐ。

【解決手段】タイミング制約のある同期式半導体集積回路の自動レイアウト設計方法において、タイミング制約が付与された経路の素子から分岐配線を抽出し(S1)この分岐配線の分岐点に分岐バッファを挿入し(S3)前記経路で与えられたタイミング制約値より始点素子から終点素子までの配線の遅延値のみを求めてから前記各素子の配線長とその総和を求め(S4)前記総配線長の範囲内に前記始点素子と前記終点素子を優先配置し、前記経路で与えられ前記始点素子から前記終点素子の間にある中間素子の配置を、前記各素子の出力抵抗とその配線抵抗との大きさの比較により判定して最適配置する(S8,S9 )ことを特徴とする。

(もっと読む)

パルス幅制御回路

41 - 50 / 72

[ Back to top ]